## eRD109 update: dRICH RDO

Pietro Antonioli, Davide Falchieri, Sandro Geminiani, Giovanni Torromeo on behalf of the INFN Bologna RDO team

EPIC Electronics & DAQ WG meeting 08 May 2025

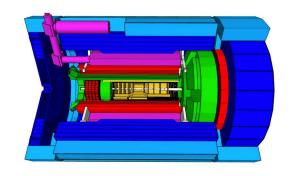

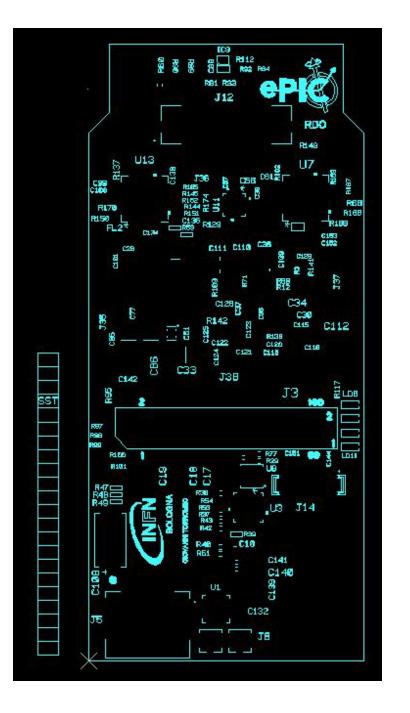

### **Towards RDO final layout**

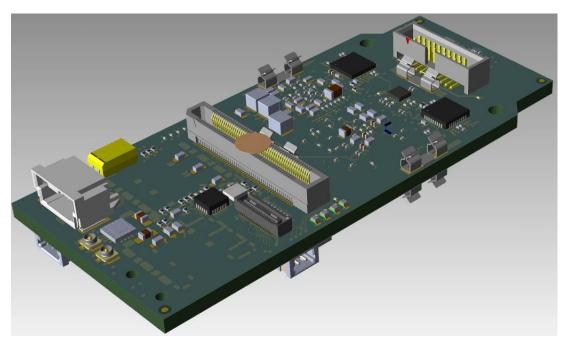

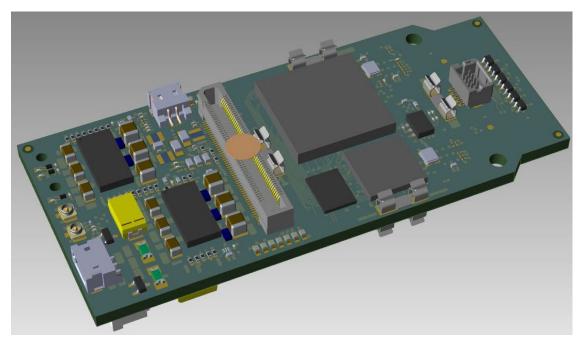

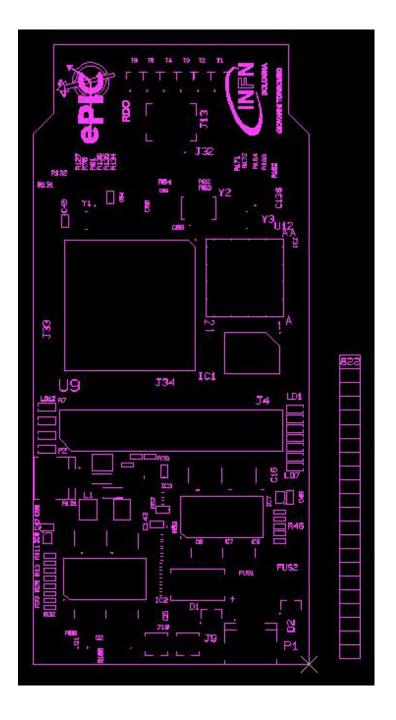

TOP

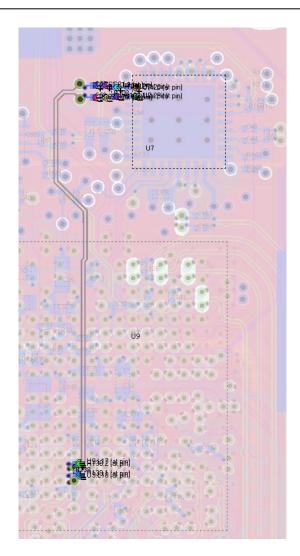

News: the PCB layout has been finalized and the PCB fabrication has been launched on Tuesday 06 May 2025

we expect 12 PCBs (of which 10 populated) in 5 weeks: first half of June 2025

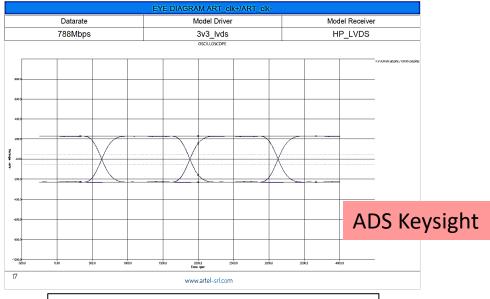

# 4 Channels TX ARTIX Ultrascale+ GTH to VTRX+ receiver AC coupling termination 100 $\Omega$ dielectric FR408HR

**ADS Keysight**

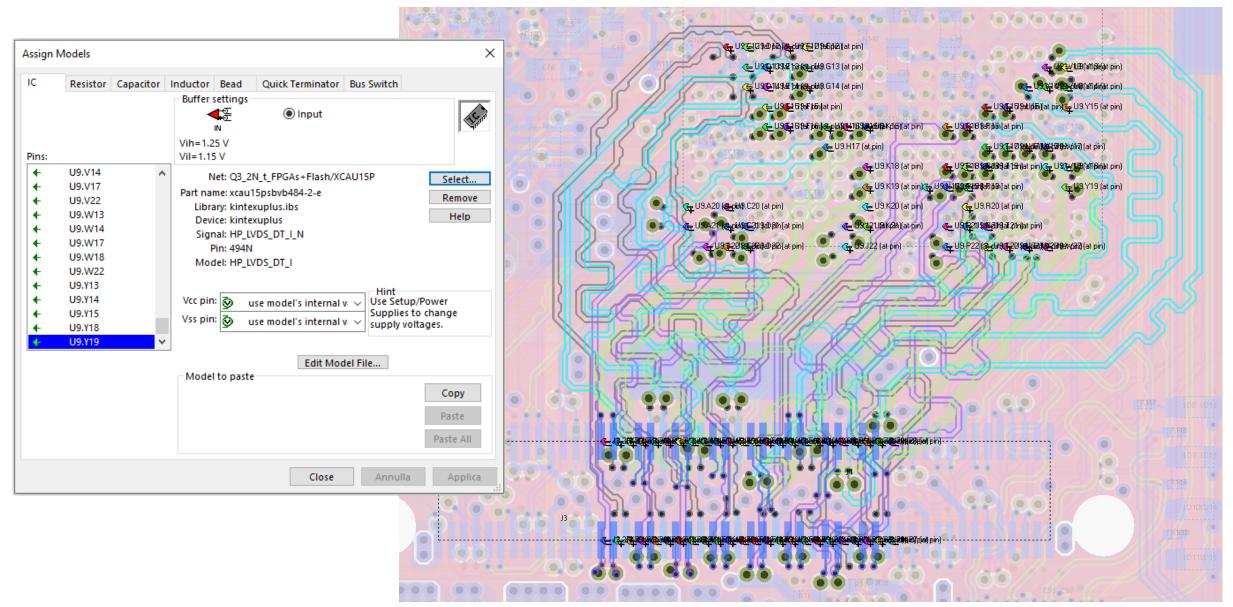

#### Routing of 32 lanes ALCOR bus

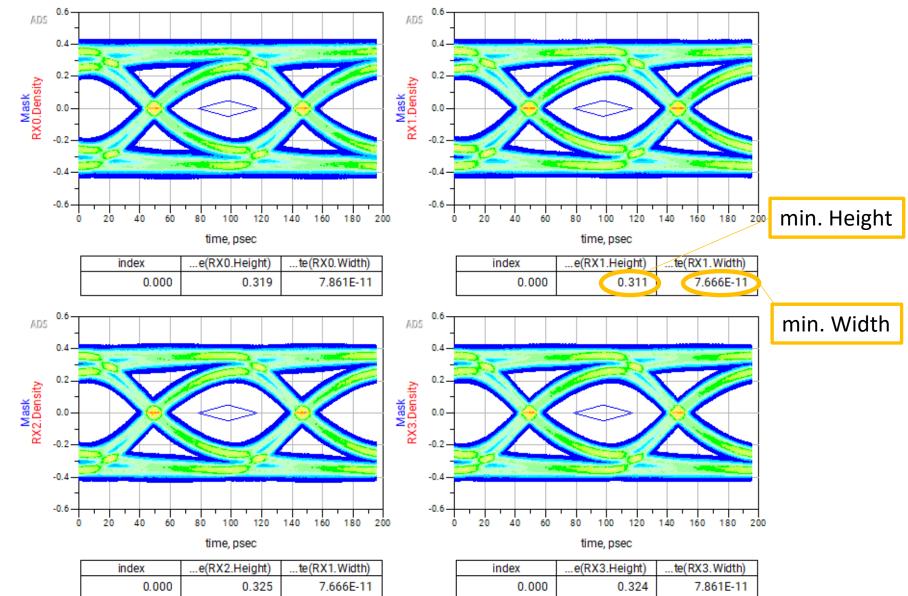

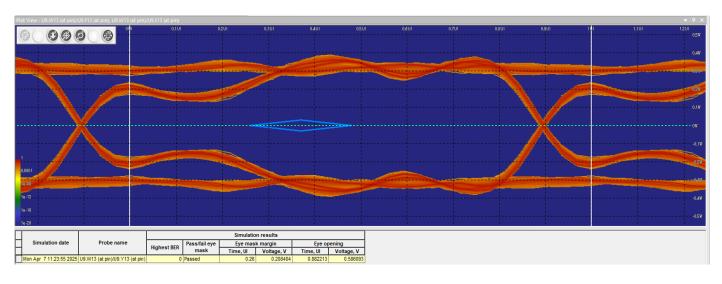

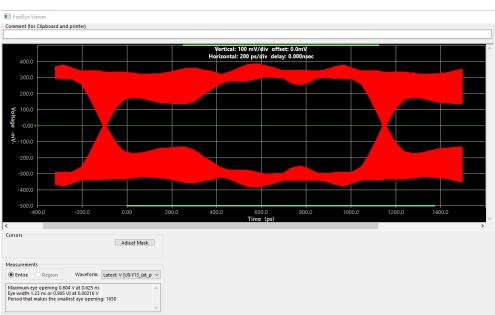

#### ALCOR Q0\_1b lane simulation @800MHz (UI=1.25ns)

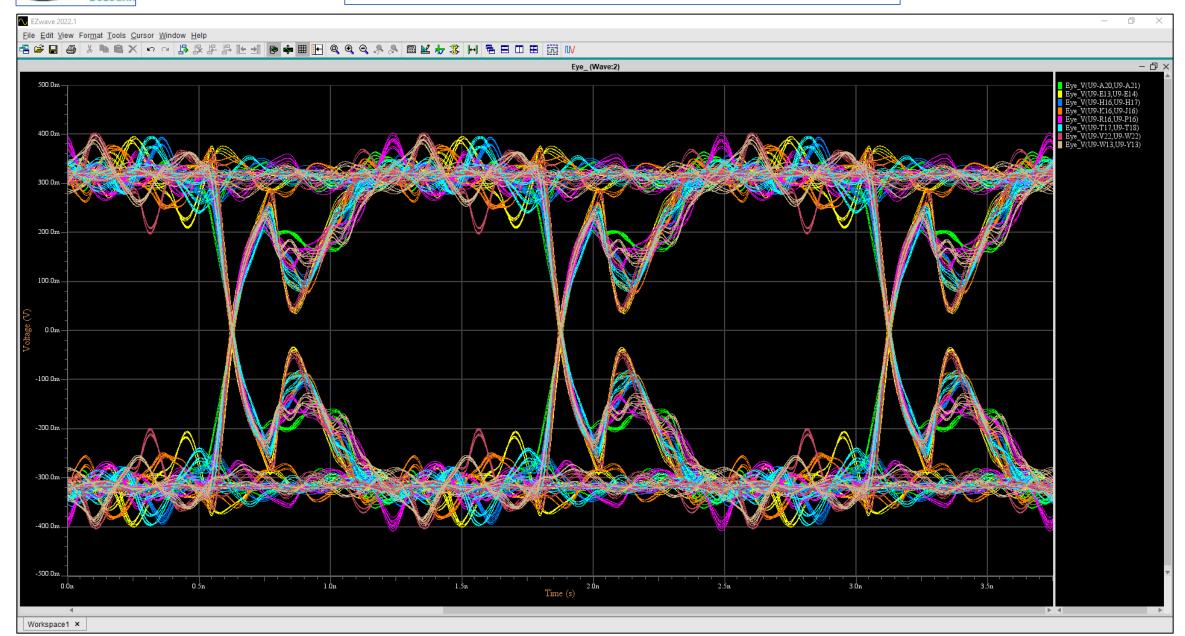

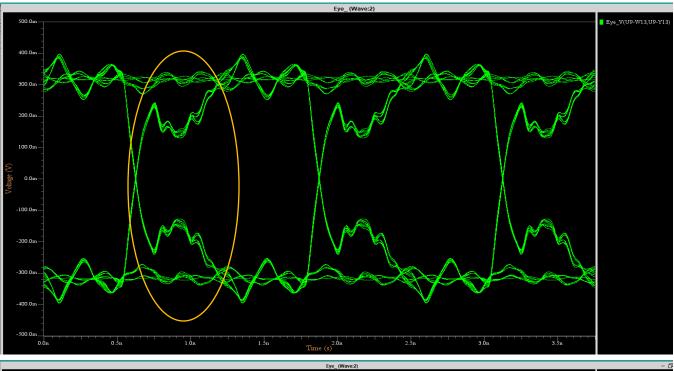

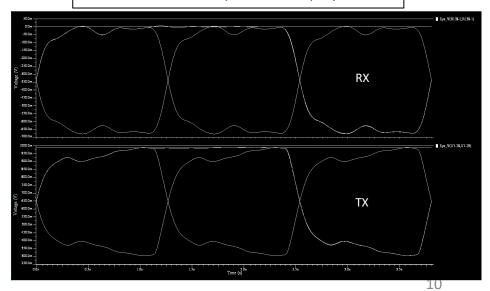

#### 8 stacked eyes of ALCOR BUS lanes (Q0\_xt,Q0xb)

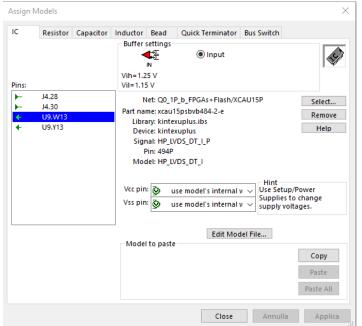

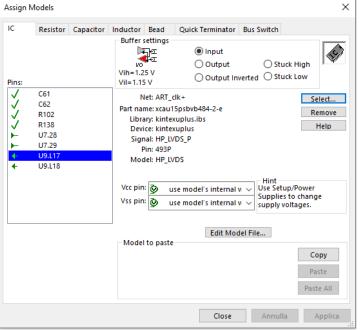

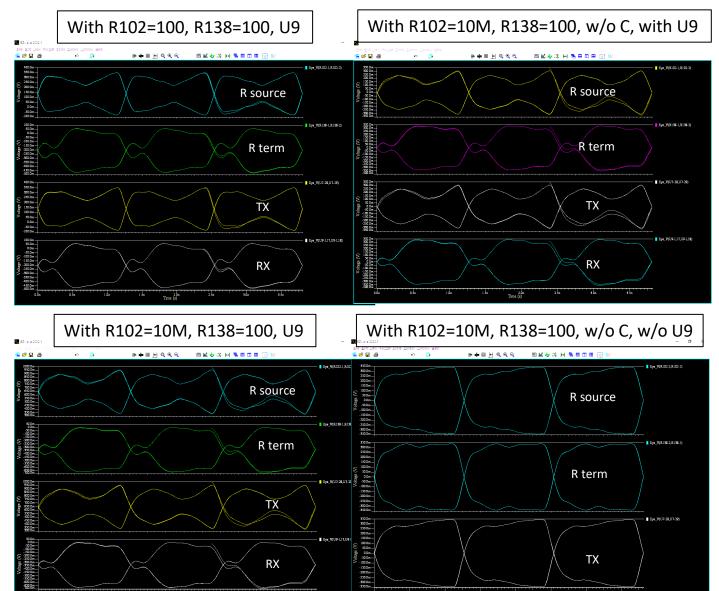

Differential probe on **ARTIX pins** receiving one lane of the **ALCOR bus @800MHz (1.25ns)** (IBIS model kintexuplus.ibs)

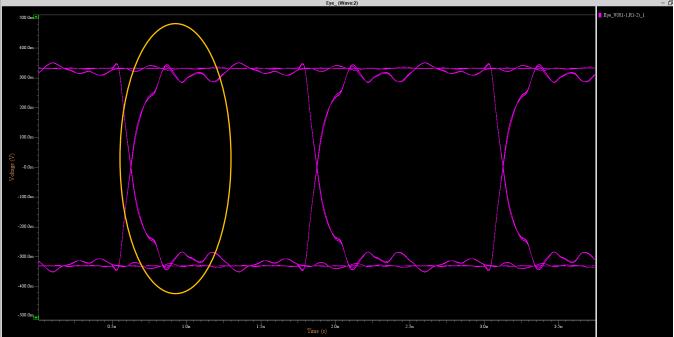

Differential probe on 100 ohm resistor that replaces the ARTIX pins receiving one lane of the ALCOR bus @800MHz (1.25ns)

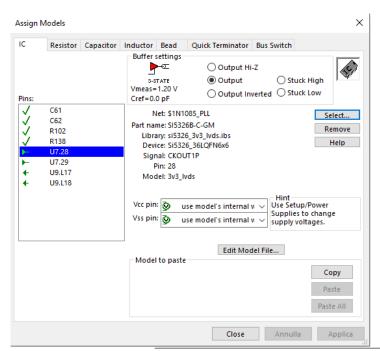

- ART\_clk+/ART\_clk-

- 394MHz

- Driver: U7/28,29 IBIS model: Si5326\_3v3\_lvds.ibs

- Receiver: U9/L17,L18 IBIS model: kintexuplus.ibs

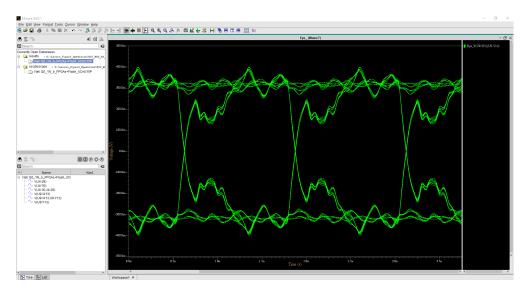

#### ART\_clk+/ART\_clk- 394MHz

#### With R102=10M, R138=100, w/o U9

#### Firmware design: Artix – Alcor interface

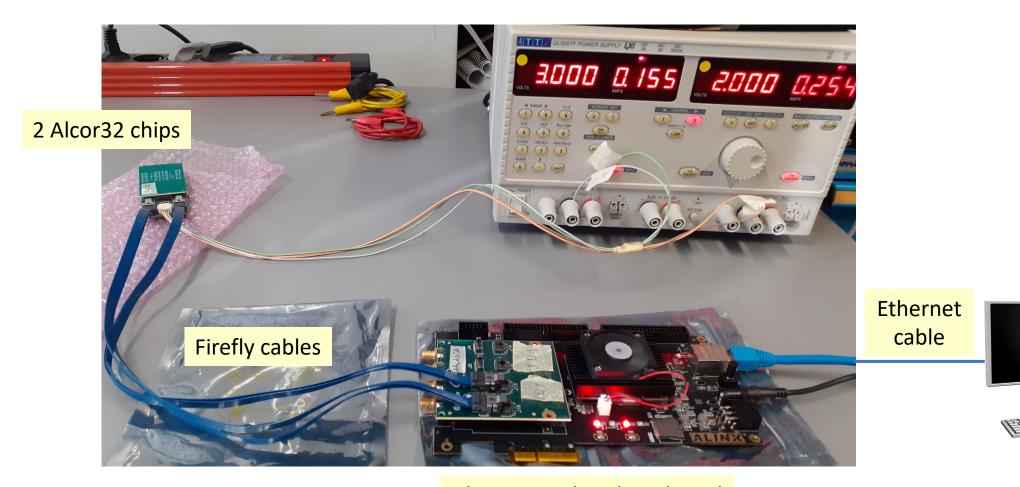

Alinx + FMC breakout board

In order to test the Artix – Alcor interface, we implemented the IPbus firmware on the FPGA. Now we can program the Alcor registers via SPI and we can correctly receive the data

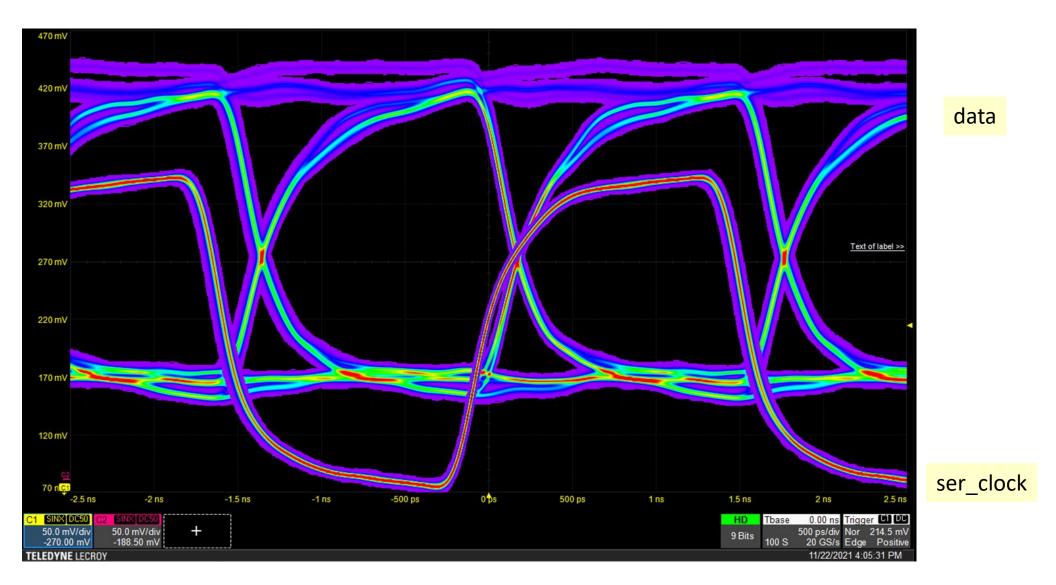

#### **Artix – Alcor interface: data decoding tests**

```

Programming 0

----- ALCOR # 0 Complete Setup

KC705 mode set to config

Resetting fifos for ALCOR # 0

Alcor reset and lanes alignment

[AlcorLib] Loading conf from /home/eic/alcor/alcor-utils/conf

----- Setup chip # 0 -----

Lane # : 0 8bit-align

OK 32bit-align

OK

Lane # : 1 8bit-align

OK 32bit-align

OK

OK 32bit-align

Lane # : 2 8bit-align

OK

Lane # : 3 8bit-align

OK 32bit-align

OK

Enabled lanes for readout 0xf

Setting Alcor registers to default

Setting ECCR to: 0xb01b

Executing custom BCR setup

Loading BCR file /au/pdu/conf/bcr/standard.bcr for chip # 0 ....

Loaded configuration for 8 Bias Control Registers

Executing custom PCR setup (channel ON/OFF driven by PCR file & mask)

Loading PCR file /au/pdu/conf/pcr/maxthreshold.pcr for chip # 0 Mask 4294967295 ....

Loaded specific configuration for 32 channels

Sending test pulse to reset pixel logic

----- End of configuration

kc705-192 chip-0 lane-0: 320014684 Hz

kc705-192 chip-0 lane-1: 319977680 Hz

kc705-192 chip-0 lane-2: 320308341 Hz

kc705-192 chip-0 lane-3: 320462234 Hz

```

#### Firmware design

AXAU15 FPGA Dev Board & Kit with AMD Artix US+ XCAU15P

This commercial board hosts the same FPGA as the RDO (AU15P), but with a different package: we are using it to perform firmware design and test before the first RDO board is available

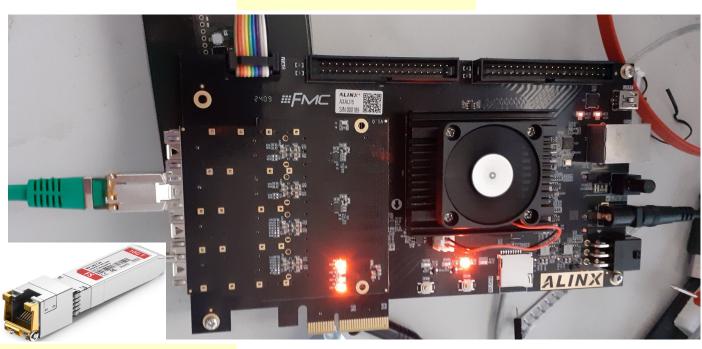

### Firmware design: Artix – SFP interface

from February 2025 meeting

Alinx + FMC SFP board

Ethernet cable

GBIC SFP with RJ45 connector

In order to mimic the Artix – VTRx+ interface, we implemented the IPbus firmware on the FPGA and tested it

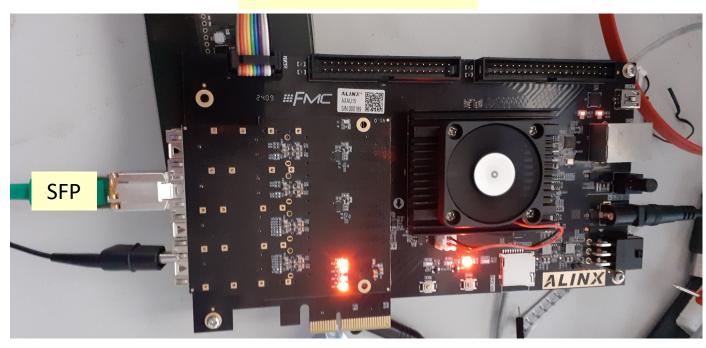

### Firmware design: Artix – SFP interface

now working on

Alinx + FMC SFP board

optical cable

The goal is to have a working IPbus firmware on the FPGA working over optical fiber

#### **Next steps**

- learn as much as we can from the Alinx board until the RDO is available

- prepare a firmware for the RDO board to start the tests as soon as the board is ready

## Thanks!

## **Backup**

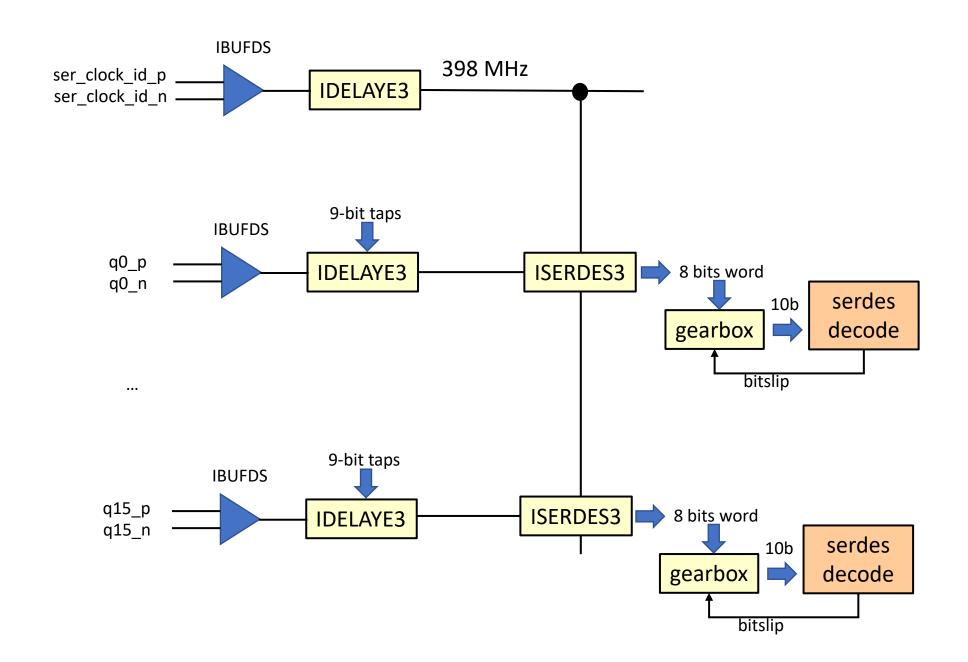

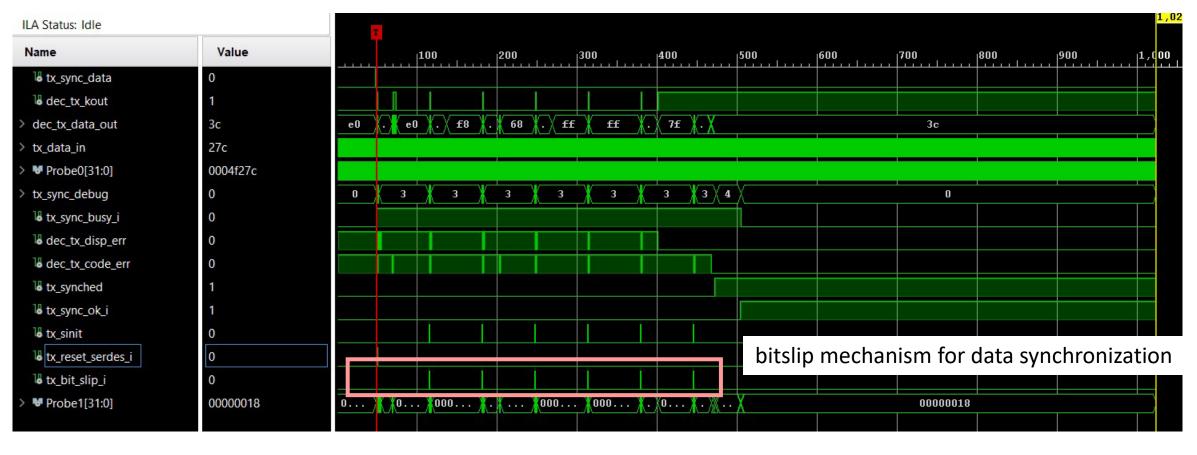

Average tap delay @ 300 MHz = 2 ps, 512 taps available for a total span of  $^{\sim}1.1$  ns The tap value is chosen via SW, then the sync procedure is run (bitslip mechanism)

### **Artix – Alcor interface: data decoding tests**

| ILA Status: Idle         |          |          |     | T        |          |          |          |          |          |                    |       |          |

|--------------------------|----------|----------|-----|----------|----------|----------|----------|----------|----------|--------------------|-------|----------|

| Name                     | Value    | 480      | 500 | 520      | 540      | 560      | 580      | 600      | 620      | 640                | 660   | 680      |

| > <b>*</b> tx_word[31:0] | bcbcbcbc | behebebe |     | 5c5c5c5c | 7e7e7e7e | 0c000000 | 08000000 | 04000000 | 00000000 | 0000   2000000   2 |       | 24000000 |

| tx_new_word              | 0        |          |     |          |          |          |          |          |          |                    |       |          |

| lane_enabled             | 1        |          |     |          |          |          |          | 111      |          |                    |       | 10       |

| > tx_data_out            | bc       | bc       | 5c  | 7c       | 00 (.)   | 00 (.    | 00 .     | 00       | (.)      | 00 \.              | 00 (. | 00 .     |

| > tx_k_code              | f        |          |     | f        |          | X        |          |          |          | 0                  |       |          |