# Sensor and AncASIC Update

Iain Sedgwick

UK WP1 F2F Meeting June 26<sup>th</sup> 2025

### Introduction

#### **SVT Silicon Scheme**

- Plans

- Why AncASIC?

### **MOSAIX** and **EIC-LAS** Update

ER1: MOSS

**ER2: MOSAIX**

### **AncASIC Update**

- Technology

- Chips Submitted

- **Future Plans**

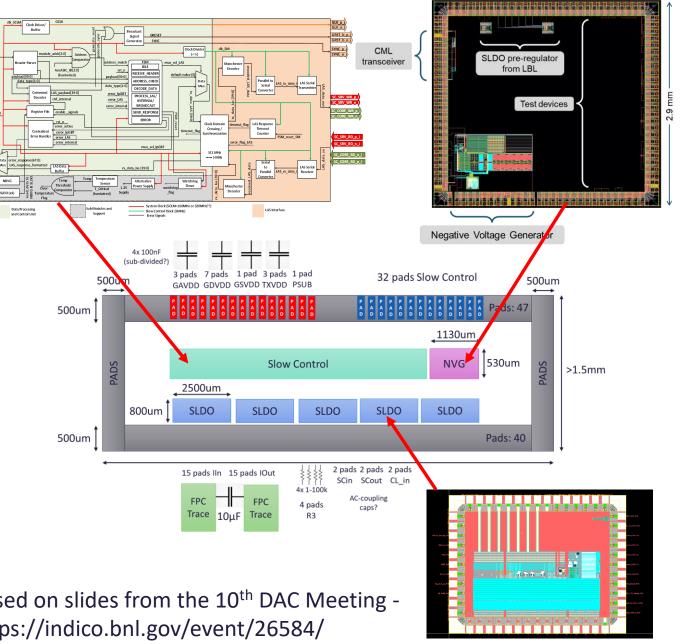

Based on slides from the 10<sup>th</sup> DAC Meeting https://indico.bnl.gov/event/26584/

# **SVT Silicon Scheme**

### Introduction SVT Silicon Scheme

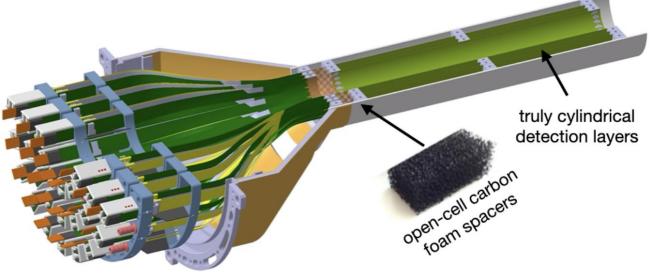

# Inner Barrel (IB) Outer Barrel (OB) Electron and Hadron Endcap Disks (EE, HE)

### **Inner Barrel**

- Thinned silicon bent around beampipe

- Use wafer-scale MOSAIX from ITS3

### **Outer Barrel and Discs**

- Smaller Version of MOSAIX with minimum necessary changes (EIC-LAS)

- Supporting AncASIC

# **Ancillary ASIC**

### Why AncASIC?

- Some MOSAIX/LAS features require adaptation to stave/disc operation:

- Point-to-point slow control

- Point-to-point powering

- Precise negative back bias

- May be technically unfeasible to integrate these features in the LAS

- Limited prototyping

- MOSAIX schedule is an external dependency

- For these reasons, develop supporting ASIC instead

https://ep-news.web.cern.ch/content/alice-its3-clears-major-milestone

MOSAIX

# **Ancillary ASIC**

### Why AncASIC?

- Some MOSAIX/LAS features require adaptation to stave/disc operation:

- Point-to-point slow control

- Point-to-point powering

- Precise negative sensor bias

- May be technically unfeasible to integrate these features in the LAS

- Limited prototyping

- MOSAIX schedule is an external dependency.

- For these reasons, develop supporting ASIC instead

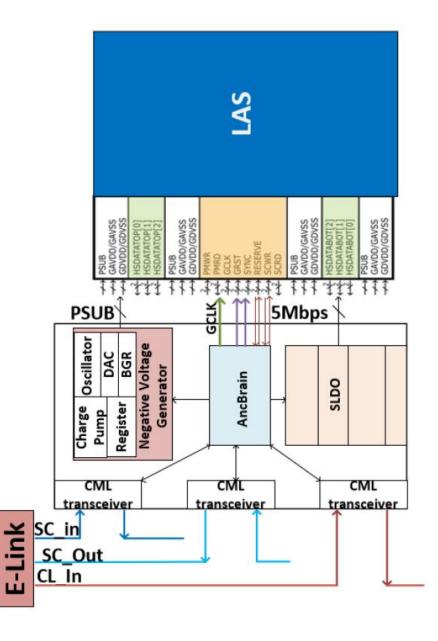

Serialised Slow Control interface from EIC-LAS to lpGBT

SLDO for serial powering

Local Negative Voltage Generator

- Develop independent supporting chip

- Development decoupled from MOSAIX availability

- No modification of MOSAIX needed

- 110nm XFAB process

- 4 MPW runs a year

- Cost effective

# **Ancillary ASIC**

### Why AncASIC?

- Some MOSAIX/LAS features require adaptation to stave/disc operation:

- Point-to-point slow control

- Point-to-point powering

- Precise negative back bias

- May be technically unfeasible to integrate these features in the LAS

- Limited prototyping

- MOSAIX schedule is an external dependency

- For these reasons, develop supporting ASIC instead

# MOSAIX and EIC-LAS Update

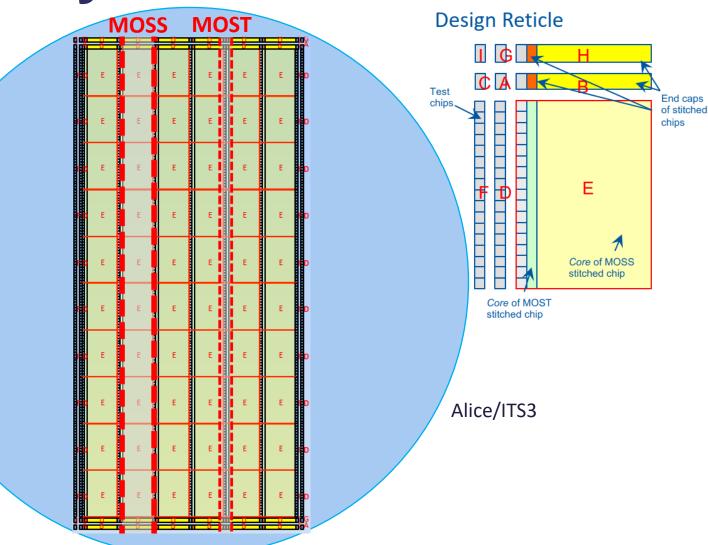

# **ER1: MOSS and babyMOSS**

- Main objective: Learn and prove stitching

- Two large stitched sensor chips (MOSS, MOST)

- Different approaches for resilience to manufacturing faults

- Small test chips (Pixel Prototypes)

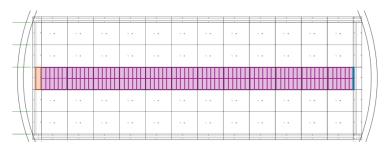

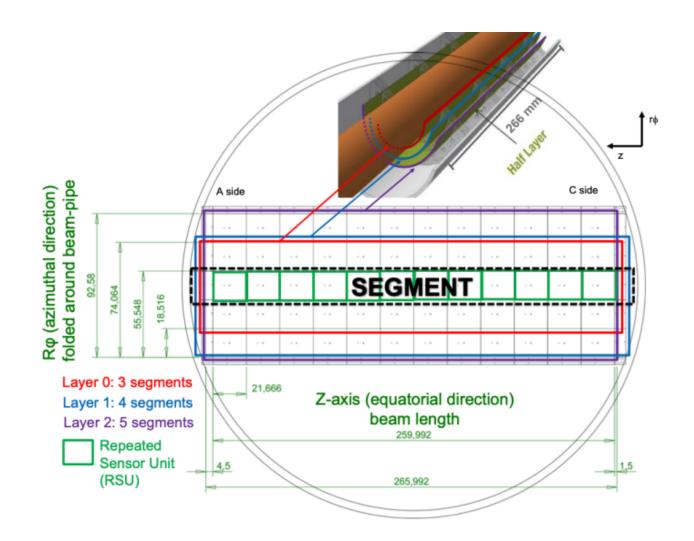

# **ER2: MOSAIX**

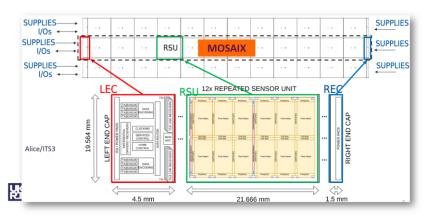

- MOSAIX is a full feature prototype of the sensor for ALICE ITS3

- Wafer scale sensor design using the stitching technique

- Process: TPSCo 65 nm CMOS Imaging Sensors(customized)

- MOSAIX design leading to production sensor (ER3)

# **ER2: MOSAIX**

# **MOSAIX: Status and Outlook**

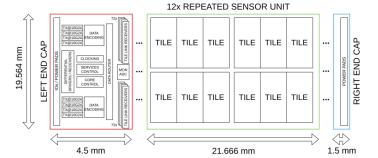

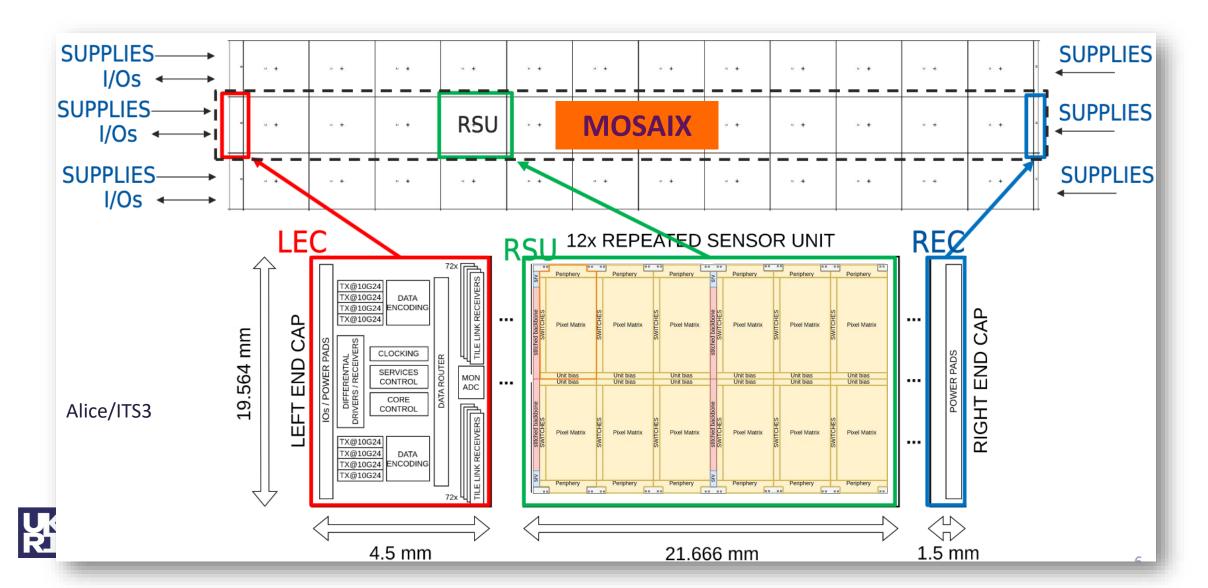

### **RSU, LEC, MOSAIX**

- All components and top level now designed and implemented.

- DOING: refinements of Quality of Results (QoR), powering signoff and polishing of physical integrity.

- Verification

- Functional verification on RTL models completed.

- DONE: complete signoff reviews of simulations of SBB and MOSAIX powering transients.

- DOING: verification with GLN models, SEU simulations, power aware simulations.

- Physical Rules on full wafer gds in very good state

# **MOSAIX to EIC-LAS**

### **MOSAIX to EIC-LAS**

#### **Inner Barrel**

MOSAIX segment

- 12 RSUs

- 8 data links

- 7 slow control links

- Direct powering

Improve yield and coverage

Lower material budget

Lower material budget, fit integration requirements

Lower material budget, fit integration requirements

### **Outer Barrel, E/H Endcaps**

EIC-LAS and ancillary chip

- 5 or 6 RSUs

- Single data link

- Multiplex slow control

- Serial powering

EIC-LAS

Ancillary ASIC

# **MOSAIX:** Power

### Only goes one way...

- Some (all?) of the latest MOSAIX power numbers for the LEC exceed our estimates

- Our previous power number for the LEC was 411mW typ and 570mW in max

### Summary: MOSAIX Power

#### ITS3 TDR Table 3.10

|                     | Power density<br>[mW cm <sup>-2</sup> ] |                                |             |  |

|---------------------|-----------------------------------------|--------------------------------|-------------|--|

|                     | Expected<br>25 °C                       | $^{\rm Max}_{\rm 25^{\circ}C}$ | Max<br>45°C |  |

| Left end cap (LEC)  |                                         | 791                            |             |  |

| Active area (RSU)   | 28                                      | 44                             | 62          |  |

| Pixel matrix        | 15                                      | 32                             | 51          |  |

| Biasing             | 168                                     | 168                            | 168         |  |

| Readout peripheries | 432                                     | 457                            | 496         |  |

| Data backbone       | 719                                     | 719                            | 719         |  |

| Impact on EIC-LAS                                                                                       |

|---------------------------------------------------------------------------------------------------------|

| The foreseen modifications on LEC will reduce this power / potential issue                              |

| No changes foreseen for the<br>RSU. However, MOSAIX-<br>RSU power is expected to<br>perform as planned. |

Final numbers can only be provided after MOSAIX has been tested, which is expected in early 2026.

#### LEC Power post implementation

|               | LEC Power<br>[mW] |      | LEC Power Density<br>[mW/cm^2] |      |

|---------------|-------------------|------|--------------------------------|------|

| Scenario      | Тур               | Max  | Тур                            | Max  |

| 3 x 10 Gbit/s | 697               | 904  | 792                            | 1027 |

| 6 x 5 Gbit/s  | 1043              | 1358 | 1185                           | 1543 |

LEC Area 0.88 [cm^2]

#### **RSU Power post implementation**

|                | Power [mW] |        | Power density<br>[mW/cm2] |

|----------------|------------|--------|---------------------------|

|                | Typ N      | 1ax    | Typ Max                   |

| Matrix (12)    | 45.36      | 89.71  | 11.5 22.8                 |

| Biasing Unit   |            |        |                           |

| (12)           | 4.32       | 4.32   | 168.0 168.0               |

| Periphery (12) | 74.88      | 84.96  | 434.4 492.9               |

| SBB Unit (4)   | 14.40      | 14.40  | 1200.0 1200.0             |

| RSU Total      | 138.96     | 193.39 | 32.8 45.6                 |

10th EIC DAC Meeting João de Melo 14

# **MOSAIX** Power

### So what does that mean?

Our previous power number (based on the MOSAIX Engineering Review) for the LEC was 411mW typ and 570mW in max

| Condition              | Typ Power (mW) | Max Power (mW) |

|------------------------|----------------|----------------|

| Our previous estimate  | 411            | 570            |

| Latest MOSAIX (3x 10G) | 697            | 904            |

| Latest MOSAIX (6x 5G)  | 1043           | 1358           |

| Latest MOSAIX (1x 5G)  | 391            | 493            |

- So if we can reduce to 1 5G link, we will be around our original estimate.

- But this is just my first attempt to integrate these values

- Need to re-simulate

- Does the expected data imply 1 link is OK? Who is simulating this?

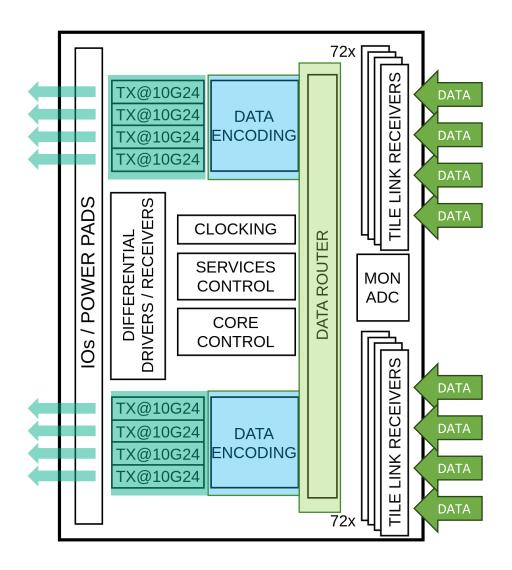

### **MOSAIX to EIC-LAS: LEC Modifications**

### Reduce LEC to one channel

- Bypass Serializer LDOs

- Study on the performance before and after removing LDOs.

- Dedicated decap cells, star routing (supply), and functional adjustments (no LDO controls).

- Data Encoding and Router (serialization of the data to a single channel)

- Challenge to adapt/change

- Slow control needs to be modified

# **AncASIC Update**

# **Technology Selection**

### XFAB XT011

- 110nm BCD-on-SOI Technology

- SOI permits floating grounds for negative voltage generation

- Thick copper top layer very low resistance for power dissipation

- High gate density suitable for AncBrain

- All design sites have experience with XFAB

- Radiation hardness untested

- ePIC radiation requirement low [1]

- Derived from a previously tested technology [2]

- Test structures in fabrication

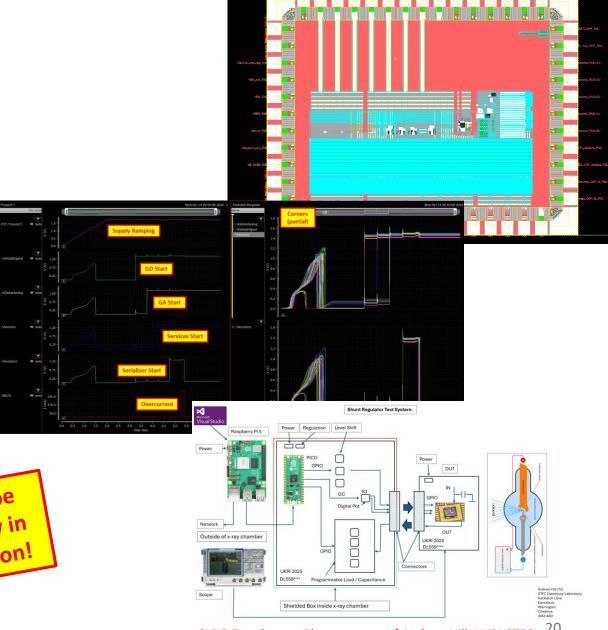

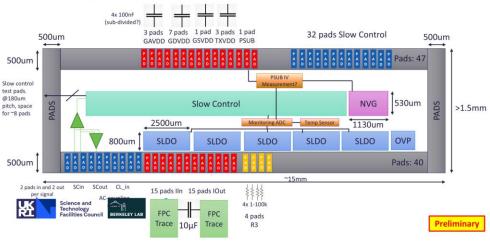

# **Shunt LDO**

### **SLDO**

- Serial powering required for services reduction

- Reviewed with external participants

- SLDO test structure (including preregulator) submitted March 2025 (UK funded, submitted via Europractice)

- Expected back September 2025

- Test system in preparation

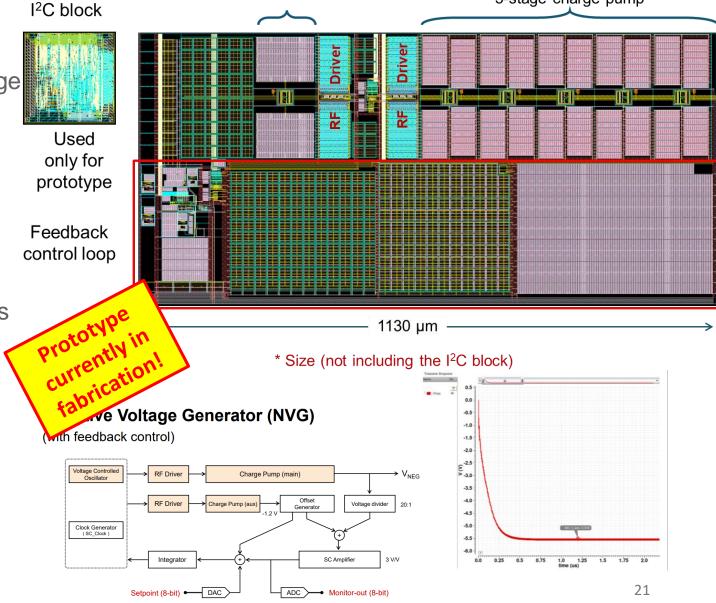

# **Negative Voltage Generator**

NVG test structure layout, courtesy of Praful Purohit, BNL

5-stage charge pump

### **NVG**

Local generation of sensor bias voltage needed due to combination of serial powering and low bias level (~1V)

Reviewed with external participants

Test structure submitted March 2025

Also included transistor test structures and other blocks

- Expected back September 2025

- Test system in preparation

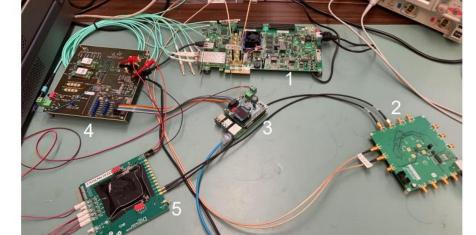

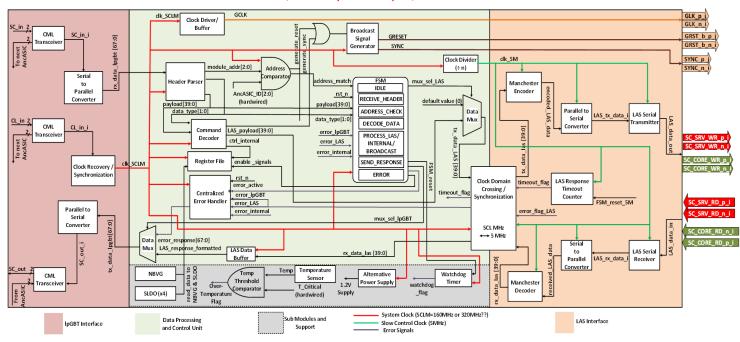

## **AncBrain**

### **AncBrain**

- Required for services reduction and control of NVG and SLDO

- Core modules complete, working on tests with MOSAIX emulator

- Plan to submit as part of first AncASIC

- Hardware emulator in preparation between LBNL, ORNL and BNL

#### AncBrain Plan, courtesy of Arif Igbal, BNL

- 1. KCU105

- 2. Clock generator

- 3. PiGBT (status monitor only)

- 4. VLDB+

- 5. ETROC2 test board

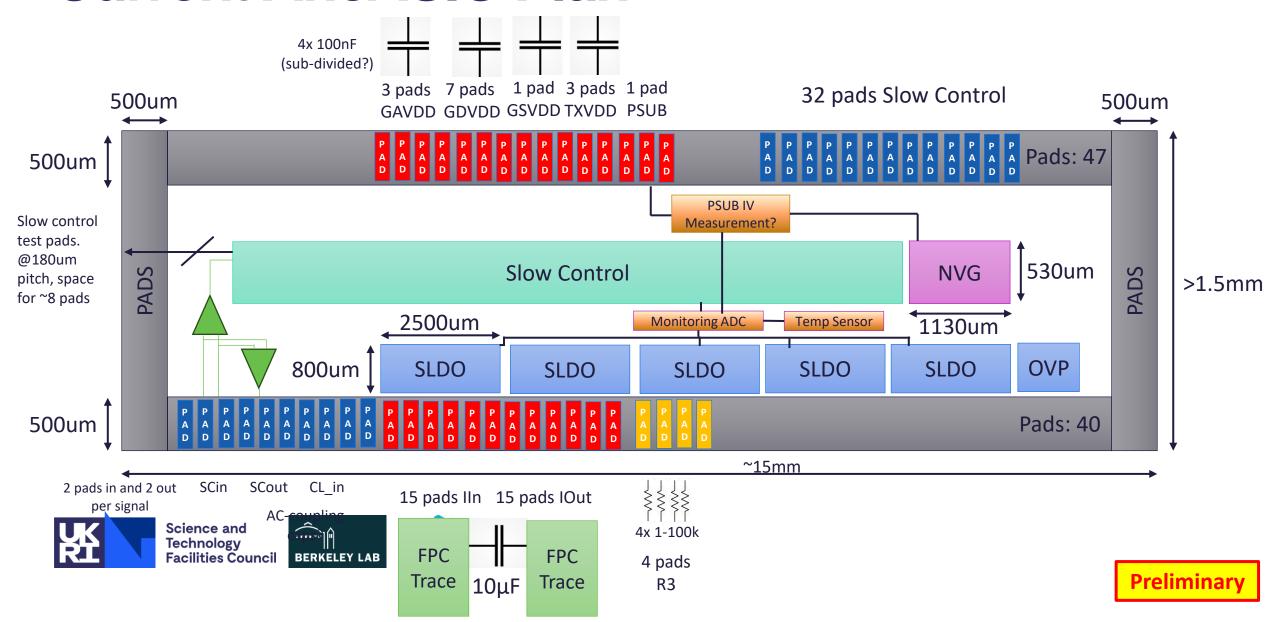

# **Current AncASIC Plan**

# Progress, Next Steps and Challenges

### **Progress and Next Steps**

AncASIC requires three main blocks. Prototypes for 2 have already been submitted:

MPW1 (NVG)

MPW2 (SLDO)

March 2025 March 2025

Work has started on the next components, and planning for further phases:

- Complete MPW1/2 Test Systems

- Complete MPW1/2 Testing

- Complete AncBrain Design and Validation

- Submit AncASIC V1

- Complete AncASIC V1 Test System

- Complete AncASIC V1 Testing

- Complete AncASIC V2 Design Modifications

- AncASIC V2 Production

September 2025 (to match out-of-fab date)

March 2026

Q3 CY2025

September/November 2025

March/June 2026

Aug/December 2026

Q1 CY2027

Q1 CY2027

# Conclusion

## Conclusion

### **AncASIC Status**

#### AncASIC

- Design progressing well

- First test structures in fabrication

- AncBrain design under way

- Next steps are testing, AncBrain completion and full integration

- DSA to be agreed (although some movement)

#### MOSAIX/EIC-LAS

- Submission very soon

- CERN/DOE agreement still needed

#### **Current AncASIC Plan**

#### **ER2: MOSAIX**

# Questions?

### References

[1] Radiation and Rate Environment, Gonella L., ePIC Collaboration Meeting, Argonne, Jan 9 2024, https://indico.bnl.gov/event/20473/contributions/84983/

[2] S. Fernandez-Perez, M. Backhaus, H. Pernegger, T. Hemperek, T. Kishishita, H. Krüger, N. Wermes, *Radiation hardness of a 180nm SOI monolithic active pixel sensor*, Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, Volume 796, 2015, Pages 13-18, ISSN 0168-9002, <a href="https://doi.org/10.1016/j.nima.2015.02.066">https://doi.org/10.1016/j.nima.2015.02.066</a>.