# CAEN Front-End Readout System DT-5202 Tests

Amarise Edgell

#### DT5202 Information

- 64 channels

- 4 readout modes

- Connection via Micro USB or Ethernet

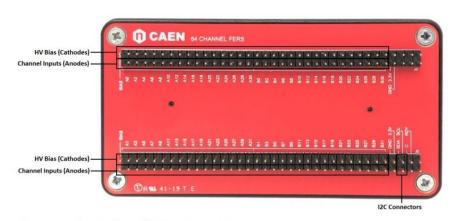

Fig. 7.6: DT5202 front panel view.

Figures taken from the CAEN DT5202 user manual, pp 28-29

#### **FERS Readout Modes**

- Spectroscopy (Pulse Height Analysis):

- Global trigger; all channels perform ADC of pulse amplitude; conversion delay is

10 μs.

- Timing:

- Time over Threshold or Time of Arrival; channels run independently

- Counting:

- Counts self triggers for each channel individually; max counting rate is 20 Mcps

- Spectroscopy and Timing:

- PHA and Timing data available

#### **Initial Test (Internal Pulse)**

- Micro USB connection to PC

- Janus for Windows

- Two modes for Janus: GUI and Console mode

- Using GUI mode for these tests

- Used the DT5202's internal pulse to test if the unit was working

- Pulse Amplitude set to 300 for all tests

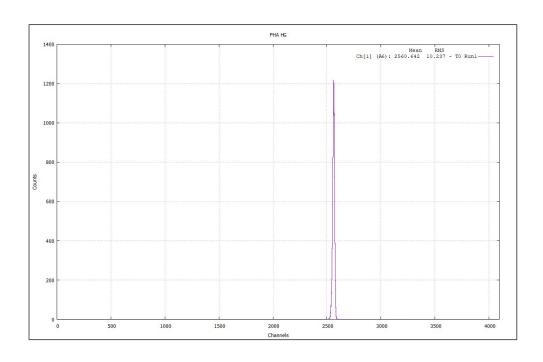

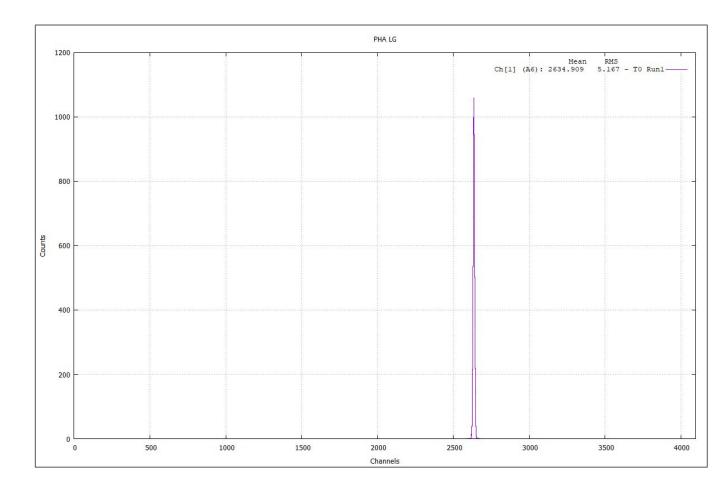

# **Spectroscopy Mode**

- Gain Selection Modes: High Gain (HG), Low Gain (LG), Both, Auto

- o Plot types: HG & LG

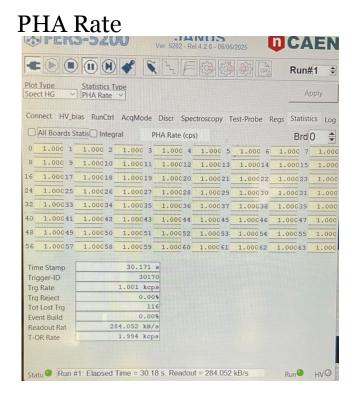

- Statistics: PHA Rate & PHA

Count

- Default settings from manual:

- o LG/HG set to 50

- Trigger period 1 ms

- Channel trigger width 8 ns

Spectroscopy mode using HG for gain selection and plotting (similar results for LG and HG+LG)

#### **Spectroscopy Statistics**

#### **PHA Count**

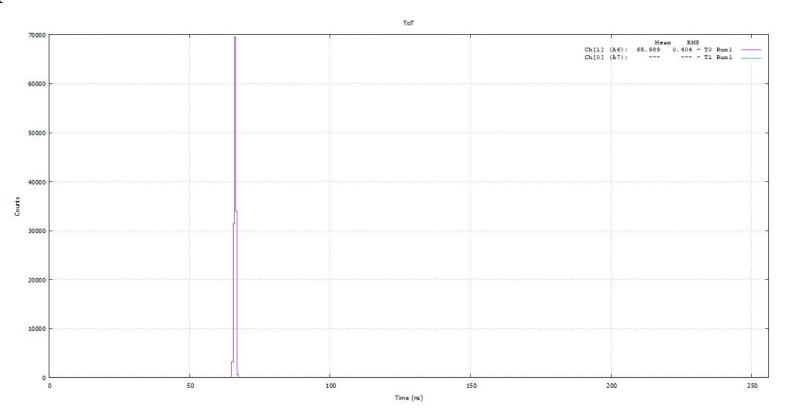

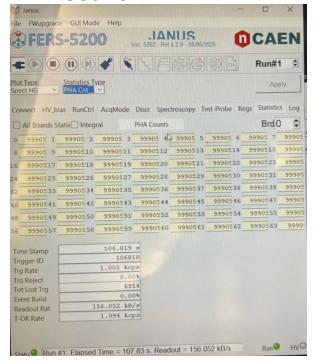

# **Timing Mode**

- Trigger settings: Common Start & Common Stop

- Only Common Start available for internal pulse

- Plot types: Time of Arrival

(ToA) & Time over Threshold

(ToT)

- Settings from manual:

- Tref window set to 1 μs

- No Tref delay

- Fast Shaper Input set to LG

Timing mode with ToT plot for TD Coarse Threshold at 300

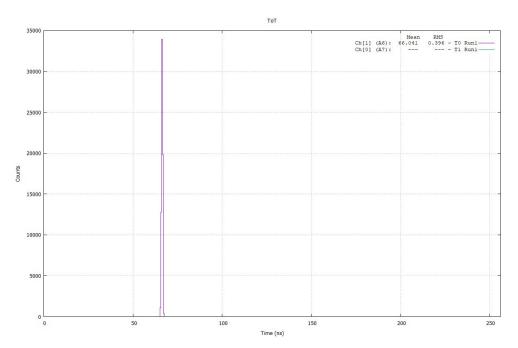

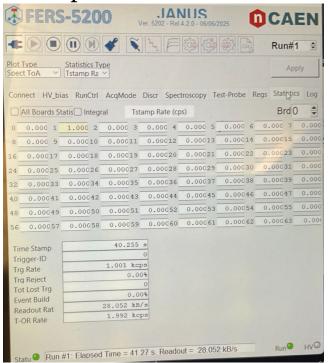

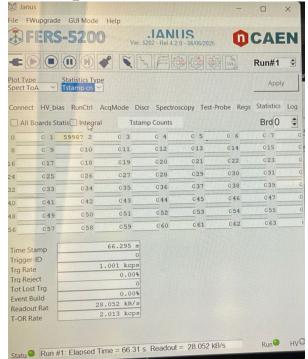

# **Timing Statistics**

TStamp Rate

TStamp Count

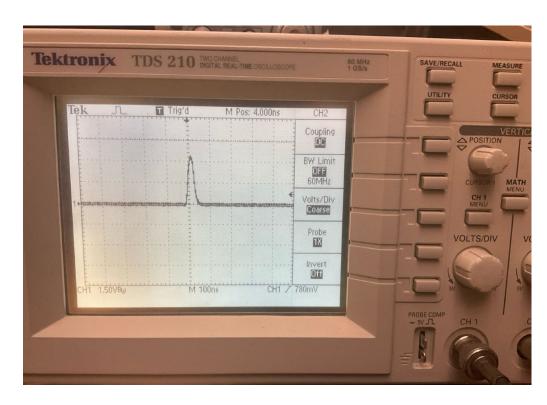

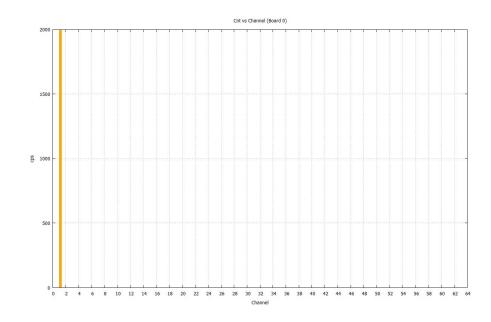

# **Counting Mode**

- Pulse for channel 1 only

- Counting intervals determined by either external signal or programmable gate width

- o Programmed gate width for this test

- Settings

- o 8 ns gate width

- Digital probe set to "CLK 1024"

(internal signal at about 61 Hz)

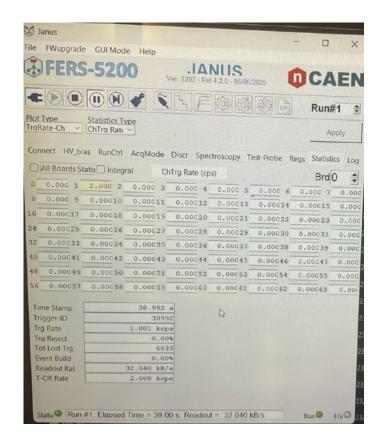

# **Counting Statistics**

• Statistics Type: ChTrg Rate

# **Conclusions & Next Steps**

- FERS unit seems to be working in all modes so far

- Further tests: use external source

- o SiPM

- Test different inputs to multiple channels

#### Spectroscopy: LG

#### Timing: ToA