# dRICH RDO

P. Antonioli, D. Falchieri, S. Geminiani,L. Rignanese, G. Torromeo(INFN Bologna)

on behalf of dRICH DSC

[ special thanks to A. Lonardo – INFN Rome, to prepare the dRICH DAQ backend discussion in this presentation ]

Incremental Preliminary Design and Safety Review of the EIC Detector DAQ and Electronics

September 3-4, 2025

# dRICH RDO re-cap in two slides (I)

dRICH status: M. Contalbrigo at April 2025 PID Review dRICH SiPM status: R. Preghenella at April 2025 PID Review

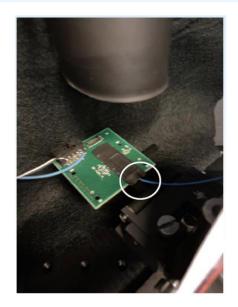

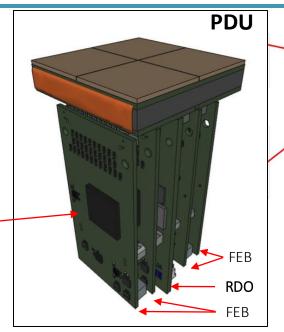

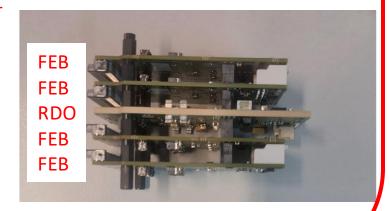

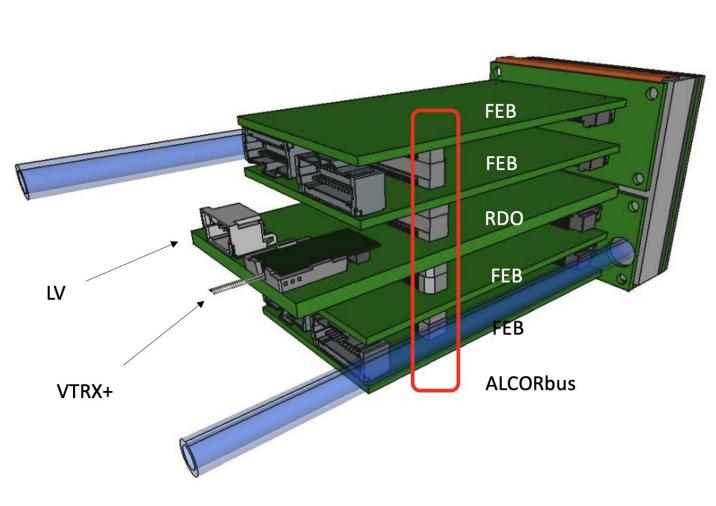

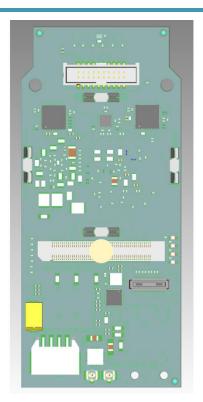

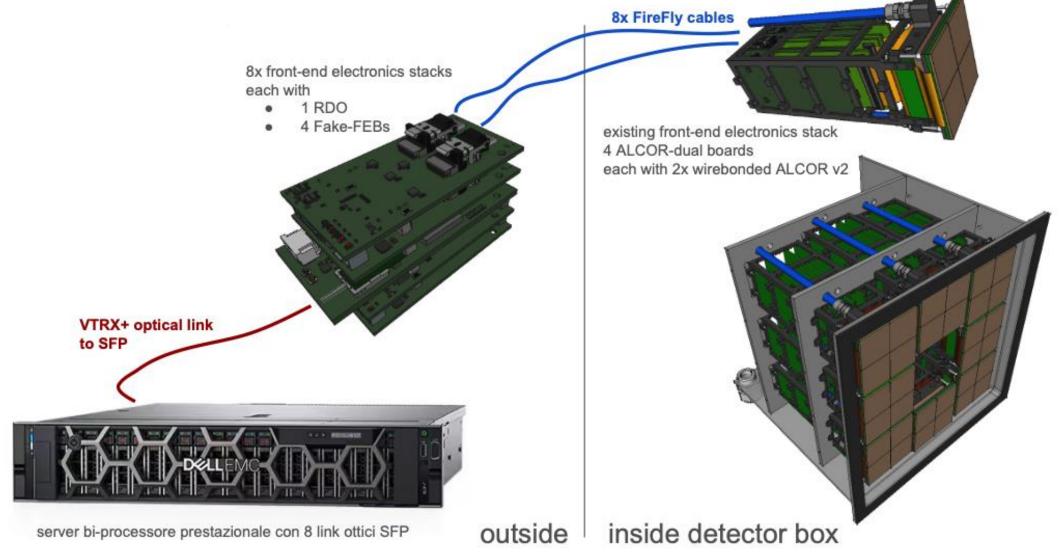

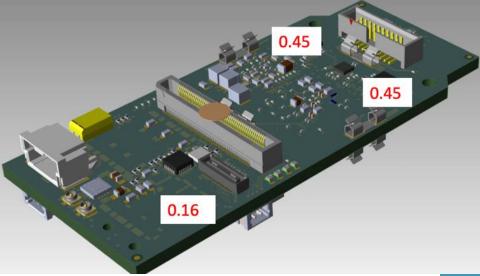

RDO is inside dRICH **PDU** photo detection unit

dRICH RDO requirements (from DAQ PDR review June 2024)

- **space**: 40 x 90 mm area

- RDO not accessible: remote firmware upgrade must be possible

- RDO FPGA need high speed ("high performance") 120 I/O pins to implement ALCOR bus towards FEBs

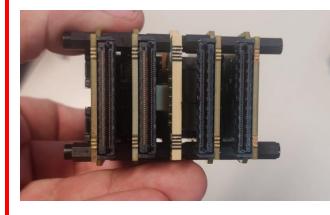

- RDO connector need high speed specs. and (minimum) 60 I/O pins each

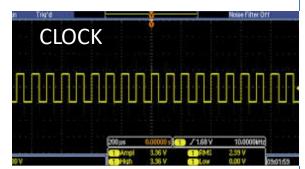

- RDO must implement clean **clock** multiplication (ALCOR@394 MHz, EIC clock 98.5 MHz)

- RDO must reconstruct clock via optical link

- RDO must produce clean clock (minimize jitter)

- opt. tranceiver must minimize space/power consumption + "rad hard" and bandwitdh up to 10 Gbps

ALCOR v3

### dRICH RDO re-cap in two slides (II)

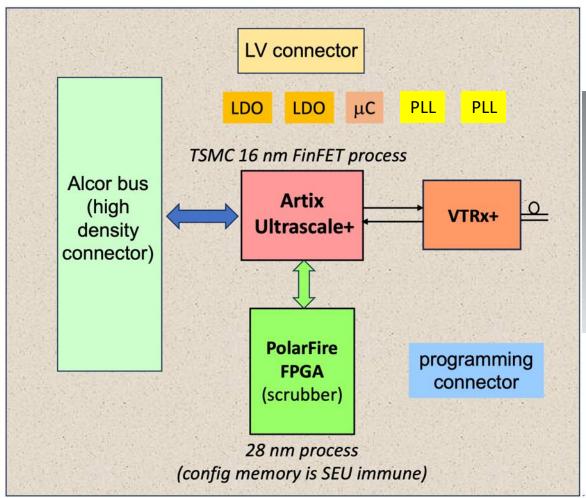

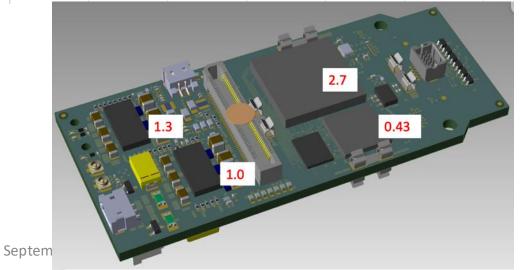

Main design choices

- a performing RAM-based FPGA + scrubbing implemented via a Flash-based FPGA

- devoted PLLs to manage clock (SkyWorks 5319 / 5326)

- VTRX+ as optical tranceiver

- a small uC acts as RDO power manager

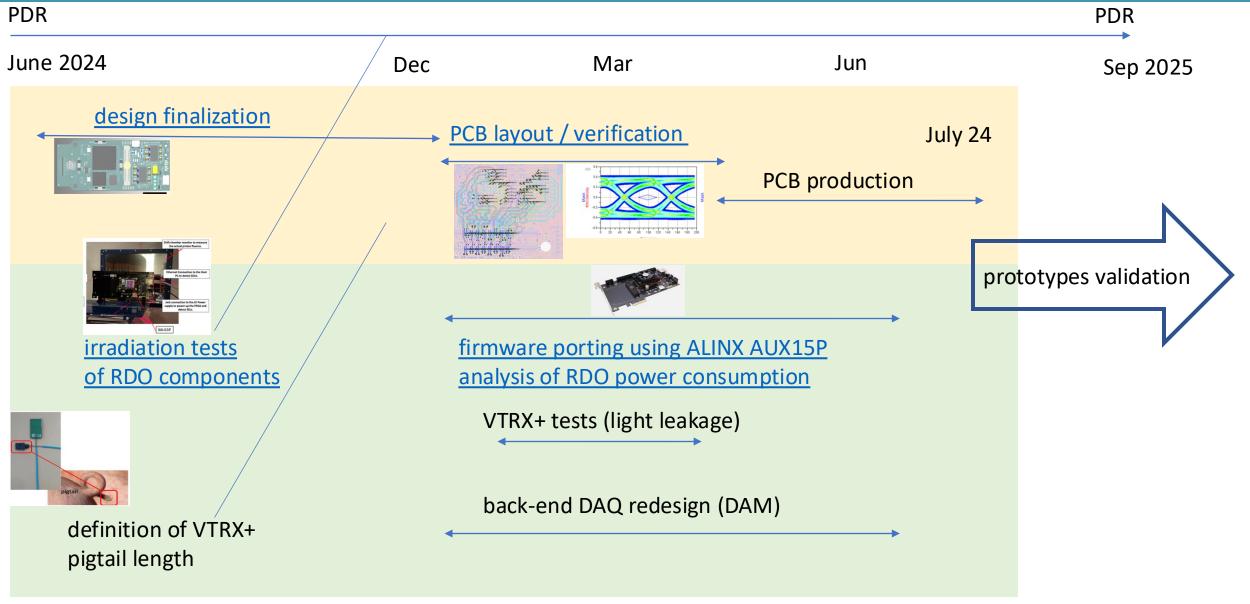

Long and painful elaboration of exact RDO specifications + components selection + schematics preparation + layout time + production time: design started January 2024

# dRICH RDO is finally getting real

First two prototypes finally received July 24, 2025!

This report:

- → updates/activities w.r.t. PDR 2024 as reference: <a href="https://doi.org/dRICH RDO PDR 2024 presentation">dRICH RDO PDR 2024 presentation</a>

- → ongoing debug / tests on first two prototypes

- → plan (2025/2026)

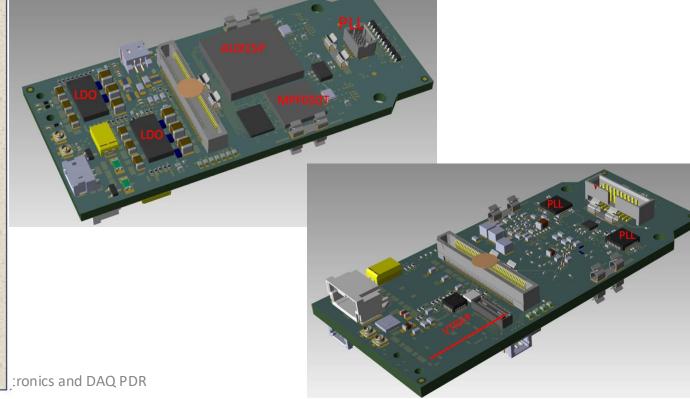

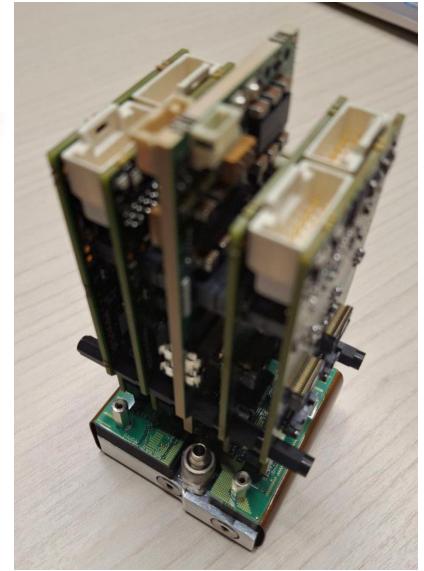

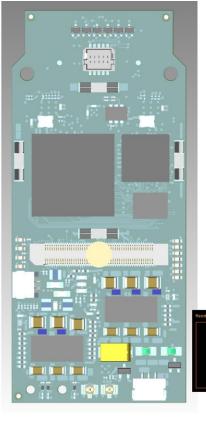

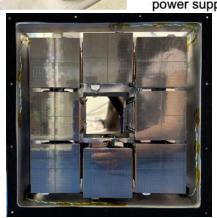

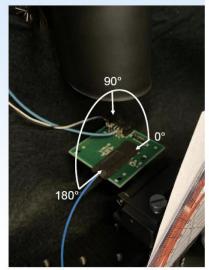

# no longer 3D-rendering: some pics

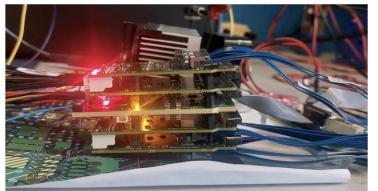

**RDO+4 FEB dRICH**

front side: connectors to SiPM

The dRICH electronic burger

Se

# from CAD to pics: the PDU

### Updates since 2024 PDR

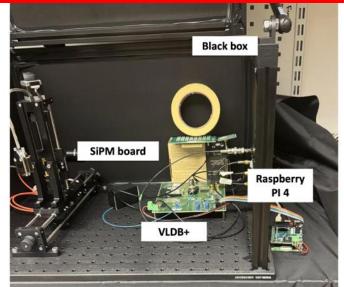

### VTRx+: light leakage studies + pigtail length (I)

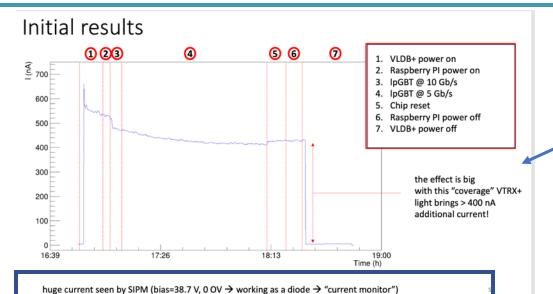

VTRX+ light leakage tests

Context: LHCb colleagues told us VTRx+ has significant light

leakage (from the transceiver + fiber)

no cover of the fiber SIPM in front of VTRX+ (not as PDU case, see next slide) all leds of VLDB+ shielded with dark tape

"minimal" cover of VTRx+ (+ BNC adapter ;-) to keep it "tight"

Test bench: black box + 1 SIPM

R. Preghenella/S.Geminiani/A. Paladino

More details on PA's talk at DAQ-Electronics WG/eRD109 (March 2025)

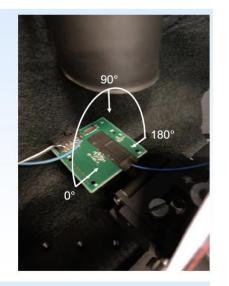

### VTRx+: light leakage studies + pigtail length (II)

Additional VTRX+ plastic box + Thorlabs masking tape

- → No measurable extra-current: just 5 nA!

- → moved to 2.7 OV

With oscilloscope and measuring DCR (VLDB+ ON/OFF) we finally see:

(400.0 +- 1.8) kHz. VLDB+ ON (398.4 +- 2.7) kHz VLDB+ OFF

(ON-OFF) = (1.9 +- 3.3) kHz

- → compatible with zero. Note that some kHz is however close to DCR @ 30 C

- → need to move to -30 C to check

#### Long story short:

- huge leak of light from VTRx+

- we will need to design an effective shield. CERN ESE-VL+ is doing something similar (<u>details</u>).

- initial results (room temperature only) encouraging

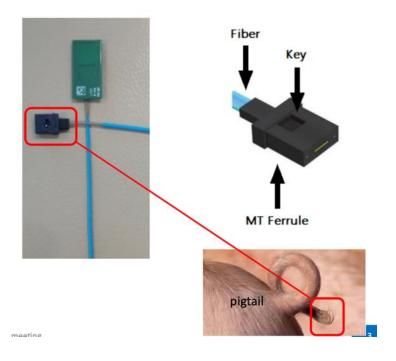

- and note after long discussion (Sep/Dec 2024) we opted for 20 cm pigtail length

#### From 2024 June FDR:

#### Comments

VTRX+ pigtail lengths must be defined at least 6 months in advance of VTRX+ production. The mechanical designs of both sub-systems are well on track to allow this definition on schedule.

#### Going shorter and avoid dangling?

We considered several options but for each of them the number of cons largely exceeds the pros. And if too short we can't come back. We don't have any convincing option for such scheme.

#### How to proceed? We go baseline

We select a 20 cm dangling pigtail

Design needs to be carefully followed up to setup proper access, secure maintenance etc. (but this is valid for almost what we are doing ;-)

dRICH option: 1500 VTRX+ with total length 20 cm

Details: PA's presentation at dRICH meeting (Dec. 2024)

additional home-made "full VTRX+ plastic box"

Details: PA's <u>presentation</u> at eRD109 (Feb. 2025)

ics and DAQ PDR

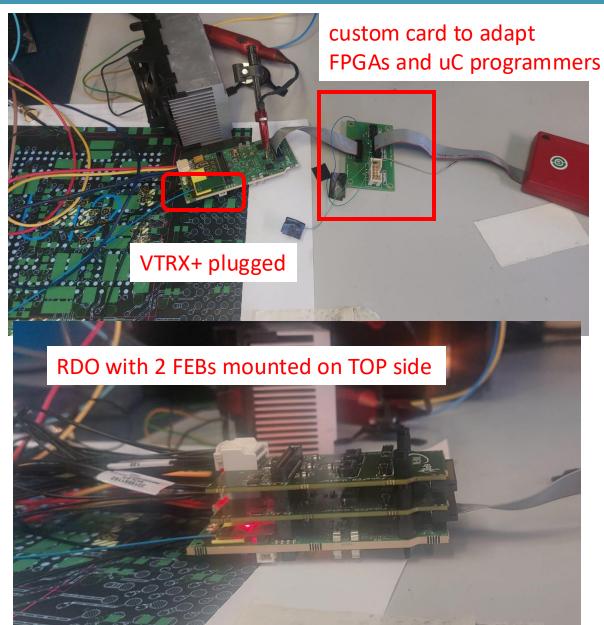

### where we are with prototypes?

10

- 1. Mechanical pairing with fake-FEB (adaptor for ALCOR32 with exactly final FEB-format with ALCOR64)

- 2. Power-up: 2.5 / 1.4 jumper to avoid power to other sections

- 3. Programming uC via external connector

- 4. Power-up with uC (post-programming uC): check Vout LDO

- 5. Programming Artix via external connector

- 6. Programming Polarfire via external connector

- 7. Artix at boot makes programming of SkyWorks (programming 125 MHz of Si5319 to setup clock for GTH)

- 8. Check consumptions

- 9. Check UFL I/Os

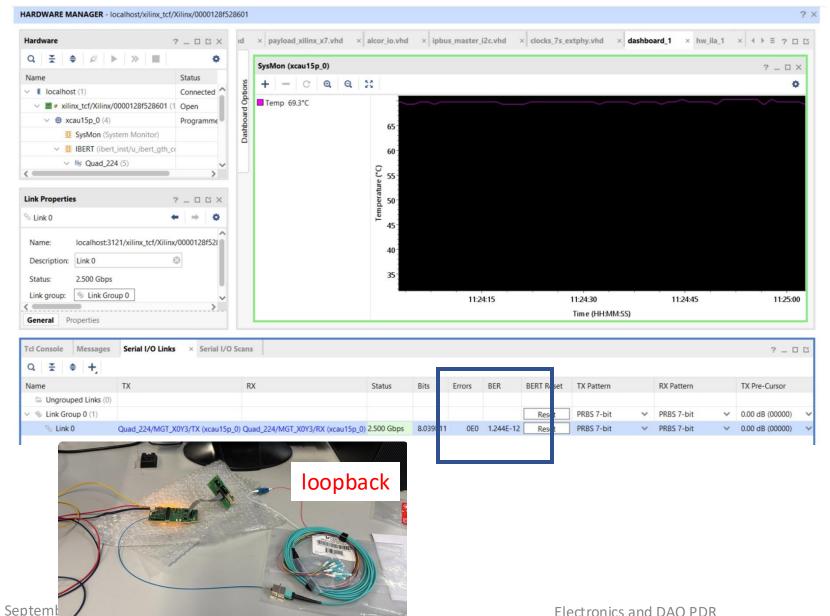

- 10. IBERT test (loopback tool integrated in Vivado) to check link

- 11. Link IPBUS via VTRX+ [MT-MPO adapter + fibers]

- 12. Turn on fake-FEB via I2C from RDO

- 13. Programming ALCOR via fake-FEB (via IPBUS → VTRX+)

- 14. ALCOR readout (via IPBUS  $\rightarrow$  VTRX+)

RDO team @ work this week on this!

When we reach point 14 we give green light to produce the other 8 RDOs for Nov. 2025 test beam ( details )

## where we are with prototypes? (UPDATE)

3.

4.

5.

6.

**₽** S

**9**

**1**0

11

12

13. P

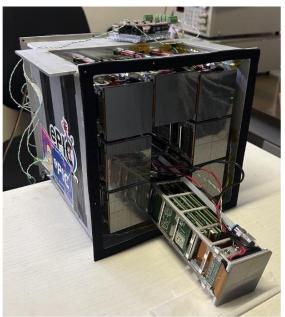

ALCOR-dual FEB

Half of a PDU

AU15P Programmer

OR32 with exactly final FEB-format with ALCOR64) er sections

**Vout LDO**

orogramming 125 MHz of Si5319 to setup clock for GTH)

check link

- Programming ALCOR via fake-FEB (via IPBUS → VTRX+)

- 14. ALCOR readout (via IPBUS → VTRX+)

- The PDU was mounted and 2 FEBs were powered-on.

- We configured all the ALCOR32s successfully.

- We read back the data aligned with the 320 MHz supplied clock.

This process was repeated for both sides without any problem from both hardware and software!

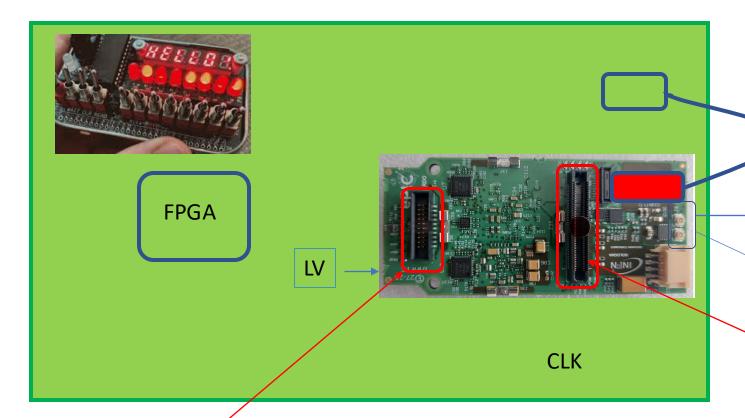

### which protocol as EIC link protocol for dRICH?

Distribution of a 39.4 MHz was made to support detectors with IpGBT, but also dRICH agreed with ePIC DAQ to receive a 39.4 MHz clock - close to 40.08 MHz à la LHC. This would be instead of 98.5 MHz (see W. Gu talk)

This will make life much easier with FELIX/RDO: FULL protocol (GBT on host) to be assessed (FULL is less resource hungry with respect to IpGBT and we don't have the ASIC, only the VTRX+) → current baseline choice

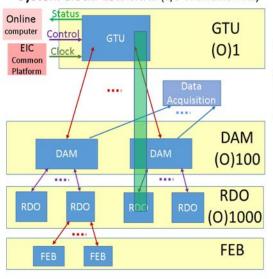

#### 1. The ePIC designs

System Clock: 19.7 MHz (1/5 of BX 98.5MHz)

Mini DAQ, functionally includes GTU, DAM, and RDO

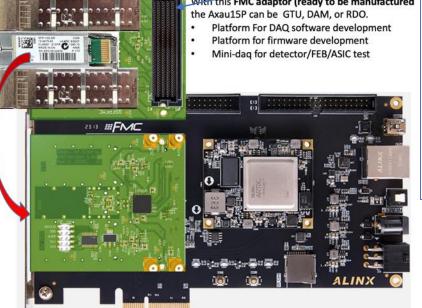

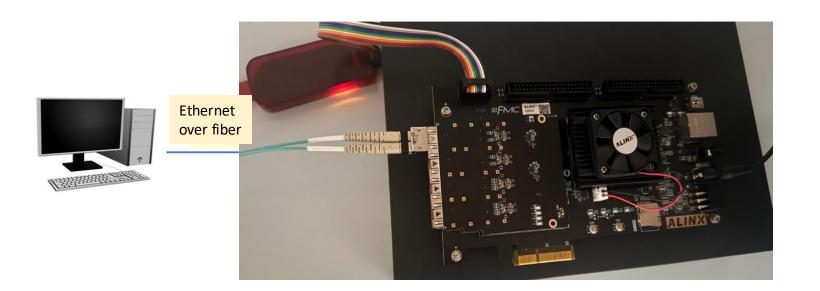

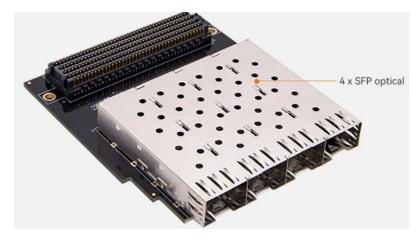

#### FMC/(Q)SFP adaptor

The piggy back produced by JLab), will allow us (Bologna and Rome) to use a pair of ALINX/AUX15P to first mimic a "RDO" and a "FELIX" link

Second step: FLX-182 (Rome1) ← RDO

Third step: FLX-155 ← RDO

Jefferson Lab

### Addressing 2024 PDR report specific comments

#### Relevant comments:

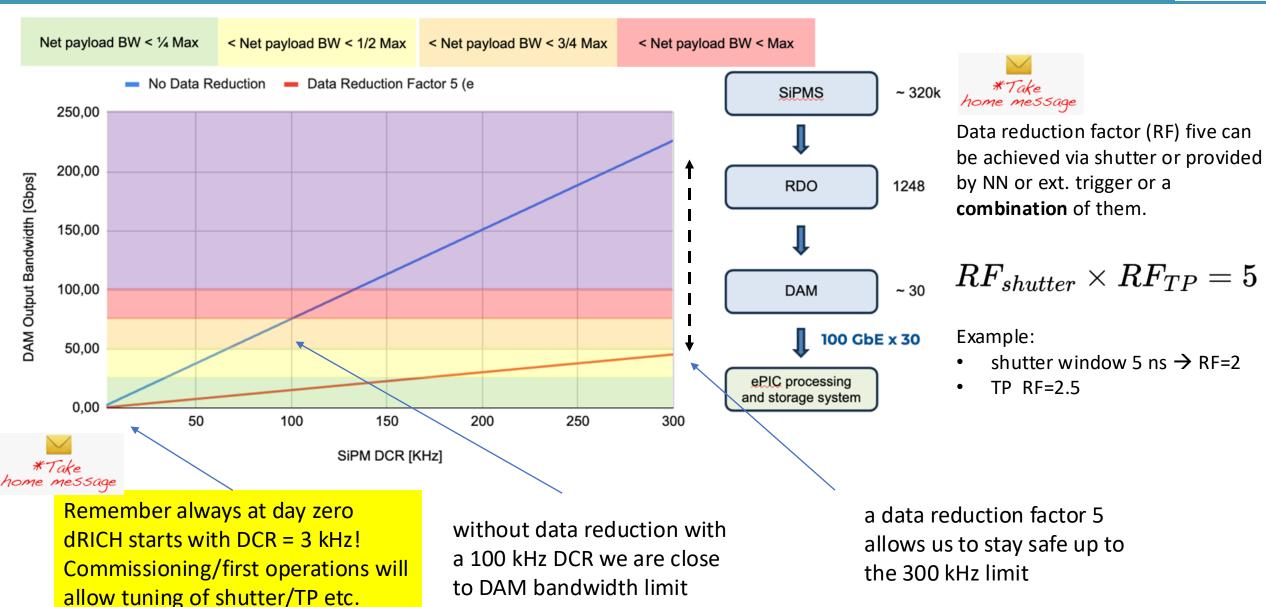

- We applaud the adaptation of the readout architectures to match detector environment specs, in particular for the dRICH where steps to mitigate the high DCR will be implemented in the ASIC together with other handles such as triggering within the DAM.

- We appreciate these steps towards robustness. However, it would be reassuring to see simulations or measurements to demonstrate the effectiveness of the shuttering mechanism for dRICH.

#### Relevant recommendations:

• Rationalize the dRICH readout with the benefit of simulation/measurement to reassure the community of the benefit of the shutter implementation.

- dRICH backend DAQ was rationalized following studies of ML techniques/NN deployed on DAMs

- Shutter implemented on ALCOR V3 and studies are on-going on shutter performance to assess best (and safe) shutter time width.

- → discussion and results reported in next slides

## Updated throughput modelling (I)

| dRICH DAQ parameters                      |          |             |

|-------------------------------------------|----------|-------------|

| RDO boards                                | 1248     |             |

| ALCOR64 x RDO                             | 4        |             |

| dRICH channels (total)                    | 319488   |             |

| Number of DAM                             | 30       |             |

| Input link in DAM                         | 42       | ١           |

| Output links from DAM to TP               | 1        |             |

| Number of DAM Trigger Processor           | 1        |             |

| Input link to DAM Trigger Processor       | 30       |             |

| RDO-DAM Link Bandwidth (VTRX+) [Gb/s]     | 10       |             |

| DAM to Echelon-0 Switch Bandwidth [Gb/s]  | 100 ▼    |             |

| dRICH Interaction tagger reduction factor | 1 🔻      |             |

| Interaction tagger latency [s]            | 1,00E-04 |             |

| EIC parameters                            |          | $\setminus$ |

| EIC Clock [MHz]                           | 98,522   |             |

| Orbit efficiency (takes into account gap) | 0,92     |             |

| ALCOR parameters                            |          | Notes                                     |

|---------------------------------------------|----------|-------------------------------------------|

| Front end limit [kHz]                       | 4000     |                                           |

| ALCOR Clock [ MHz]                          | 394,08 ▼ | It will be 394.08 MHz or 295.55 MHz       |

| Channels/serializer                         | 8        |                                           |

| Bits per hit                                | 64       | 2 32-bit words per hit (also TOT)         |

| Bits per hit encoding 8/10                  | 80       |                                           |

| Serializer band limit [Mb/s]                | 788,16   |                                           |

| Theoretical Serializer limit/ channel [kHz] | 1231,5   | this would be with 0 control words        |

| Serializer limit single ch [kHz]            | 800      | this is expected to improve with ALCOR v3 |

| Number of serializer per chip               | 8        |                                           |

|                                             |          |                                           |

| Channel/chip                                | 64       |                                           |

| Shutter width (ns)                          | 2 ▼      | (if you put 10 ns == no shutter)          |

|                                             | K        |                                           |

|                                             |          |                                           |

Reduction factor via shutter RF = 10 ns/(shutter width)

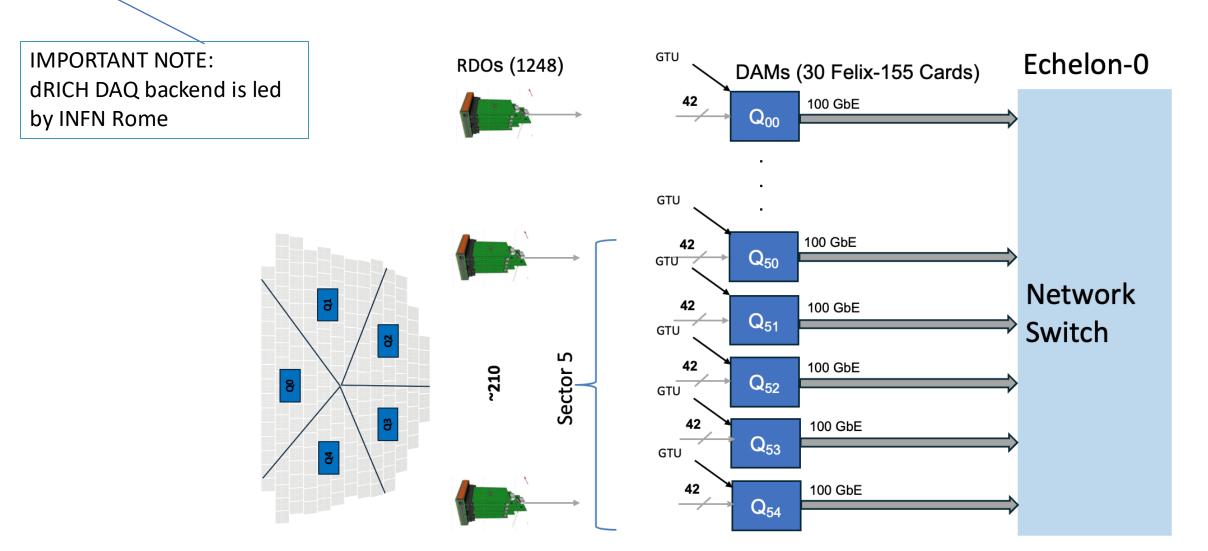

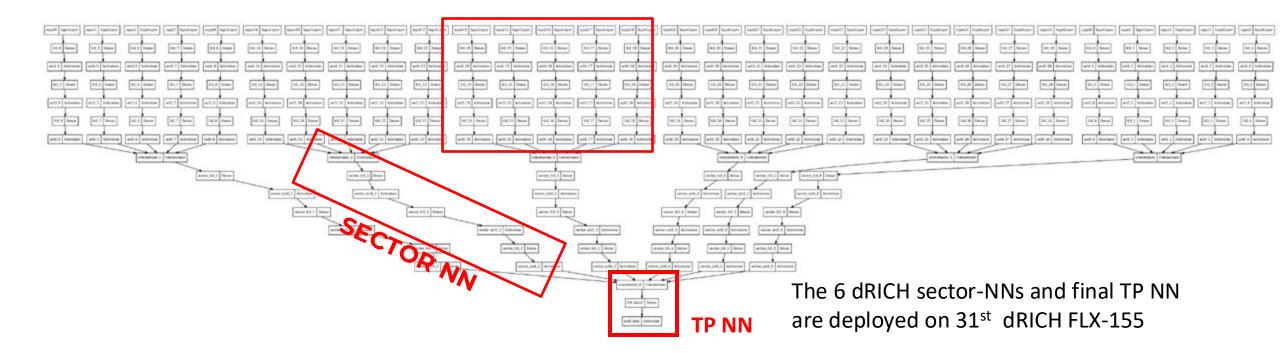

dRICH backend DAQ reorganized following studies from INFN Rome (see next slides) from 27+1 to 30+1 FLX-155: 30 DAMs + 1 Trigger Processor (TP)

Reduction factor provided by whatever ext. trg (including NN on dRICH DAMs)

## Updated throughput modelling (II)

| DAM to Echelon-0 Switch Bandwidth [Gb/s]  | 100 ▼    |                                                         |                                        |     |                                  |

|-------------------------------------------|----------|---------------------------------------------------------|----------------------------------------|-----|----------------------------------|

| dRICH Interaction tagger reduction factor | 1 🔻      |                                                         | Channel/chip                           | 64  |                                  |

| Interaction tagger latency [s]            | 1,00E-04 |                                                         | Shutter width (ns)                     | 2 ▼ | (if you put 10 ns == no shutter) |

| EIC parameters                            |          |                                                         |                                        |     |                                  |

| EIC Clock [MHz]                           | 98,522   |                                                         |                                        |     |                                  |

| Orbit efficiency (takes into account gap) | 0,92     |                                                         |                                        |     | This is worst case!              |

|                                           |          |                                                         |                                        |     |                                  |

| dRICH data stream analysis                |          | Limit                                                   | Comments                               |     |                                  |

| Sensor rate per channel [kHz]             | 300,00 🕶 | 4.000,00                                                |                                        |     |                                  |

| Rate post-shutter [kHz]                   | 55,20    | 800,00                                                  |                                        |     |                                  |

| Throughput to serializer [ Mb/s]          | 34,50    | 788,16                                                  |                                        |     |                                  |

| Throughput from ALCOR64 [Mb/s]            | 276,00   |                                                         | limit FPGA dependent: - check with RDO |     |                                  |

| Throughput from RDO [ Gb/s]               | 1,08     | 10,00                                                   | based on VTRX+                         |     |                                  |

| Input at each DAM [Gbps]                  | 45,28    | 420,00                                                  |                                        |     |                                  |

| Buffering capacity at DAM [Mb]            | 4,64     |                                                         | to be checked but seems manageable     |     |                                  |

| Output from each DAM [Gbps]               | 45,28    | 100,00                                                  |                                        |     |                                  |

| Aggregated dRICH data throughput          |          | Comments                                                |                                        |     |                                  |

| Total input at DAM [ Gb/s ]               | 1.358,44 | This is only "inside" DAM, not to be transferred on PCI |                                        |     |                                  |

| Total output from DAM [ Gb/s ] to Echelon | 1.358,44 | Reduction from interaction tagger (FPGA or det. based)  |                                        |     |                                  |

\*Take home message

Using only the shutter with a reduction factor 5 (2 ns over 10 ns BC) we keep 1.3 Tbps throughput and we stay within all limits (including transfer from DAM to Echelon-0)

## Updated throughput modelling (III)

| 7                                         | l        | I                  | produce the contract of the co | 1    | 1                                |

|-------------------------------------------|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------|

| DAM to Echelon-0 Switch Bandwidth [Gb/s]  | 100 ▼    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |

| dRICH Interaction tagger reduction factor | 5 🕶      |                    | Channel/chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64   |                                  |

| Interaction tagger latency [s]            | 1,00E-04 |                    | Shutter width (ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10 ▼ | (if you put 10 ns == no shutter) |

| EIC parameters                            |          |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |

| EIC Clock [MHz]                           | 98,522   |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |

| Orbit efficiency (takes into account gap) | 0,92     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |

|                                           |          |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |

| dRICH data stream analysis                |          | Limit              | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 10 ns means no shutter           |

| Sensor rate per channel [kHz]             | 300,00 ▼ | 4.000,00           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |

| Rate post-shutter [kHz]                   | 276,00   | 800,00             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |

| Throughput to serializer [ Mb/s]          | 172,50   | 788,16             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |

| Throughput from ALCOR64 [Mb/s]            | 1.380,00 |                    | limit FPGA dependent: - check with RDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                  |

| Throughput from RDO [ Gb/s]               | 5,39     | 10,00              | based on VTRX+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | data reduction via               |

| Input at each DAM [Gbps]                  | 226,41   | 420,00             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |

| Buffering capacity at DAM [Mb]            | 23,18    |                    | to be checked but seems manageable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | "another method"                 |

| Output from each DAM [Gbps]               | 45,28    | 100,00             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |

| Aggregated dRICH data throughput          |          | Comments           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |

| Total input at DAM [ Gb/s ]               | 6.792,19 | This is only "insi | de" DAM, not to be transferred on PCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                                  |

| Total output from DAM [ Gb/s ] to Echelon | 1.358,44 | Reduction from     | interaction tagger (FPGA or det. based)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _    |                                  |

|                                           |          |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |

further risk mitigation here might be applied using two TX links instead of one

If shutter is not effective we need a reduction factor 5 from a dRICH interaction tagger method and we stay within all limits (including transfer from DAM to Echelon-0)

### Will the shutter be effective?

(for all work on shutter implementation in ALCOR v3 and related simulations see F. Cossio talk)

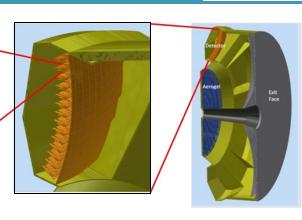

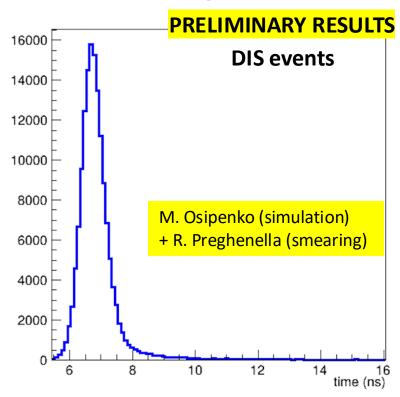

### Simulations of hit time distribution at dRICH entrance window (before aerogel)

- Hit time distribution (primaries) has Gaussian shape + a tail

- Bulk of primary hits lies within 2 ns ( $\sigma_{pr} \cong$  260 ps)

- added in quadrature time zero jitter (  $\sigma_{t0}$ = 250 ps) + front-end resolution (  $\sigma_{FE}$ = 150 ps)

$$\sigma = \sqrt{\sigma_{pr}^2 + \sigma_{t0}^2 + \sigma_{FE}^2} pprox \,$$

400 ps

• from cumulative distribution 99% of particles included with a shutter window of 5 ns (from 5.5 ns to 10.5 ns → 50% DCR data reduction)

Full simulation (including Cerenkov light propagation) in progress:

- → we don't expect a large spread added by photon emission + propagation

- → impact of time slewing effect (see F. Cossio talk) to be assessed

### dRICH DAQ: the backend (updates from 2024)

Details about dRICH DAQ backend studies in A. Lonardo's talks at ePIC <u>Jan 2025</u> meeting and ePIC Italia <u>June 2005</u> meeting

### dRICH data reduction integrated in the DAQ Backend (I)

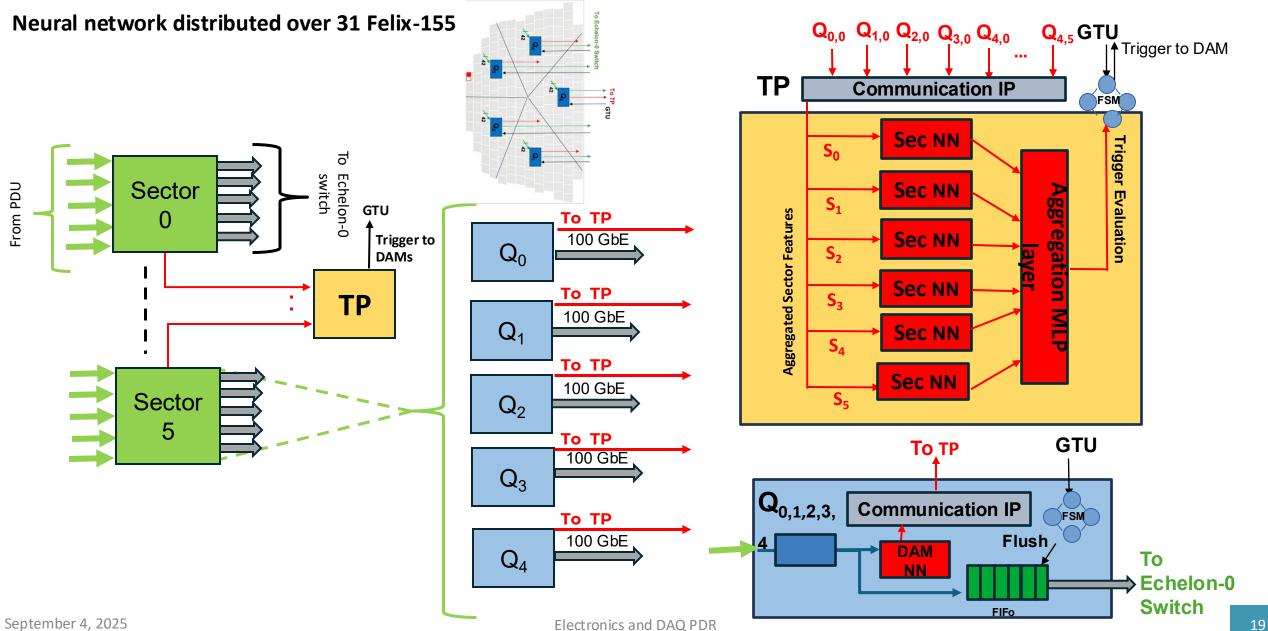

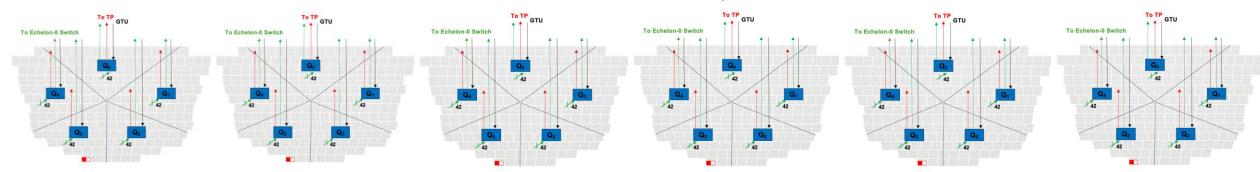

# NN deployment model and DAMs

#### 6 dRICH sectors – 5 DAMs/sectors

### Studies of NN models for distributed deployment on DAMs + Trigger Processor

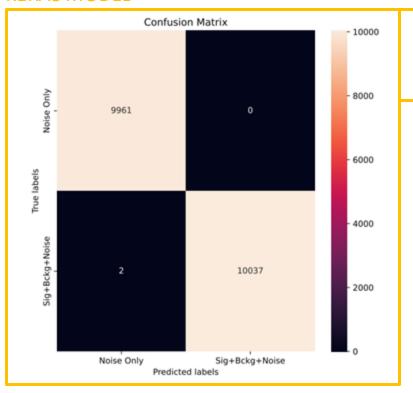

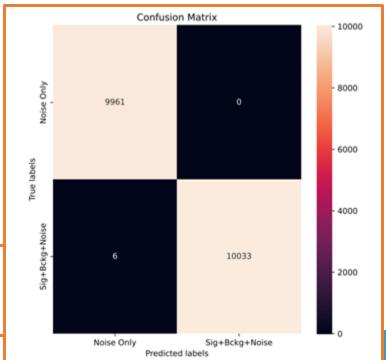

#### Data Reduction performance @ luminosity = 100 fb<sup>-1</sup>, time window = 10 ns **PRELIMINARY RESULTS** Test with 10000 signal+phys. background (P=Positive) + 10000 pure noise events (N=Negative)

#### **KERAS MODEL**

- Accuracy = (TP+TN)/(TP+TN+FP+FN)= 0.997

- Purity = TP/(TP+FP) = 0.995

- Efficiency = TP/(TP+FN) = 0.999

Preliminary result indicate DAM filter could comfortably provide >> 5 data reduction factor

### **Model Quantization**

- Inputs, Activations: fixed point<16,6>

- Weights, Biases: fixed point<8,1>

#### QUANTIZED MODEL

parameterization of DCR background included

- Accuracy = (TP+TN)/(TP+TN+FP+FN) = 0.997

- Purity = TP/(TP+FP) = 0.994

- Efficiency = TP/(TP+FN) = 0.999

September 4, 2025 Electronics and DAQ PDR

# Re-cap on dRICH Output bandwidth

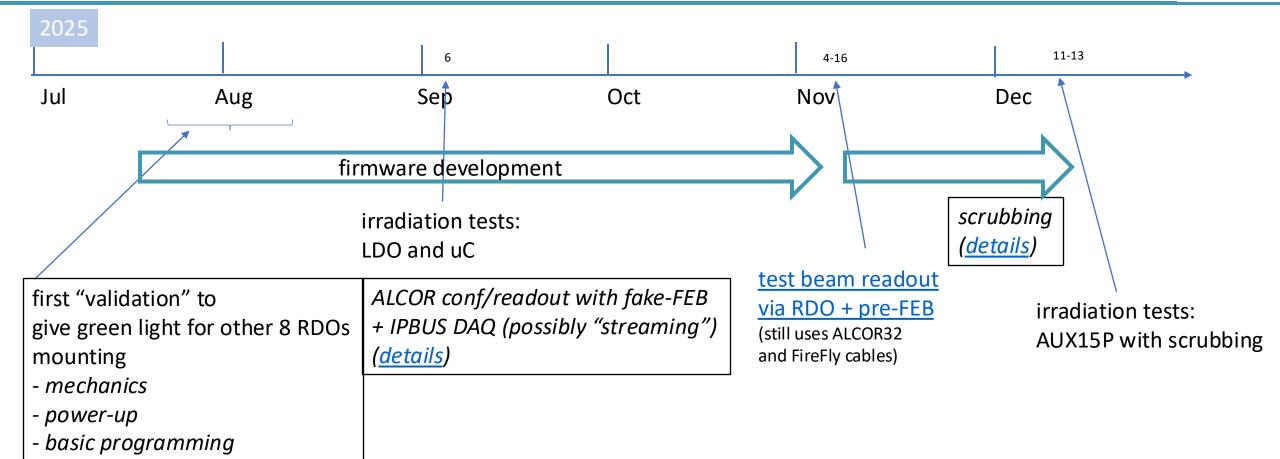

## Plannning and validation tests (2025)

### Next steps/challenges for dRICH RDO

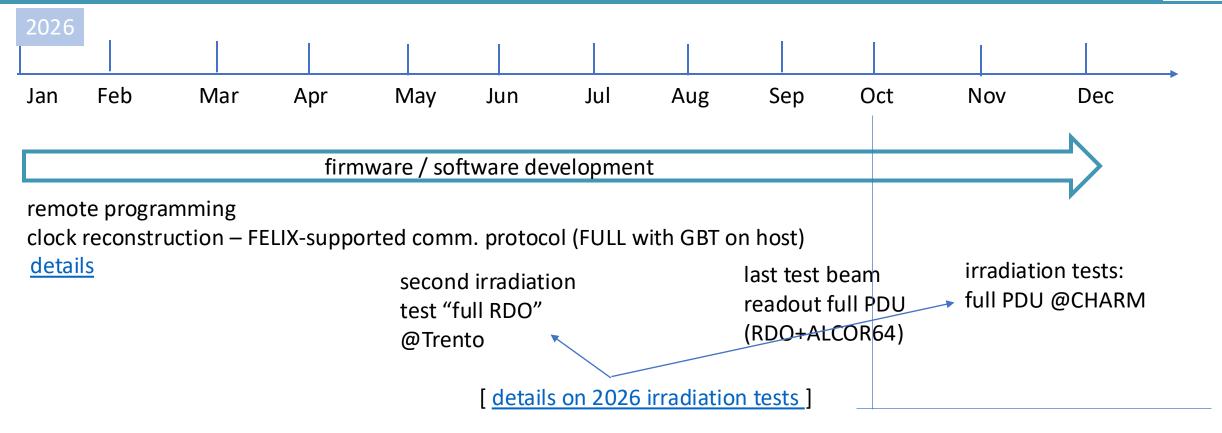

### During 2026 we need:

full validation of current prototypes including irradiation tests

fix any mistake found

design adaptations due to integration challenges that may arise (cooling, space, FPGA resources, ...)

validate communication with DAM (implementing a FELIX-supported comm. protocol)

## Plannning and validation tests (2026)

RDO communication tests with DAM

Developing a RDO testbed to test RDO production (preparing for 2027 RDO production!) [details]

requirements | specs | design

layout and production

validation

Details in backup

### Final information and conclusions

- No substantial updates for requirements with respect to the ones presented in PDR 2024

- Cost: preliminary offers for production (two companies) evaluated. Total cost ~ 700 k€ + VAT (<u>details in backup</u>)

- **Schedule**: one-year shift: pre-production in 2026, production in 2027 (in line with EIC project program)

- ESH&Q and QA considerations: as last year. Note funding for RDO testbed asked for 2026 to INFN.

INFN Bologna is following frontend DAQ (RDO) and INFN Rome backend DAQ (FLX-155): hardware is finally available First weeks of tests on RDO are very promising, no show-stoppers identified dRICH frontend DAQ and backend DAQ are much closer to finally meet

#### **INFN BO dRICH RDO core team:**

- P. Antonioli, physicist

- D. Falchieri, electronic engineer

- S. Geminiani, PhD student

- L. Rignanese, electronic engineer

- G. Torromeo, electronic technician

RDO team works obviously very closely with INFN-TO (ALCOR), INFN-FE (detector box), INFN-BO (SiPM and PDU coordination), INFN-RM1 (backend DAQ) colleagues. INFN-GE and INFN-TS are contributing to detector simulations.

# Backup

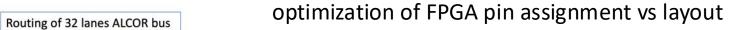

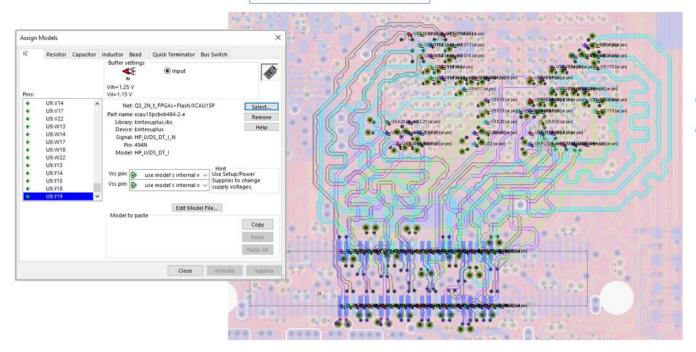

### Design finalization on layout and cross-checks

### high-speed differential line modeling

Much more details in D. Falchieri's <u>presentation</u> at WG Electronics and DAQ/eRD109 (April 2025)

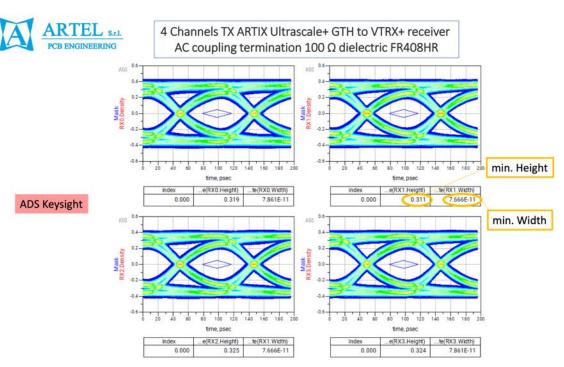

### Irradiation tests (I)

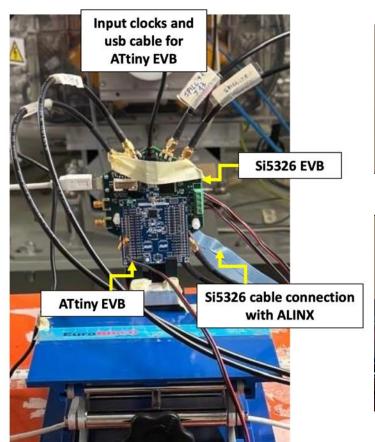

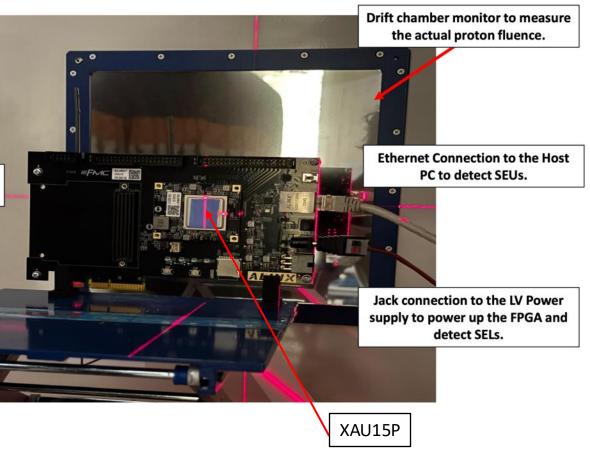

- Waiting for full RDO we tested several key components: PLL (Si5326), uC (ATtiny417) and AMD FPGA (AUX15P)

- irradiation with a proton beam at Centro di Protonterapia in Trento / December 2024

- TID<sub>5</sub>  $\cong$  2.3 krad (1000 fb<sup>-1</sup>) and  $\Phi$ (h>20 MeV)  $\cong$  700 Hz/cm<sup>2</sup> (including a safety factor 5)

Note TID<sub>5</sub> estimates increased by a factor 3.5 since PDR 2024

See presentation by S.Geminiani @ePIC Collaboration meeting (Jan 2025)

### Irradiation tests (II)

30

MTBF= Mean Time Between Failure

SEU = Single Event Upset

SEL = Single Event Latchup

from conclusions presented in January:

1. We integrated  $TID \sim 2.8 \cdot TID_5$  for the AU15P,  $TID \sim 10 \cdot TID_5$  for the ATtiny and  $TID \sim 18 \cdot TID_5$  for the Si5326.

Devices tested up to a TID largely exceeding expected TID @dRICH: no destructive effects seen for TID ≤ TID<sub>5</sub>

No significative cumulative effect or SEL for Si5326 and AU15P, while the **ATtiny stopped working at TID = 23** krad.

The RDO AU15P will control the chip configuration every t ≪ 3.8 h.

3. ATtiny: SRAM MTBF = 4 h and FLASH MTBF > 43 h (for 1248 RDOs).

The FLASH MTBF is a safety limit and key RAM registers will be implemented with TMR checks.

**Comments:** investigation addendum for ATtiny + first measurements of this kind in ePIC

# Irradiation tests (III)

### AUX15P

- Monitored memory: 8/156 kb of FF memory, 3.6/5.1 Mb of BRAM and 33/33 Mb of CRAM.

- **0 SEUs** detected on **FF memory** and **69 SEUs** on **BRAM** after 2560s.

- 70 corrected SEUs, 11 uncorrected SEUs and 1 dead link detected on CRAM after 2560 s.

- No SEL detected after 3632 s.

- TID = 6.36 krad (dose rate = 10-500 rad/min) after 3632 s.

FF memory (limit @ 95% C.L.):  $\sigma < 3.5 \cdot 10^{-14} \frac{\rm cm^2}{\rm bit}$  MTBF (156 kb) in the dRICH system (1248 RDOs): > 3.6 min

BRAM:  $\sigma_{SEU}=(1.78\pm0.23)\cdot10^{-15}\frac{cm^2}{bit}$  MTBF (5.1 Mb) in the dRICH system (1248 RDOs): 2.1 min

SEU cross sections and MTBFs (33 Mb) in the dRICH system (1248 RDOs) for CRAM :

|       | $\sigma_{\text{SEU}} \left( 10^{-16} \frac{\text{cm}^2}{\text{bit}} \right)$ | MTBF<br>(min) |

|-------|------------------------------------------------------------------------------|---------------|

| COR   | $(1.96 \pm 0.25)$                                                            | 2.9           |

| UNCOR | $(3.09 \pm 0.94) \cdot 10^{-1}$                                              | 18            |

| TOTAL | $(2.30 \pm 0.28)$                                                            | 2.5           |

## RDO firmware progresses (I)

32

- pin placement for layout design

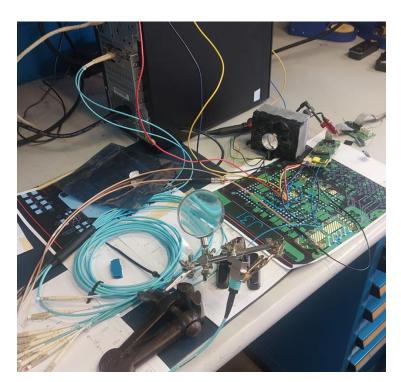

- intense use of <u>ALINX AUX15P evb card</u> (same FPGA) as RDO GYM (waiting for real cards!)

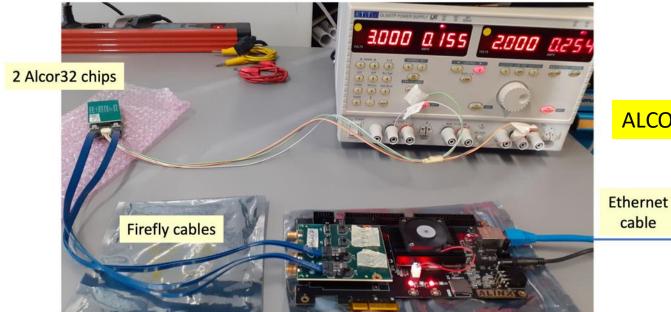

**ALCOR readout via AUX15P**

Alinx + FMC breakout board

In order to test the Artix – Alcor interface, we implemented the IPbus firmware on the FPGA. Now we can program the Alcor registers via SPI and we can correctly receive the data

successfully ported KC705 FW (reading ALCOR) to AUX15P including SERDES More details in D. Falchieri's talk at Electronics and DAQ WG/eRD109 (May 2025)

## RDO firmware progresses (II)

- pin placement for layout design

- intense use of <u>ALINX AUX15P evb card</u> (same FPGA) as "RDO GYM" (waiting for real cards!

successfully implemented IPBUS communication over optical link (commercial SFP)  $\rightarrow$  configuration foreseen for test beam

"collecting pieces of the firmware needed on RDO"

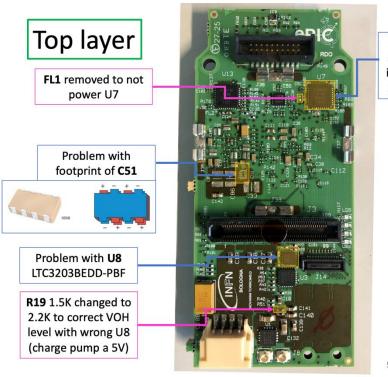

### initial debug on prototypes

initial debug included the fixing of several problems ("minor issues")

- mounted 2 Si5319 instead of a Si5319 and a Si5326 → we will do reworking

- mounted "wrong" charge pump component  $\rightarrow$  fixed changing some resistors, we will do reworking

- a short due to a capacitor (layout error): bypassed

- somehow difficult the pairing of VTRX+ MT connector with MPO and then with fibers (we had initially the wrong fanout patchcord)

details

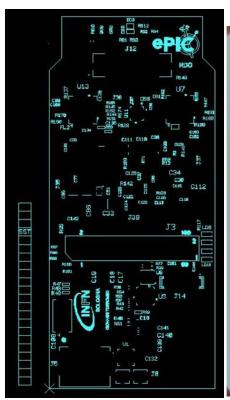

## initial debug details

U7 Si5319 instead Si5326

R34 15K changed with 8.2K to set 1.2V lout limit

Works the LCO resonan current and convert the current bad to voltage for ACC ATtry

MOREY MOREY MAY Set 0,500 A resonance 0,52A Volta-2 LBV Set-0,514A resonance 0,

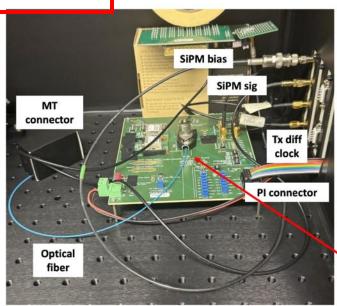

## checking the optical link

#### first ping to dRICH RDO via VTRX+

#### which firmware flavour in ePIC?

| Flavour        | Link Wrapper                           | Decoders                                                                                                     | Encoders                                                                 | Remarks                                                                                                                                                                                                                                                                                                                                            |

|----------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0: GBT         | GBT                                    | 8b10b 8.4.13<br>HDLC 8.4.14<br>Direct 8.4.16<br>TTCToHost 8.4.17<br>BusyToHost 8.4.18                        | 8b10b 8.5.11<br>HDLC 8.5.12<br>Direct 8.5.13<br>TTC 8.5.14               | The GBT mode flavour is available in 8 and 24 channel versions, with a complete set of encoders / decoders, and a so called SemiStatic configuration where some decoders/encoders are left out. FELIX aims to provide a 24 channel fully configurable version for FLX712, it has been demonstrated to work but with high resource count (78% LUTs) |

| 1: FULL        | ToHost FULL,<br>FromHost GBT or<br>LTI | FULL 8.4.15<br>TTCToHost 8.4.17<br>BusyToHost 8.4.18                                                         | 8b10b 8.5.11<br>HDLC 8.5.12<br>Direct 8.5.13<br>TTC 8.5.14<br>LTI-tx 8.6 | The FULL mode flavour is available in 24 channels for FLX712 and FLX128. The ToHost side/decoding is using 9.6Gb/s 8b10b data without logical links. FromHost/encoding is identical to GBT, with an option to transmit a copy of the LTI-TTC link data at 9.6Gb 8b10b with additional fields for XOFF                                              |

| 2: LTDB        | GBT                                    | 8b10b 8.4.13<br>HDLC 8.4.14<br>Direct 8.4.16<br>TTCToHost 8.4.17<br>BusyToHost 8.4.18                        | 8b10b 8.5.11<br>HDLC 8.5.12<br>Direct 8.5.13<br>TTC 8.5.14               | LTDB mode is a 48 channel version of GBT mode, but with reduced e-link configurability. This flavour only includes the EC and IC e-links, as well as an AUX e-link (Egroup 4, link 7) with HDLC/8b10b/Direct configuration. Additionally TTC distribution is available on all FromHost/ToFrontend e-links.                                         |

| 4: PIXEL       | lpGBT                                  | HDLC (EC/IC)<br>8.4.14<br>Aurora 8.4.11<br>TTCToHost 8.4.17<br>BusyToHost 8.4.18                             | RD53A/B 8.5.8<br>TTC 8.5.14<br>HDLC (IC/EC)<br>8.5.12                    | The Pixel flavour was designed to read out the ITk Pixel detector over IpGBT with Aurora e-links. The encoder uses a custom protocol for RD53 and includes a trigger and command state machine.                                                                                                                                                    |

| 5: STRIP       | lpGBT                                  | HDLC (IC) 8.4.14<br>Endeavour (EC)<br>8.4.10<br>8b10b 8.4.13, 8.4.9<br>TTCT0Host 8.4.17<br>BusyToHost 8.4.18 | HDLC (EC) 8.5.12<br>Endeavour (EC)<br>8.5.7<br>LCB 8.5.9<br>R3L1 8.5.10  | The Strip flavour was designed to read out the ITk Strip detector over lpGBT with 8b10b e-links. The encoder uses a strip custom protocol with so called trickle merge.                                                                                                                                                                            |

| 9: LPGBT       | lpGBT                                  | HDLC (EC/IC)<br>8.4.14<br>8b10b 8.4.13<br>Direct 8.4.16<br>TTCT0Host 8.4.17<br>BusyToHost 8.4.18             | 8b10b 8.5.11<br>HDLC 8.5.12<br>Direct 8.5.13<br>TTC 8.5.14               | The IpGBT Flavour is the IpGBT equivalent of the GBT flavour. It involves 8b10b, HDLC and TTC protocols and the aim is to have a fully configurable 24 channel build available. The LPGBT flavour will include encoding and decoding schemes for the HGTD                                                                                          |

| 10: INTERLAKEN | 64b67b                                 | ToHost Interlaken,<br>FromHost LTI<br>8.4.19                                                                 | LTI-tx 8.6                                                               | The Interlaken Flavour has 24x 25.78125 Gb/s Interlaken links in ToHost direction. Note that no more than 12 links can be fully occupied as otherwise the PCIe Gen4 bandwidth will be saturated. As encoders, the Interlaken flavour implements the TTC-LTI encoder, a copy of the received LTI frame but with additional XOFF bits.               |

Table of available link "flavours" in FELIX cards and FPGA resources usage (courtesy by A. Lonardo)

FPGA resource usage

|                      |      | KU115   | VM1802  | VP1552 |

|----------------------|------|---------|---------|--------|

| GBT 24 channel       | LUT  | 80.65%  | 69.60%  | 35.71% |

|                      | FF   | 77.03%  | 50.94%  | 26.13% |

|                      | BRAM | 70.00%  | 89.45%  | 34.04% |

|                      | URAM |         | 62.20%  | 22.14% |

| FULL 24 channel      | LUT  | 52.59%  | 44.35%  | 22.75% |

|                      | FF   | 38.40%  | 33.21%  | 17.03% |

|                      | BRAM | 40.46%  | 20.99%  | 7.99%  |

|                      | URAM |         | 62.20%  | 22 14% |

| LPGBT 24 channel     | LUT  | 112.51% | 82.94%  | 42.55% |

|                      | FF   | 52.39%  | 38.62%  | 19.81% |

|                      | BRAM | 68.94%  | 79.52%  | 30.26% |

|                      | URAM |         | 62.20%  | 22.14% |

| PIXEL 24 channel     | LUT  | 82.40%  | 60.75%  | 31.17% |

|                      | FF   | 62.04%  | 45.74%  | 23.46% |

|                      | BRAM | 81.20%  | 62.25%  | 23.69% |

|                      | URAM |         | 62.20%  | 22.14% |

| STRIP 24 channel     | LJJ  | 67.04%  | 49.42%  | 25.35% |

|                      | FF   | 49.94%  | 36.81%  | 18.88% |

|                      | BRAM | 121.43% | 104.45% | 39.75% |

|                      | URAM |         | 145.14% | 51.65% |

| INTERLAKEN 8 channel | LUT  |         | 9.15%   | 4.69%  |

|                      | FF   |         | 7.89%   | 4.05%  |

|                      | BRAM |         | 40.43%  | 15.39% |

|                      | URAM |         | 0.00%   | 0.00%  |

Table 5.2: Resource utilization for all firmware flavours estimated for the

Note dRICH aims to use FLX-155 resources too for data reduction!

See A. Lonardo talk at ePIC Jan 2025 meeting

#### **Update:**

Rome1/2 has now the FLX-182 sent by BNL up and running!

- scale up to 48 lpGBT links might be a problem for FLX-155?

- as dRICH we use just the VTRX+ tranceiver not the lpGBT ASIC so lpGBT protocol not strictly needed but we would recommend to use anyway one of the existing flavour. FULL will be tested, agreement within ePIC

#### scale up to a test beam up to 2 kchannels

DAQ and DCS computers

auxiliary control electronics crates

gigabit ETH switch for DAQ and DCS

low voltage and high voltage power supplies

dRICH prototype on the T10 beam line at CERN-PS in October 2023 dRICH prototype SiPM photodetector readout box DAQ FPGAs and clock distribution 53.0 SiPM at low temperature

11 KC705 FPGA boards in parallel → 64 AlCOR chips → 2048 SiPMs

next step is bringing readout inside the PDU (RDO comes after)

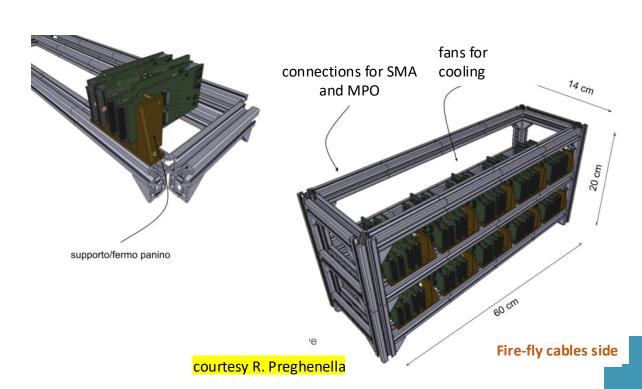

## RDO setup for 2025 test beam (Nov. 2025)

- we use IPBUS protocol over VTRX+ with SFP NIC cards on receiving end

- "fake-FEB" (ALCOR v2.1 adaptor): two FireFly connectors to reach existing FEB (with 2 ALCOR v2.1)

## RDO next steps preparing for test beam 2025

- External clock processed by SI5326 (note: we need 16 SMA-UFL cables)

- 2. Readout of all I<sup>2</sup>C sensors