# ePIC Electronics & DAQ WG DAQ Protocol discussion

ePIC DAQ meeting

Filippo Costa (CERN/ALICE)

# I will share my experience in ALICE, as firmware developer and detector readout expert.

I will go through some details of the GBT and IpGBT protocol in FPGA.

Challenges in DAQ operations concerning:

- Support.

- Debug.

- Code maintainability.

- slow and fast control.

With the risk to sound obvious I will cover some topics that I consider important at this stage of the development.

If I sound obvious, I apologize for that.

## Agenda

## Filippo Costa

#### STAFF at CERN since 2008

- DETECTOR READOUT EXPERT

- ALICE SW RELEASE COORDINATOR

#### Development:

- Software and firmware developer for DAQ readout card.

- Experience in fw development for readout cards:

- CRORC XILINX VIRTEX 6 (old project still running on ISE)

- CRU ALTERA ARRIA X

- FELIX-182/155 (WIP)

- Software, python tools to configure and monitor the card.

#### Coordination and support

- Responsible for the detector readout activities in ALICE.

- ALICE Software Release Coordinator.

# ALICE OVERVIEW and LESSONS LEARNED FROM THE PAST.

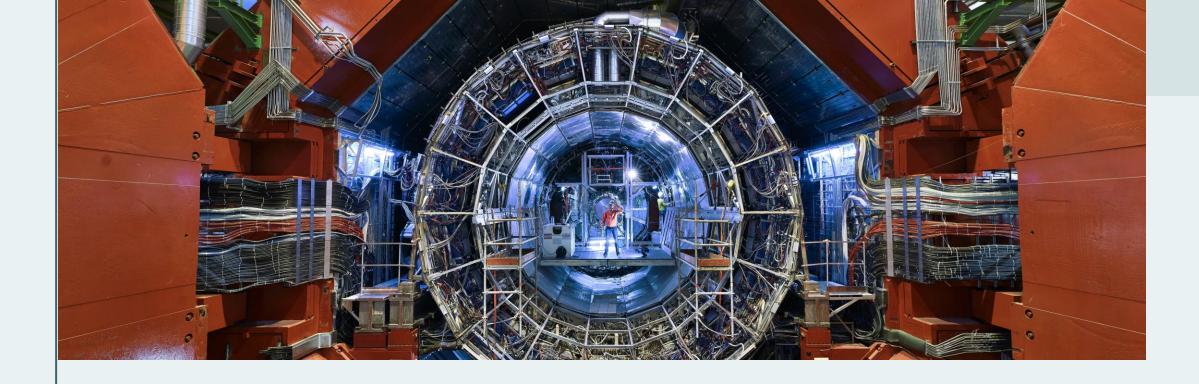

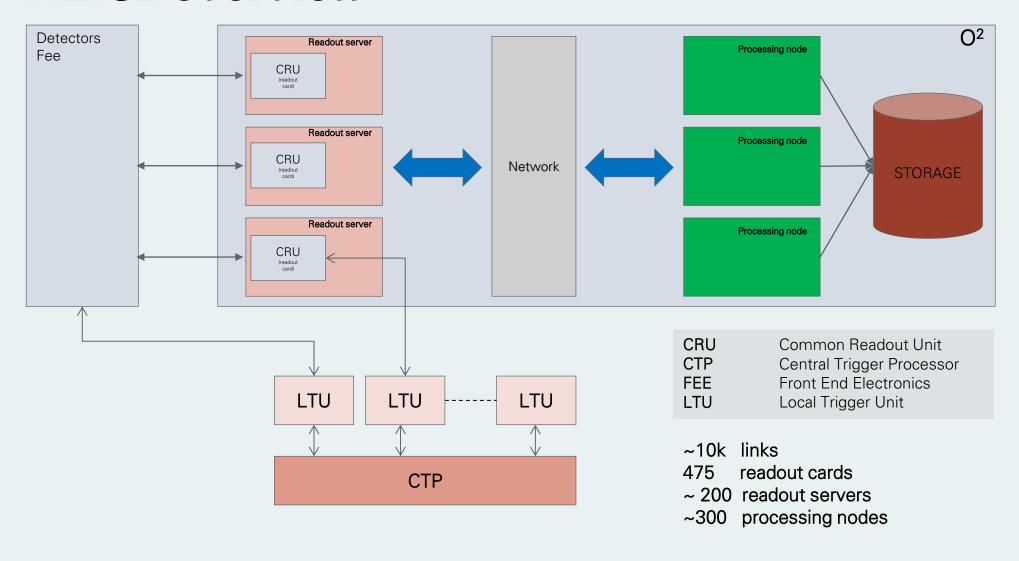

## **ALICE** overview

## **ALICE** overview

## What we learned from the past

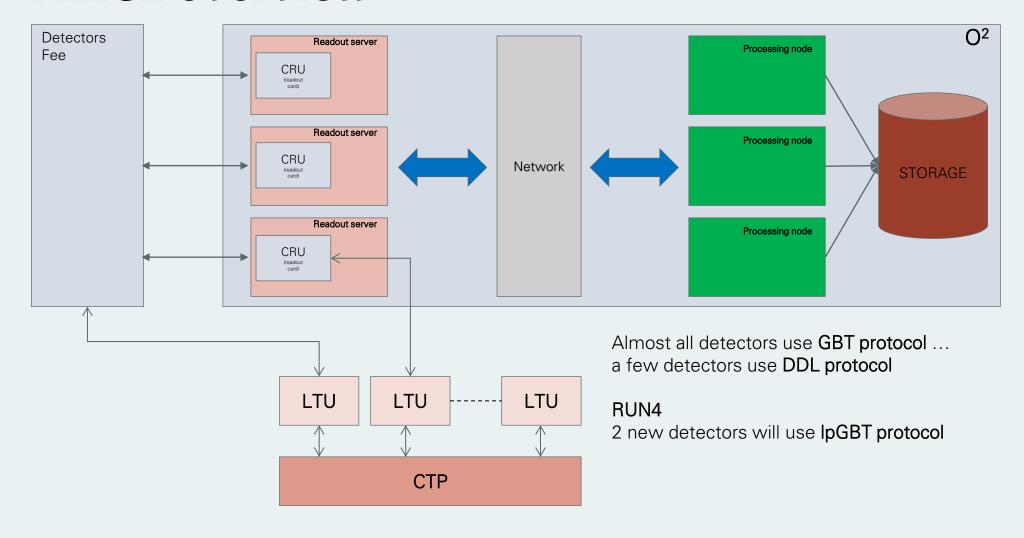

#### Why did we start RUN3 using different link protocols?

- Hard requirement, not a DAQ choice !!!

- Some detectors could not upgrade their front-end electronics.

#### Challenges in integrating the old protocol into the new system.

- The new continuous readout system was designed around the flexibility of the GBT protocol, enabling parallel operations (slow control, clock recovery, and data transfer).

Integrating the legacy protocol required substantial adaptation and introduced operational limitations.

- Significant modifications were needed to make the old protocol compatible with the new software and higher data rates, as it was not originally designed for such performance.

- Most of the issues coming from the chain using the old protocol were not reproducible by other systems or in the lab and they required intense debug session in production.

## What we learned from the past

Challenges will not come only from protocol implementation. They will also arise from (technical/coordination issues):

- Firmware and software verification.

- Deployment in production.

- Coordination among experts working on different features.

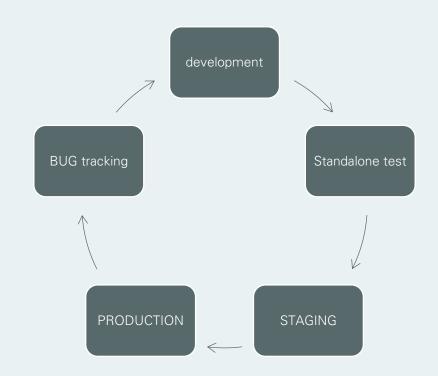

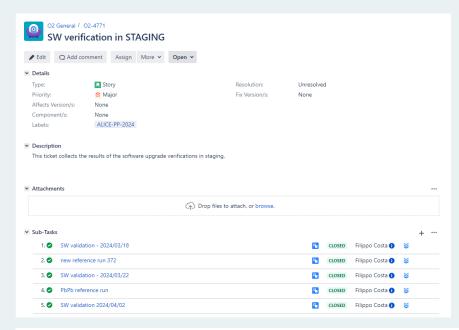

# ALICE sw deployment in 2022

## ALICE sw deployment in 2025

We deploy and verify the sw in production in less than 1h with a success rate of 99%.

- Development

- experts develop the new feature.

- Standalone test

- experts verify the new feature in their test system.

- STAGING

- the new sw is deployed in STAGING and tested.

- PRODUCTION

- if STAGING test is passed the new feature is validated in PRODUCTION.

- BUG tracking

- if there are new issues, tickets are opened and assigned to experts.

| Issue                             | Assignee      | Reporter          | Priority       | Status | Resolution | Created ↓ |

|-----------------------------------|---------------|-------------------|----------------|--------|------------|-----------|

| $\Sigma$ Summed Values            |               |                   |                |        |            |           |

| ✓ <del>02~4813</del> O2 sw update | Filippo Costa | Filippo Costa     | <b>₩</b> Minor | CLOSED | DONE       | 01/Apr/24 |

| <del>○ ○2-4788</del> O2 sw update | Filippo Costa | Filippo Costa     | <b>₩</b> Minor | CLOSED | DONE       | 22/Mar/24 |

| <del>○ 02-4762</del> O2 sw update | Filippo Costa | Filippo Costa     | <b>₩</b> Minor | CLOSED | DONE       | 14/Mar/24 |

| <del>○ 02-4736</del> O2 sw update | Filippo Costa | Filippo Costa     | <b>¥</b> Minor | CLOSED | DONE       | 07/Mar/24 |

| <del>○ ○2-4704</del> O2 sw update | Filippo Costa | Filippo Costa     | <b>₩</b> Minor | CLOSED | DONE       | 28/Feb/24 |

| ✓ <del>D2~4690</del> O2 sw update | Filippo Costa | Filippo Costa     | <b>₩</b> Minor | CLOSED | DONE       | 26/Feb/24 |

| ✓ <del>O2=4662</del> O2 sw update | Filippo Costa | ilippo Costa      | <b>₩</b> Minor | CLOSED | DONE       | 15/Feb/24 |

| ✓ <del>O2~4653</del> O2 sw update | Filippo Costa | Filippo Costa     | <b>₩</b> Minor | CLOSED | DONE       | 13/Feb/24 |

| <del>O2−4610</del> O2 sw update   | Filippo Costa | iii Filippo Costa | <b>₩</b> Minor | CLOSED | DONE       | 30/Jan/24 |

| ✓ <del>02~4600</del> O2 sw update | Filippo Costa | ilippo Costa      | <b>₩</b> Minor | CLOSED | FIXED      | 25/Jan/24 |

| ✓ <del>D2-4454</del> O2 sw update | Filippo Costa | Filippo Costa     | <b>₩</b> Minor | CLOSED | DONE       | 01/Dec/23 |

| <del>○ 02-4432</del> O2 sw update | Filippo Costa | ilippo Costa      | <b>₩</b> Minor | CLOSED | DONE       | 27/Nov/23 |

| <del>○ ○2-4384</del> O2 sw update | Filippo Costa | Filippo Costa     | <b>₩</b> Minor | CLOSED | DONE       | 16/Nov/23 |

| <del>○ ○2-4347</del> ○2 sw update | Filippo Costa | Filippo Costa     | <b>₩</b> Minor | CLOSED | DONE       | 08/Nov/23 |

| ▼ Description                        |                                                                 |                       |

|--------------------------------------|-----------------------------------------------------------------|-----------------------|

| SW update JIRA: https://its.cern.ch/ | ſjira/browse/O2-4813                                            |                       |

| COMPONENT                            | NOTE/VERSION                                                    |                       |

| FLP                                  | 1.26.0                                                          |                       |

| PDP                                  | O2PDPSuite/epn-20240329-DDv1.6.4-QCv1.139.0-flp-suite-v1.26.0-1 |                       |

| СТР                                  | ctp: 23_01 ltus: 22_02 sw:32.1.8                                |                       |

| QC                                   | 1.139                                                           |                       |

| DETECTOR                             | QC layout (validation)                                          | QC layout (reference) |

| CPV                                  | validation - run 419                                            | reference - run 372   |

| EMC                                  | validation - run 419                                            | reference - run 372   |

| FDD                                  | validation - run 419                                            | reference - run 372   |

| FT0                                  | validation - run 419                                            | reference - run 372   |

| FV0                                  | validation - run 419                                            | reference - run 372   |

| HMP                                  | validation - run 419                                            | reference - run 372   |

| ITS                                  | validation - run 419                                            | reference - run 372   |

| MCH                                  | validation - run 419                                            | reference - run 372   |

| MFT                                  | validation - run 419                                            | reference - run 372   |

| MID                                  | validation - run 419                                            | reference - run 372   |

| PHS                                  | validation - run 419                                            | reference - run 372   |

| TPC                                  | validation - run 419                                            | reference - run 372   |

| TOF                                  | validation - run 419                                            | reference - run 372   |

| TRD                                  | validation - run 419                                            | reference - run 372   |

| ZDC                                  | validation - run 419                                            | reference - run 372   |

|                                      |                                                                 |                       |

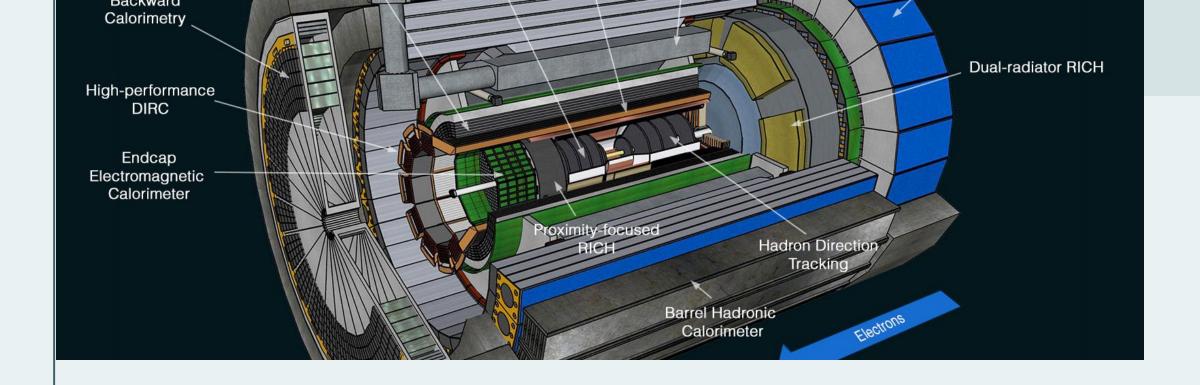

## ePIC OVERVIEW and some considerations.

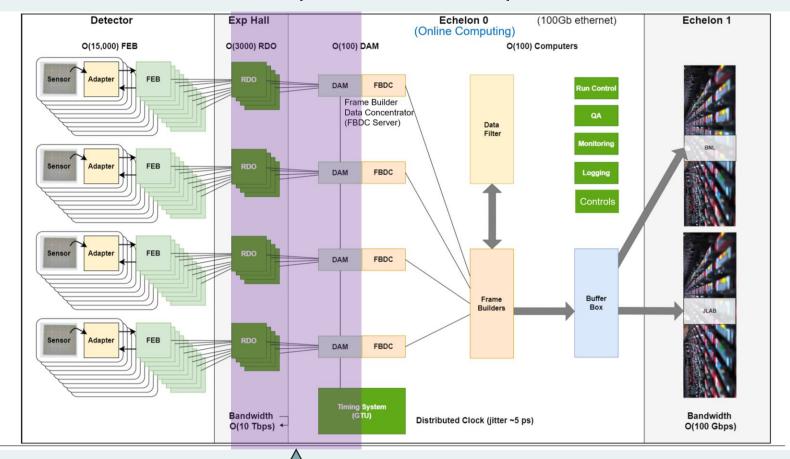

## ePIC DAQ framework (overview)

#### **EIC Specs**

- Bunch Crossing ~10.2 ns (98.5 MHz)

- Interaction Rate

~ 2 us (500 kHz)

(one interaction per ~200 bunch crossings)

- · High Luminosity

- -- up to 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>

- Low occupancy physics signal

- Background and noise significant for some sub-systems

Readout links I will focus on this part

# ePIC DAQ readout links (~4K)

### **Summary of Channel Counts and Data Flow**

Charge 1

| Detector        |          |               | Channels      |             |                   | Det           | Det         | RDO      | Fiber         | DAM             | Data                      | Data                             |

|-----------------|----------|---------------|---------------|-------------|-------------------|---------------|-------------|----------|---------------|-----------------|---------------------------|----------------------------------|

| Group           | MAPS     | AC-LGAD       | SiPM/PMT      | MPGD        | HRPPD/<br>MCP-PMT | Fiber<br>Down | Fiber<br>Up |          | Pair<br>(DAQ) |                 | Volume<br>(RDO)<br>(Gb/s) | Volume<br>(To<br>Tape)<br>(Gb/s) |

| Tracking (MAPS) | 16B      |               |               |             |                   | 187           | 4976        | 323      | 323           | 7               | 15                        | 15                               |

| Tracking (MPGD) |          |               |               | 164k        |                   | 640           | 2560        | 160      | 160           | 5               | 27                        | 5                                |

| Calorimeters    | 500M     |               | 100k          |             |                   |               |             | 522      | 522           | 17              | 70                        | 17                               |

| PID (TOF)       |          | 6.1M          |               |             |                   | 500           | 1364        |          | 1364          | 30              | 50                        | 12                               |

| PID Cherenkov   |          |               | 318k          |             | 143k              | 1334          | 1334        | 1242     | 1334          | 33              | 1275                      | 32                               |

| Far Forward     |          | 1.5M          | 10k           |             |                   |               |             | 80       | 80            | 6               | 36                        | 12                               |

| Far Backward    | 66M      |               | 3.4k          |             |                   |               |             | 25       | 289           | 11              | 37                        | 8                                |

| Lumi            |          | 128k          | 5.1k          |             |                   |               |             | 41       | 41            | 4               | 264                       | 8                                |

| Polarimetry     |          | Independent E | lectronics, [ | DAQ, & Cont | rols from centi   | ral detec     | tor but exp | ected to | build or      | same te         | chnologies                | 5                                |

| TOTAL           | 16.6B    | 7.7M          | 432k          | 164k        | 143k              | 2,661         | 10,234      | 2,393    | 4,113         | 113             | 1,774                     | 109                              |

| Summary o       | f Data F | Tow           | Copper        | RDO         | Fiber             | DAN           | PCI/        | Eth      |               | adout<br>nputer | Eth                       | <b>\</b>                         |

| Aggregate       |          | 2.0 Tb/sec    |               |             |                   |               | Aggregate   | ,        | 1             | 15 Gb/s         | ес                        |                                  |

| Noise           |          | 1.6 Tb /sec   | /             |             |                   |               | Collision S | ignal    | 6:            | 2 Gb/sec        | ;                         |                                  |

| Signal from Phy | /sics +  | 400 Gb / sec  |               |             |                   |               | Synchrotro  | n Rad    | 6             | Gb/sec*         |                           |                                  |

| Background      |          |               |               |             |                   |               | Electron B  |          |               | .5 Gb/se        |                           |                                  |

|                 |          | Aggregate     |               | 2.0 Tb/sec  |                   |               | Hadron Be   | am       | 1.            | .0 Gb/se        | С                         |                                  |

#### Scale of the system:

- Electronics

- ~ 25 detector subsystems

- ~ 5 Readout Technologies

- ~ 2500 RDOs (on detector/in racks)

- ~ 110 DAM boards (DAQ room)

- CTU (with interface boards)

- Maximum Data Volume

- ~ 2 Tb/sec digitized

- ~ 115 Gb/sec recorded

- Online Computing (Echelon 0)

- ~200 nodes (DAQ Room/SDCC)

#### Synchrotron radiation caveats

41 Gb/sec

- Rates are based upon hit rate for all ePIC detectors. In fact, data volumes depend upon specific detector hit (64 bits/hit assumed)

- Highest Synchrotron radiation / electron beam gas will correspond to lower values for collision signal

- 3. Plan to analyze by component soon

#### **ACRONIMS:**

- RDO: DAO readout FEE interface (aggregator card)

- **DAM** : FELIX-155

Fiber Pair (DAQ)

323

160

522

1364

1334

80

289

41

build on

4,113

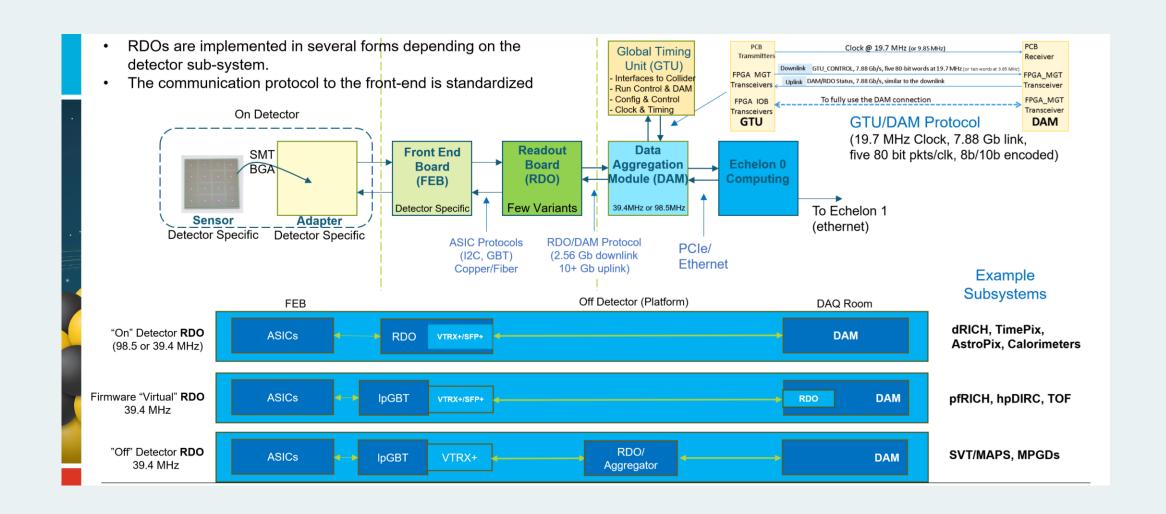

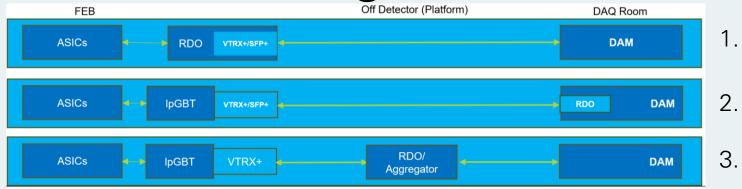

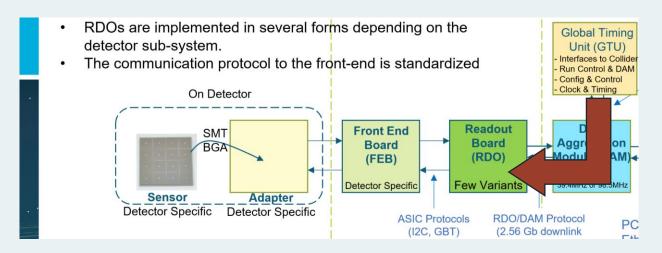

## DAM control and readout chain options

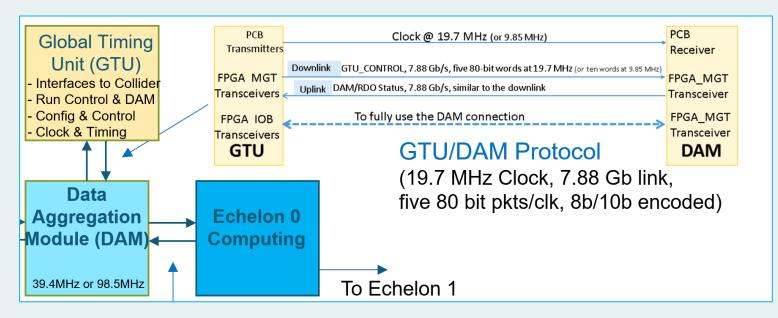

## GTU and DAM communication

# Global Timing Unit (GTU)

- Interfaces to Collider

- Run Control & DAM

- Config & Control

- Clock & Timing

Responsibilities and Challenges of the GTU

#### Multiple Core Functions:

- Acts as the **interface to the machine** to recover the machine clock.

- Handles Run Control starts and stops data taking for the DAM.

- Manages Configuration and Control of the DAM and/or Front-End Electronics (FEE).

- Provides **Clock and Timing distribution** to ensure synchronized operation across the system.

#### Key Challenge:

- Concentrating all these critical tasks in a **single entity** increases complexity and risk.

- The GTU's firmware must remain **stable and rarely changed**, since it's responsible for **delivering precise** and reliable clock and timing signals to the entire system.

## Who does What?

# Global Timing Unit (GTU)

- Interfaces to Collider

- Run Control & DAM

- Config & Control

- Clock & Timing

GTU is a sensitive component in charge to deliver clock and triggers to the whole experiment.

Every changes in the firmware might bring:

- New timing.

- Instability in the system.

- Clock stability is directly connected to the FEE link stability.

- Run control and DAM configuration often requires access to large database.

- It is important that you change this firmware as little as possible.

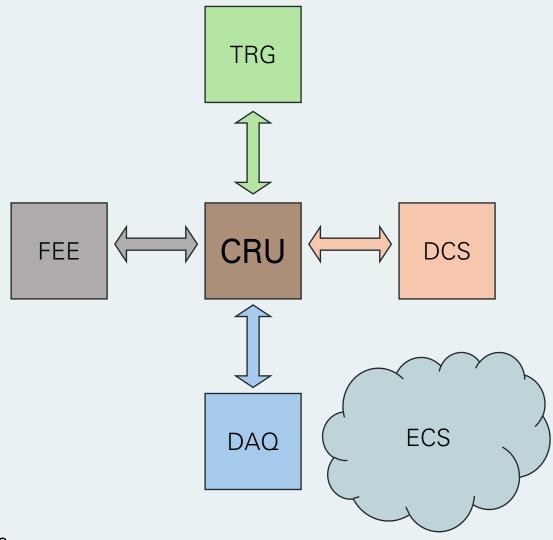

## ALICE central systems

#### TRG

- Clock and trigger.

#### DCS

- Slow control information.

#### DAQ

- Card configuration and data taking.

#### ECS (Experiment Control System)

- Coordinates all the components to start in the correct order:

- 1. DCS (FEE configuration).

- 2. DAQ (readout card con.

- 3. TRIGGER.

- 4. FEE start to generate data.

## Readout Configurations

ePIC is evaluating three different readout configurations.

#### Option 2:

The link protocol is clearly defined. It uses lpGBT or an FPGA-based implementation on the readout card. The connection with the readout system is therefore well established.

Already provides protocols for data delivery, slow control, and trigger communication between the FEE and the readout card.

#### Options 1 and 3:

The link protocol is not yet defined.

This uncertainty will have a **major impact** on implementing other essential protocols, such as **slow control** and **trigger information transfer**.

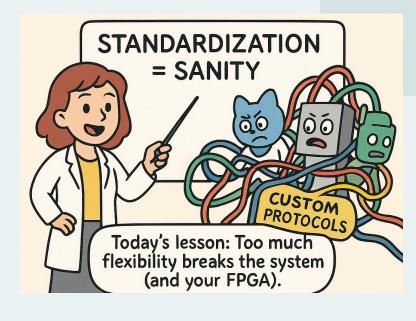

## Impact of Link Protocol Flexibility

High flexibility in link protocols introduces several challenges:

- Increases implementation complexity.

- Reduces issue reproducibility and complicates code maintenance.

- Affects FPGA resource utilization across different designs.

#### Recommendation:

Standardize communication protocols between the FEE and DAQ as much as possible.

Adopt different or custom approaches only when specific requirements justify the deviation.

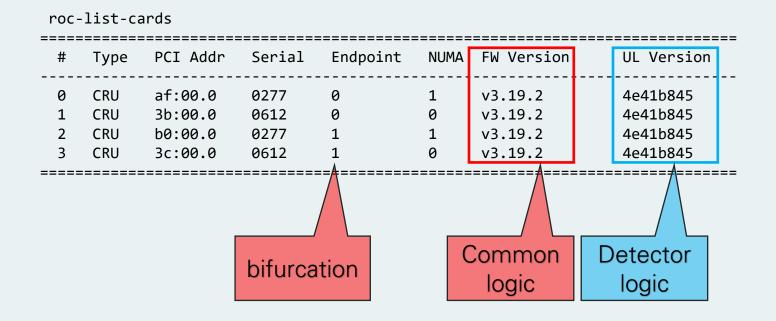

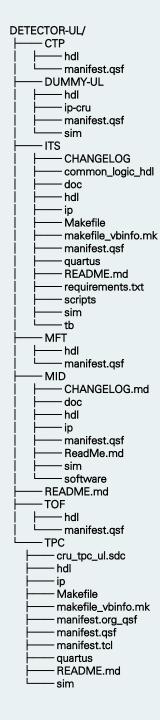

## Flavors of firmware

#### The DAM FIRMWARE is YOUR responsibility !!!!

The RDO in the DAM implies that detector firmware will be implemented in the general framework of the DAM. You need to put in place a strategy to compile and test the different firmware flavors:

- Git submodules.

- Fw versions to compile (different versions can generate different results).

- Timing errors !!!

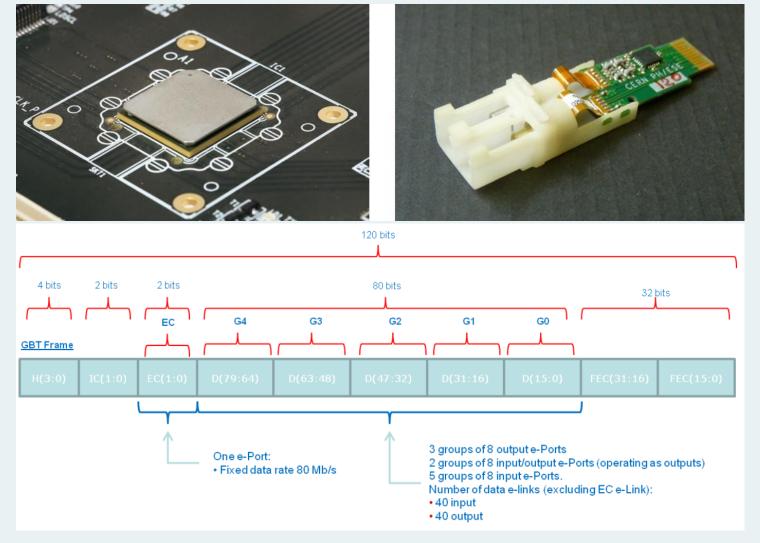

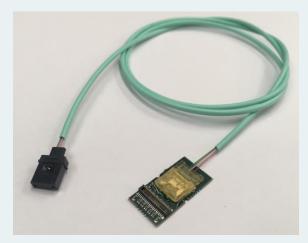

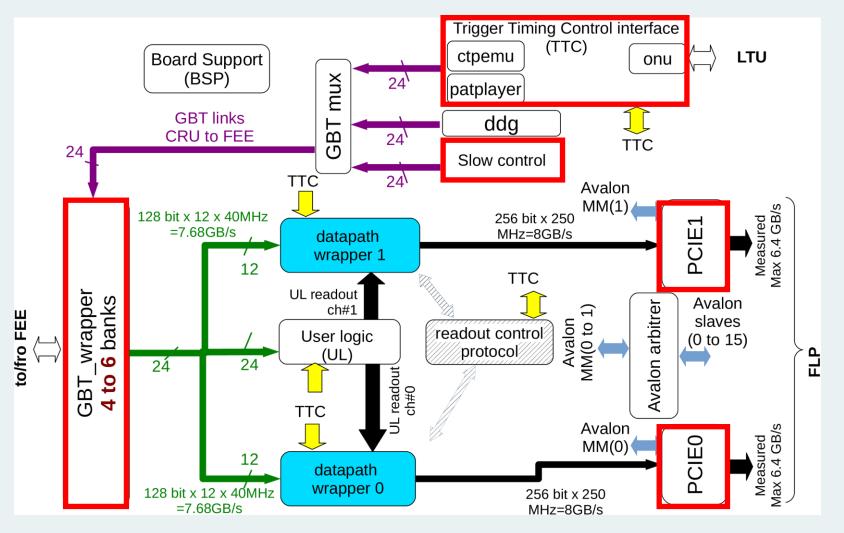

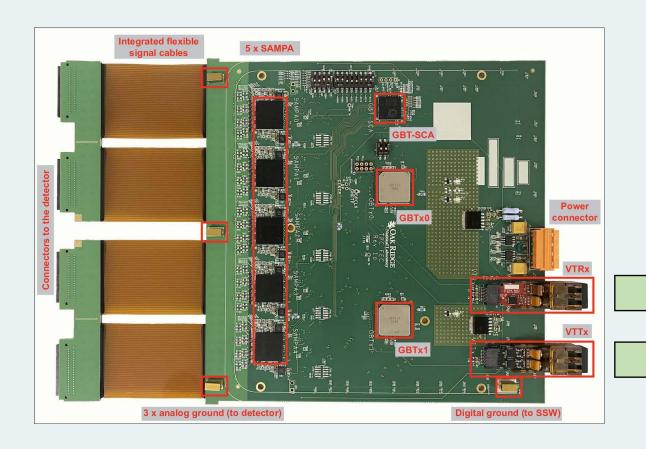

## DAQ protocols (GBT VTRX)

Line rate 120 bit @ 40MHz = 4.8 Gb/s

- 80 bit \* 40 MHz = 3.2 Gb/s

- 112 bit \* 40 MHz = 4.48 Gb/s

- 4 bit of SC (IC/EC)

- IC: used to configure the GBT chip.

- EC: requires SCA chip (provides general I/O and I2C interfaces).

- ALICE SWT protocol (80 bit of DATA are used).

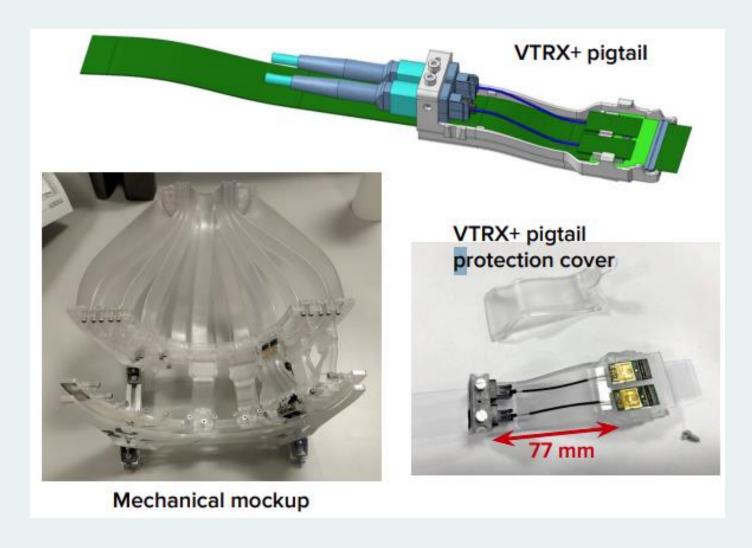

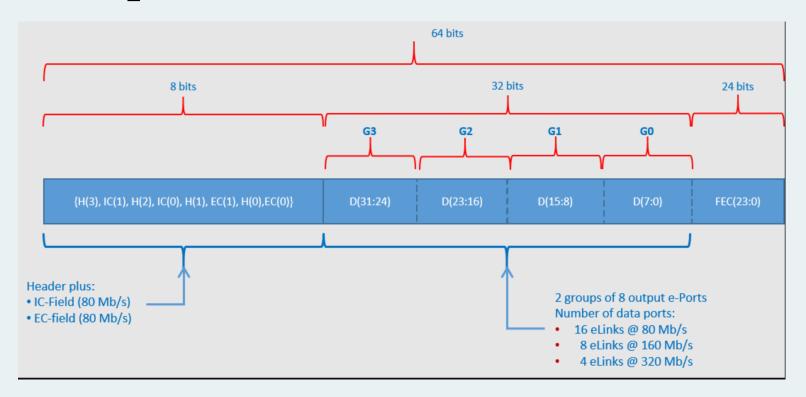

# DAQ protocols (lpGBT VTRX+)

## DAQ protocols (DAM to RDO)

Line rate 64 bit @ 40 MHz = 2.560 Gb/s DATA rate 32 bit @ 40 MHz = 1.280 Gb/s

# DAQ protocols (RDO to DAM)

|                   | 5.1  | L2 Gbps    | 10.24 Gbps |       |  |

|-------------------|------|------------|------------|-------|--|

| Field             | FEC5 | FEC5 FEC12 |            | FEC12 |  |

| Frame [bits]      |      | 128        | 256        |       |  |

| Header [bits]     |      | 2          | 2          |       |  |

| IC [bits]         |      | 2          | 2          |       |  |

| EC [bits]         |      | 2          | 2          |       |  |

| D [bits]          | 112  | 112 96     |            | 192   |  |

| FEC [bits]        | 10   | 24         | 20         | 48    |  |

| LM [bits]         | 0    | 0 2        |            | 10    |  |

| Correction [bits] | 5    | 5 12       |            | 24    |  |

| # of eLink groups | 7    | 6          | 7          | 6     |  |

#### ASYMMETRIC LINK RATE !!!

A lot of options available, do you need all of them? Reducing the choice will simplify the implementation in FPGA and the sw to configure the cards.

# GBT / lpGBT

|            | GBT            | Data width | lpGBT                    | Data width |

|------------|----------------|------------|--------------------------|------------|

| Upstream   | 3.2 Gb/s       | 80 bit     | 1.280 Gb/s               | 32 bit     |

| Downstream | (GBT) 3.2 Gb/s | 80 bit     | (5Gb/s FEC12) 3.84 Gb/s  | 96 bit     |

|            | (WB) 4.48 Gb/s | 112 bit    | (5Gb/s FEC5) 4.48 Gb/s   | 112 bit    |

|            |                |            | (10Gb/s FEC12) 7.68 Gb/s | 192 bit    |

|            |                |            | (10 Gb/s FEC5) 8.96 Gb/s | 224 bit    |

### HARDWARE SELF TEST !!!

In the CRU, we implemented several **self-test features** by placing the links in loopback mode. Since the TX and RX link rates were identical, the transmitted data could be read back and verified.

This allowed us to:

- Read back the trigger stream.

- Send data (simulating detector output) and read it back useful for stressing and validating the full dataflow.

- Verify the GBT test stream including counter and constant pattern checks.

These capabilities were extremely valuable to:

- Validate fiber installation.

- Check firmware functionality.

- Confirm proper FEE operation and clock recovery.

### Limitations with IpGBT

With IpGBT, most of these loopback-based features are no longer available, as TX-to-RX loopback is not supported.

Therefore:

Robust link and dataflow validation tools are essential. when failures arise, it becomes more challenging to isolate whether the issue originates from the readout card firmware or the detector FEE.

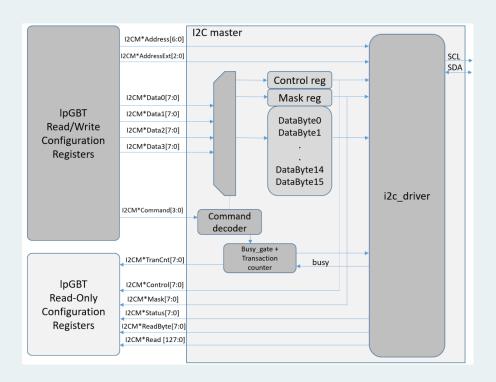

# Slow control protocol

The main benefit in using GBT-family protocol is the possibility to send different streams at the same time through 1 fiber:

- Clock.

- Data.

- Slow Control.

To use the SC capability of the GBT/lpGBT protocol you need to have the ASIC on the FEE.

The FPGA implementation is a "simple" parallel to serial interface.

## Virtual Vs Real world (HDL Vs ASIC)

lpGBT chip provides

- I2C masters

- General Purpose I/O

```

gbt_wrapper at base address 0x4_00_0000

cmp_gbt_wrapper : lpgbt_wrapper

generic map (

g_CLK_FREQUENCY => g_CLK_FREQUENCY,

g_LINKS_PER_BANK => g_LINKS_PER_BANK(15 downto 0),

g_NUM_GBT_LINKS => g_NUM_GBT_LINKS

-- User global clock

=> ttc_clk240_i.

ttc_clk240

ttc_tick

gbt_reset_tx

=> gbt_reset_tx,

gbt_reset_rx

=> gbt_reset_rx,

-- Transceiver signals

mgt_bank_refclk_i => gbt_refclk(3 downto 0),

serial_rx_i => gbt_rx(g_NUM_GBT_LINKS - 1 downto 0),

=> gbt_tx(g_NUM_GBT_LINKS - 1 downto 0),

-- GBT Downlink (CRU -> FE)

gbt_tx_ready_o => s_gbt_tx_ready(g_NUM_GBT_LINKS - 1 downto 0),

gbt_tx_bus_i => s_gbt_dl_bus(g_NUM_GBT_LINKS - 1 downto 0),

-- GBT Uplink (FE -> CRU)

gbt_rx_ready_o => s_gbt_rx_ready(g_NUM_GBT_LINKS - 1 downto 0),

gbt_rx_bus_0 => s_gbt_ul_bus(g_NUM_GBT_LINKS - 1 downto 0),

-- Avalon-MM Slave - PCIe BAR Read/Write access

=> SYSCLK,

=> CORE_RESET_2CK,

s0_reset_i

s0_waitrequest_o => sx_waitreq(4),

s0_address_i

=> sx_addr(4)(23 downto 0),

s0_read_i

s0_readdata_o

s0_readdatavalid_o => sx_rdval(4),

s0_write_i

=> sx wr(4).

s0_writedata_i => sx_wrdata(4)

```

IpGBT FPGA is a TX/RX SERDES interface.

The IC protocol used to communicate with the IpGBT ASIC works if you have the ASIC on the other side.

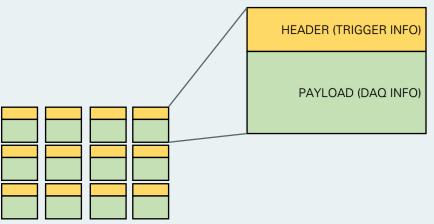

# Trigger protocol/path (ALICE example)

ALICE trigger information consists of 3 fields

- TTYPE = 32 bit

- BC = 16 bits

- ORBIT = 32 bits

The current assumption is that trigger information will follow the path GTU -> DAM -> RDO -> FEB. How large is ePIC trigger information?

In ALICE we use the GBT link from CRU to FEE to deliver clock and trigger.

- The trigger format relies on the protocol used to communicate with the FEE.

- GBT and lpGBT payloads (upstream) are different (32 bit Vs 80 bits), so changes in the trigger protocol for the lpGBT detectors are required.

# Continuous readout (triggerless) ...

If ALICE is continuous readout (triggerless) why do we talk about triggers?

For the dataflow we still need time markers to put data together:

- SOR (Start of Run)

- ALICE marks data between 2 ORBITS with a timestamp so we can put together data from different detectors generated at the same time. (1 ORBIT is 3564 bunch crossing)

ALICE trigger information consists of 3 fields

- TTYPE = 32 bit

- BC = 16 bits

- ORBIT = 32 bits

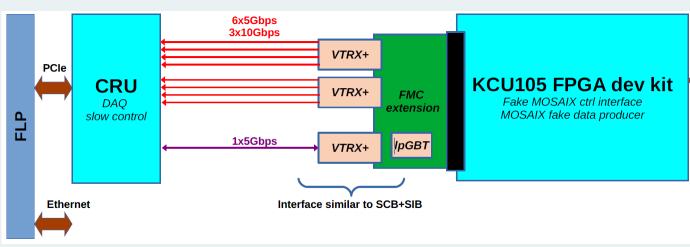

## Test bed systems

VLDB+ (CERN – ESE)

<a href="https://vldbplus.web.cern.ch/">https://vldbplus.web.cern.ch/</a>

#### KCU105 + FMC card (GRENOBLE)

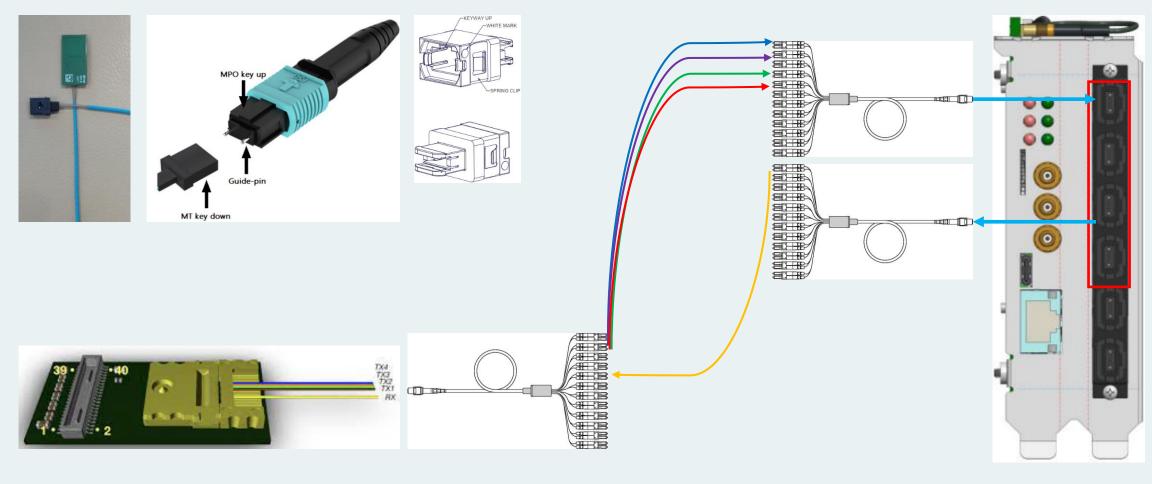

## Fiber connections

12 ch unidirectional

## FPGA resources utilization

## FPGA utilization

|                      |      | KU115   | VM1802  | VP1552  |

|----------------------|------|---------|---------|---------|

| GBT 24 channel       | LUT  | 80.65%  | 69.60%  | 35.71%  |

|                      | FF   | 77.03%  | 50.94%  | 26.13%  |

|                      | BRAM | 70.00%  | 89.45%  | 34.04%  |

|                      | URAM |         | 62.20%  | 22.14%  |

| FULL 24 channel      | LUT  | 52.59%  | 44.35%  | 22.75%  |

|                      | FF   | 38.40%  | 33.21%  | 17.03%  |

|                      | BRAM | 40.46%  | 20.99%  | 7.99%   |

|                      | URAM |         | 62.20%  | 22 1/1% |

| LPGBT 24 channel     | LUT  | 112.51% | 82.94%  | 42.55%  |

|                      | FF   | 52.39%  | 38.62%  | 19.81%  |

|                      | BRAM | 68.94%  | 79.52%  | 30.26%  |

|                      | URAM |         | 82.20%  | 22.14%  |

| PIXEL 24 channel     | LUT  | 82.40%  | 60.75%  | 31.17%  |

|                      | FF   | 62.04%  | 45.74%  | 23.46%  |

|                      | BRAM | 61.20%  | 62.25%  | 23.69%  |

|                      | URAM |         | 62.20%  | 22.14%  |

| STRIP 24 channel     | LUT  | 67.04%  | 49.42%  | 25.35%  |

|                      | FF   | 49.94%  | 36.81%  | 18.88%  |

|                      | BRAM | 121.43% | 104.45% | 39.75%  |

|                      | URAM |         | 145.14% | 51.65%  |

| INTERLAKEN 8 channel | LUT  |         | 9.15%   | 4.69%   |

|                      | FF   |         | 7.89%   | 4.05%   |

|                      | BRAM |         | 40.43%  | 15.39%  |

|                      | URAM |         | 0.00%   | 0.00%   |

Table 5.2: Resource utilization for all firmware flavours estimated for the

### CRU Firmware Resource Usage (focal\_tb branch, 24 lpGBT link)

| Quartus Prime Version<br>Revision Name      | 18.1.0 Build 222 09/21/2018 S.<br>cru | J Pro E | dition                           |                                  |                               |                           |

|---------------------------------------------|---------------------------------------|---------|----------------------------------|----------------------------------|-------------------------------|---------------------------|

| Top-level Entity Name<br>Family             | top_cru_lpgbt<br>Arria 10             | Fitte   | r Resource Utilization by Entity |                                  |                               |                           |

| Device                                      | 10AX115S3F45E2SG                      | Q <     | <filter>&gt;</filter>            |                                  |                               |                           |

| Timing Models Logic utilization (in ALMs)   | 147,442 / 427,200 ( 35 % )            |         | Compilation Hierarchy Node       | [A] ALMs used in final placement | Combinational ALUTs           | Dedicated Logic Registers |

| ctal registers                              | 269588                                | 1       | * I                              | 182264.8 (3.5)                   | 235470 (7)                    | 269584 (5)                |

| otal pins                                   | 370 / 960 ( 39 % )                    | 1       | ▶  auto_fab_0                    | 3246.5 (1.0)                     | 3301 (2)                      | 6171 (0)                  |

| otal virtual pins<br>otal block memory bits | 0<br>20,572,652 / 55,562 240 ( 37 °   | 2       | ▼  corecmp                       | 179014.8 (8.9)                   | 232162 (9)                    | 263408 (23)               |

| otal DEP Blocks                             | 0/1,518(0%)                           | 1       | busmux                           | 157.2 (157.2)                    | 261 (261)                     | 155 (155)                 |

| otal HSSI RX channels                       | 41 / 72 (57 %)                        | 2       | ▶  cmp_bsp                       | 3069.2 (0.0)                     | 4367 (0)                      | 4198 (0)                  |

| otal HSSI TX channels                       | 41 / 72 ( 57 % )                      | 3       | ▶  cmp_datapath0                 | 19078.4 (374.7)                  | 21618 (665)                   | 33236 (762)               |

| otal PLLS                                   | 59 / 144 ( 41 % )                     | 4       | ►  cmp_datapath1                 | 19205.0 (377.1)                  | 21018 (005)                   | 33580 (777)               |

| /                                           |                                       | 5       | ▶  cmp_gbt_wrapper               | 74897.0 (22.6)                   | 104028 (36)                   | 100092 (54)               |

| /                                           |                                       | 6       | ►  cmp_gbtsc_w                   | 24211.3 (043.4)                  | 20393 (54)                    | 36390 (2208)              |

| /                                           | 1                                     | 7       | ►  cmp_pciedma0                  | 16124.2 (0.0)                    | 22919 (0)                     | 23680 (0)                 |

| /                                           |                                       | 8       | ▶  cmp_pciedma1                  | 16077.7 (0.0)                    | 22745 (0)                     | 22654 (0)                 |

| /                                           | 35%                                   | 9       | ▶ [ttcpon_comp]                  | 6125.7 (152.6)                   | 8204 (187)                    | 9391 (350)                |

| 4 lpGBT +<br>6 PCle +                       | 3370                                  |         |                                  |                                  | The section of the section of | InGRT features:           |

ALMs = 74897 / 427200 (17.5%) ALUT8s = 104028 / 427200 (24.3%) FFs = 100092 / 1708800 (5.9%) Implemented IpGBT features:

- Dynamic 5.12 / 10.25 Gbp switch

- Fixed FEC12

1 PON

ARRIAX production year 2013

#### CRU firmware development (common)

- Firmware VHDL

- Test tools Python

- Production tools C/C++

- Driver in C and C/Python library to access the card

- Central GIT repository (firmware and software)

- https://gitlab.cern.ch/alice-cru/cru-fw.git

- <a href="https://gitlab.cern.ch/alice-cru/cru-sw.git">https://gitlab.cern.ch/alice-cru/cru-sw.git</a>

- Synthesis and firmware file generation via cmd line (make)

- Gitlab issues to keep track of new features

- Branching:

- Master/develop branch

- New feature, new branch from develop

- When feature is tested branch is moved back to develop

- When ready, develop is merged back to master and then tagged

#### CRU firmware development (common)

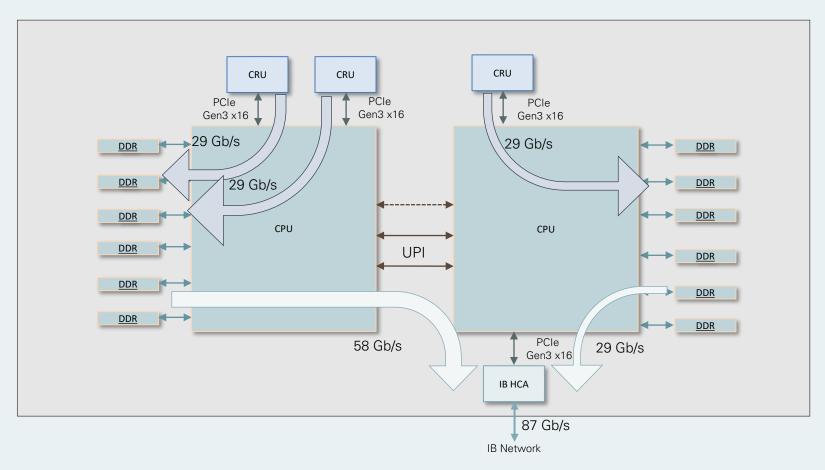

#### Memory access

Card position and memory channels equipped in the server, have an impact on the overall performances of the dataflow.

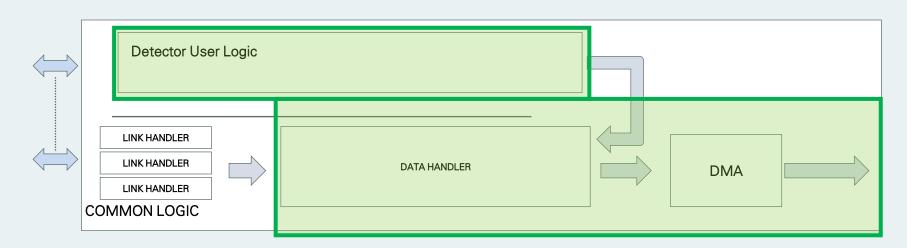

#### CRU firmware development (detector)

- DETECTOR LOGIC provided in GIT-SUBMODULE.

- CENTRAL firmware compiled including the DETECTOR LOGIC.

- Development flow:

- Detector experts develop logic and perform test in their lab.

- Central team compiles the firmware and checks timing results.

- Collaboration with detector experts is needed in case of errors in timing or dataflow.

#### Firmware components

#### ESE:

- GBT/lpGBT.

- TTCPON.

- Slow control.

ALTERA/XILINX: - DMA CORE.

All the other components have been specifically designed to satisfy ALICE data format requirements.

#### Data processing on the readout card

The following results represent my implementation-based assessment of optimal strategies for managing the ALICE dataflow, derived from practical experience rather than a universal reference model.

While other experiments may employ different approaches, these reflect design choices suited to their specific architectures and requirements, not incorrect solutions.

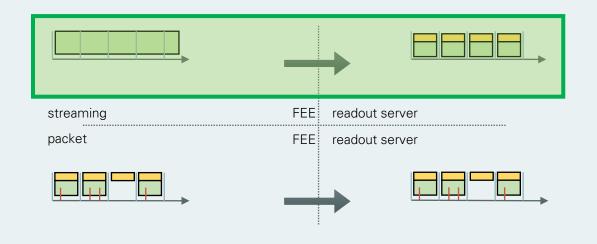

# Data processing on the readout card

Every detector in ALICE has a different FEE, that are readout by the same card

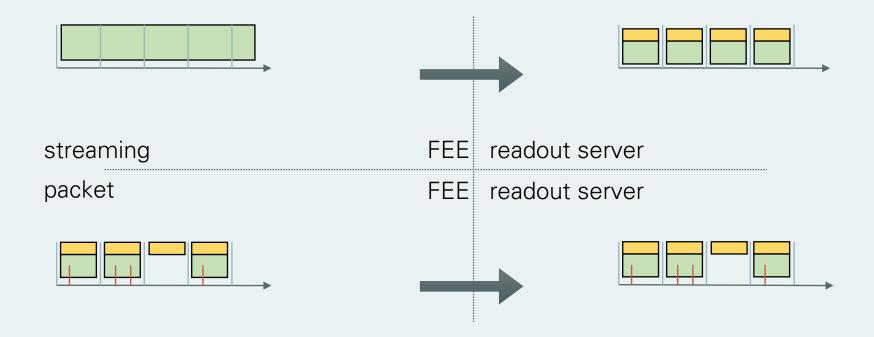

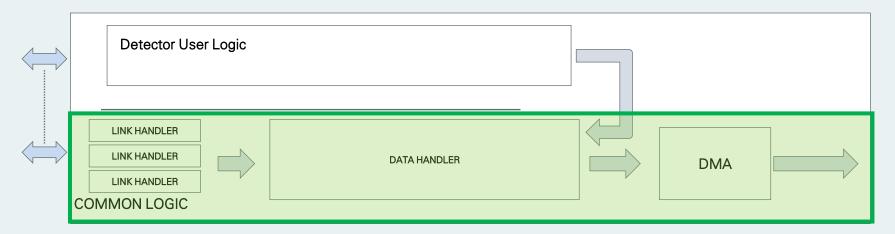

## FEE with ASIC/s (streaming data)

DATA

DATA

## FEE with FPGA/s (packet data)

## FEE with FPGA/s (packet data)

#### FEE with FPGA/s (packet data)

FIRMWARE in VHDL code. Operations on DATA:

- Check of protocol requirements.

- Data flow balancing.

- Monitoring.

- DMA.

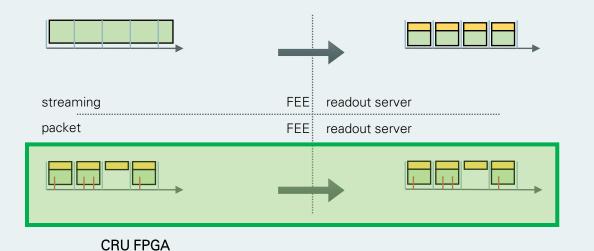

### FEE with FPGA/s (streaming data)

**CRU FPGA**

FIRMWARE in VHDL code. Operations on DATA:

- Detector specific code.

- Zero suppression.

- Data alignment/synchronization.

- ... data rate reduction.

#### Use of the DRAM

CRU doesn't have external buffer; the data flow relies on the memory of the server (easily accessible through DMA).

FELIX-155 is equipped with external RAM ... should you use it?

#### Use of the DRAM

- Data selection on FPGA?

- Data buffering?

- ... what else

#### REMEMBER:

- sw is faster to develop/maintain/debug than firmware

- Readout server is usually equipped with large amount of memory (cheaper and easy to access)

#### Final tips & takeaways

- STANDARDIZATION

- SEPARATION OF PROTOCOLS

- TEST BED

- HARDWARE SELF TEST

#### A few words of wisdom

- The best is the enemy of the good.

- Move fast and break things (and fix it soon). Do not wait too much for the perfect feature.

- Test is asap with the detectors and find out what works and what not.

- Invest time and money on testing facilities (STAGING).

- To ensure early issue detection, shared expertise, and system stability, all experts

must begin using the available DAQ system as soon as possible and rely on the same

readout chain rather than developing isolated, non-reproducible solutions on custom

hardware.

Filippo Costa filippo.costa@cern.ch

# Thank you