# Notes on bridge FPC: Towards a new iteration + AncAsic layout

M.Borri

### Target module design to date

Reference: James' talk on interconnection considerations: https://indico.bsnl.gov/event/25702/contributions/99824/attachments/58780/100945/24-11--6\_FPC\_AncAsicPlacement\_Bonding\_JJG\_ET\_r3.pdf

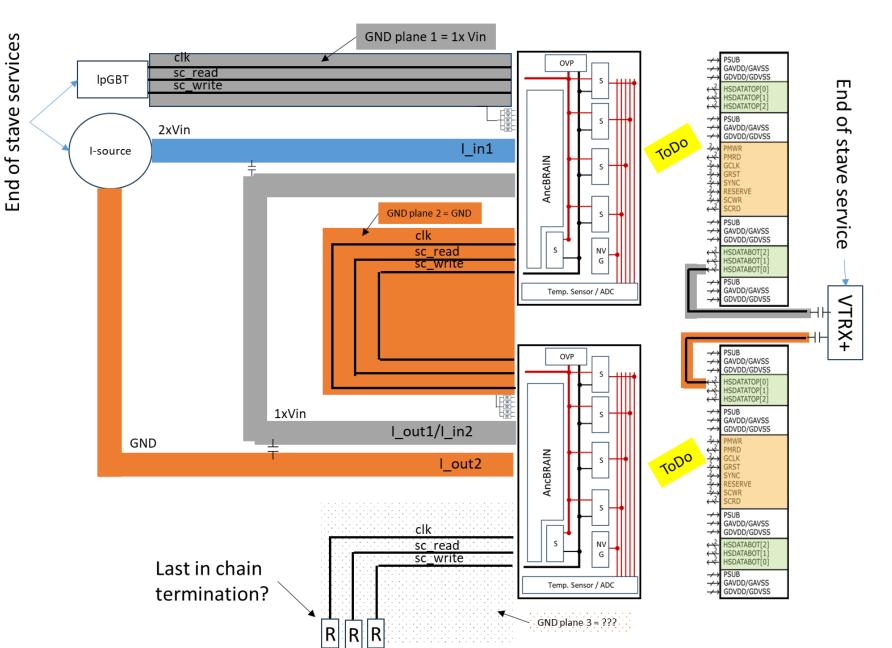

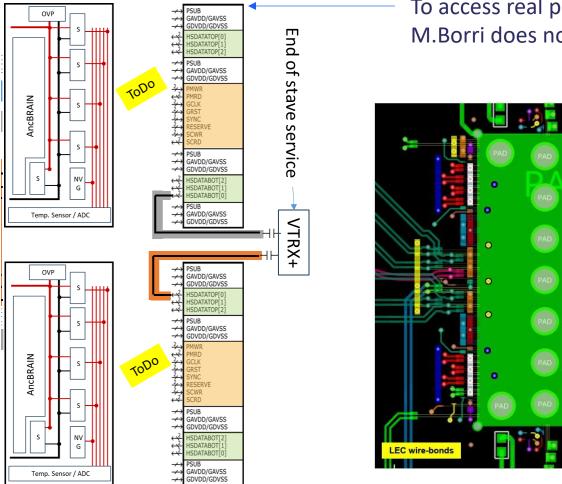

#### Sanity check on the "end of stave side" of B-FPC

services

I in = const

clk, sc\_read, sc\_write: AC or DC coupled?

#### Sanity check on the "LAS side" of B-FPC

| Supply purpose  | Nets        | Voltage [V] | Current [mA] | Pads on LEC | Pads on REC |

|-----------------|-------------|-------------|--------------|-------------|-------------|

| Services        | SDVDD-SDVSS | 1.2 to 1.32 | 227          | Yes         | Yes         |

| Global analogue | GAVDD-GAVSS | 1.2 to 1.32 | 540          | Yes         | Yes         |

| Global digital  | GDVDD-GDVSS | 1.2 to 1.32 | 1369         | Yes         | Yes         |

| Serialisers     | TXVDD-TXVSS | 1.8         | 200          | Yes         | No          |

| Substrate bias  | PSUB        | -1.2  to  0 |              |             |             |

To access real pin out?

M.Borri does not have access to the CERN MOSAIX web page.

## Thank you

**Facebook:** Science and Technology Facilities Council

X:@STFC\_matters

**YouTube:** Science and Technology Facilities Council