# Software: Testing, Commissioning, and Operation

Oxford SVT working meeting

16 Dec. 2025

Gregor Eberwein (MIT) on behalf of SVT WP2

# Outline

- MOSAIX recap

- Testing infrastructure, qualification and status

- SVT SW framework

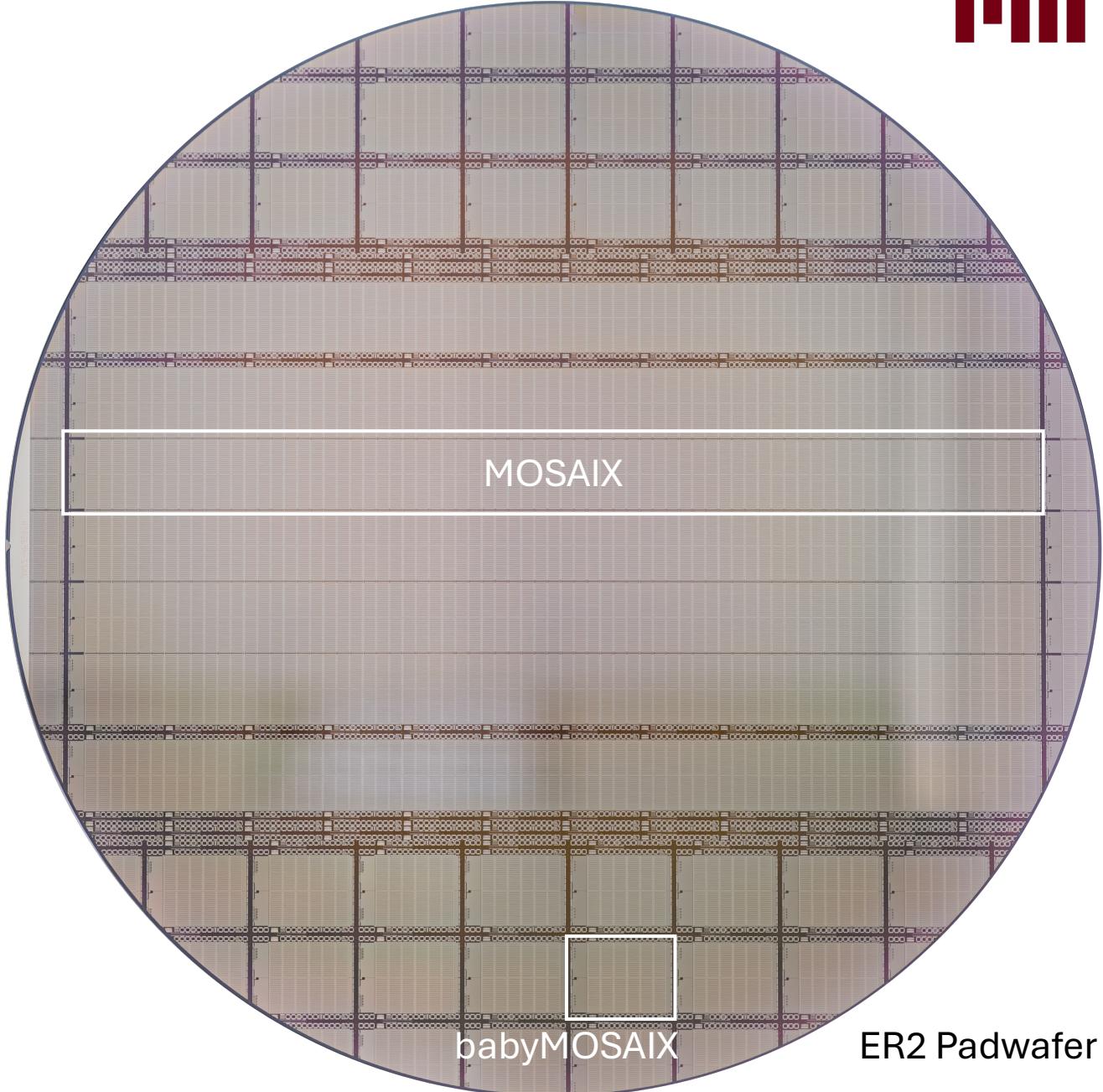

# MOSAIX chip status

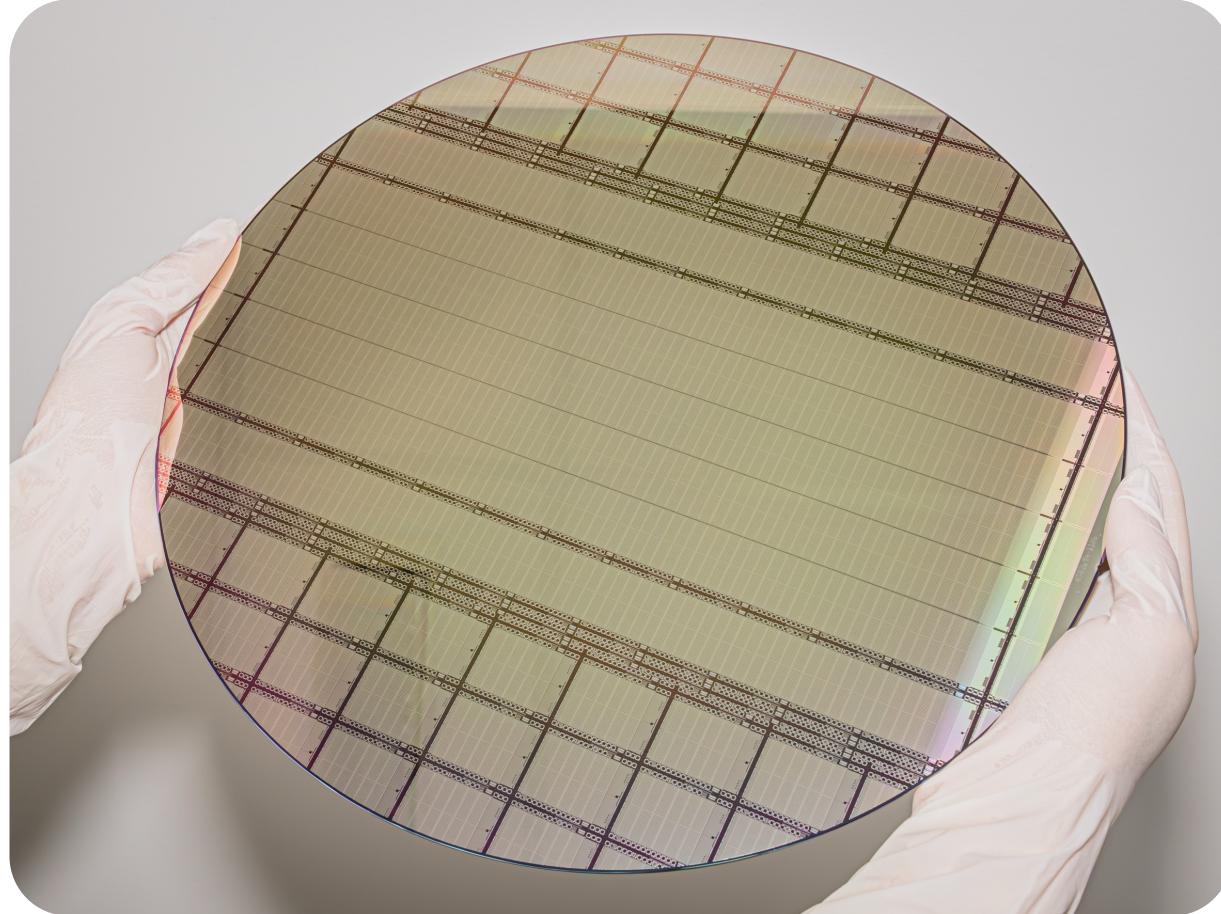

- MOSAIX wafers (ER2) arriving in February

Pad wafers: **arrived December**

- ER3 submission preparation in progress -> feedback to designers by mid 2026

# MOSAIX chip status

- MOSAIX wafers (ER2) arriving in February

Pad wafers: **arrived December**

- ER3 submission preparation in progress -> feedback to designers by mid 2026

# MOSAIX chip status

- MOSAIX wafers (ER2) arriving in February

Pad wafers: **arrived December**

- ER3 submission preparation in progress -> feedback to designers by mid 2026

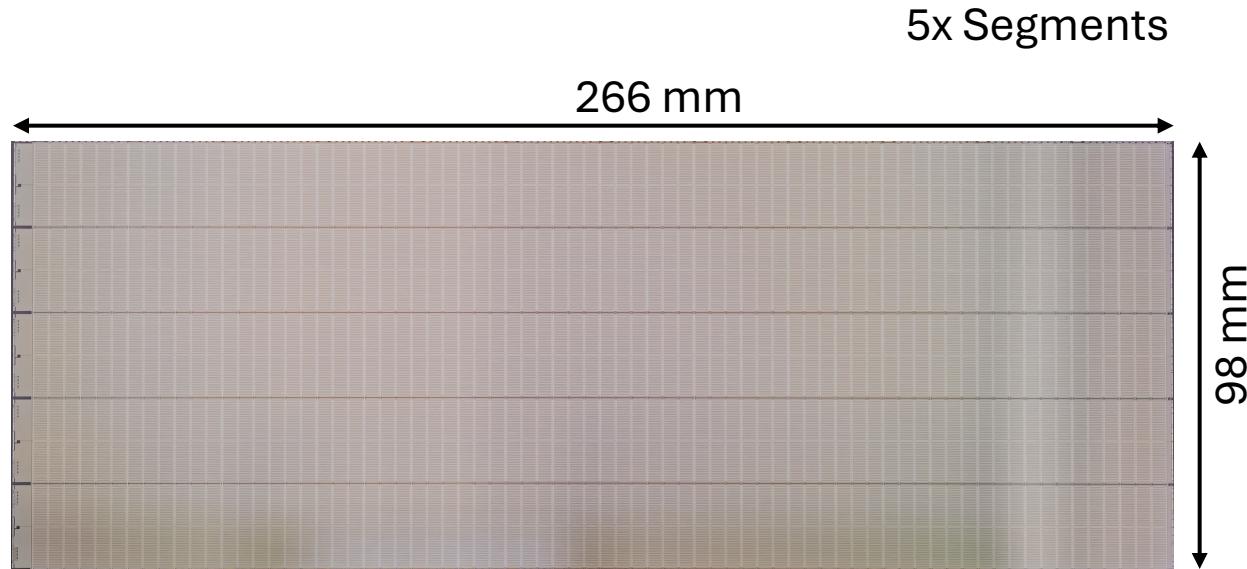

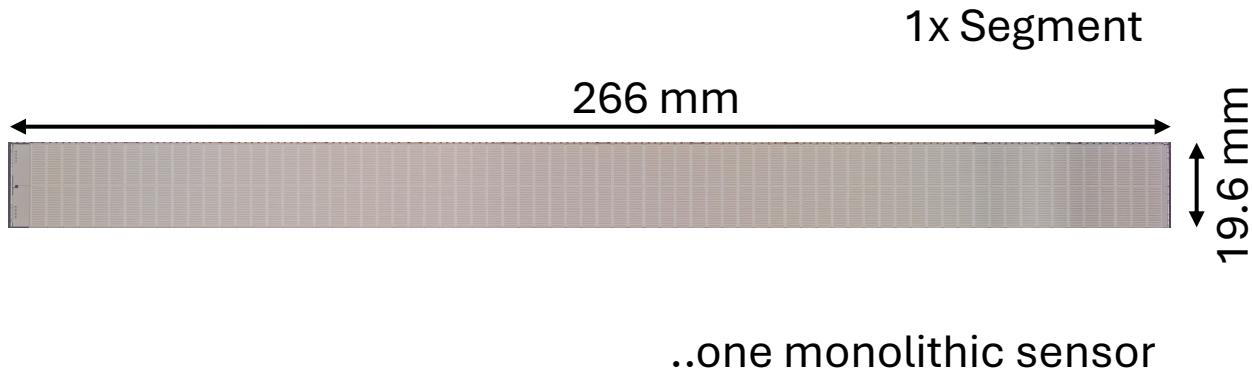

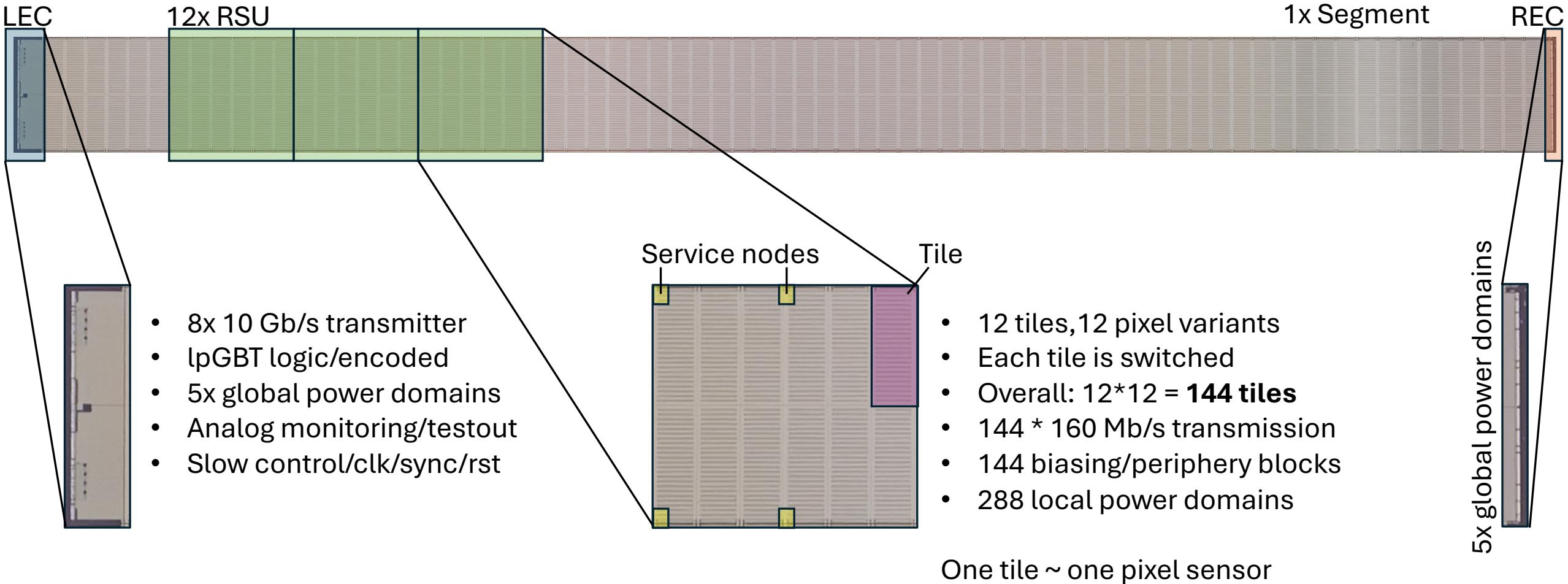

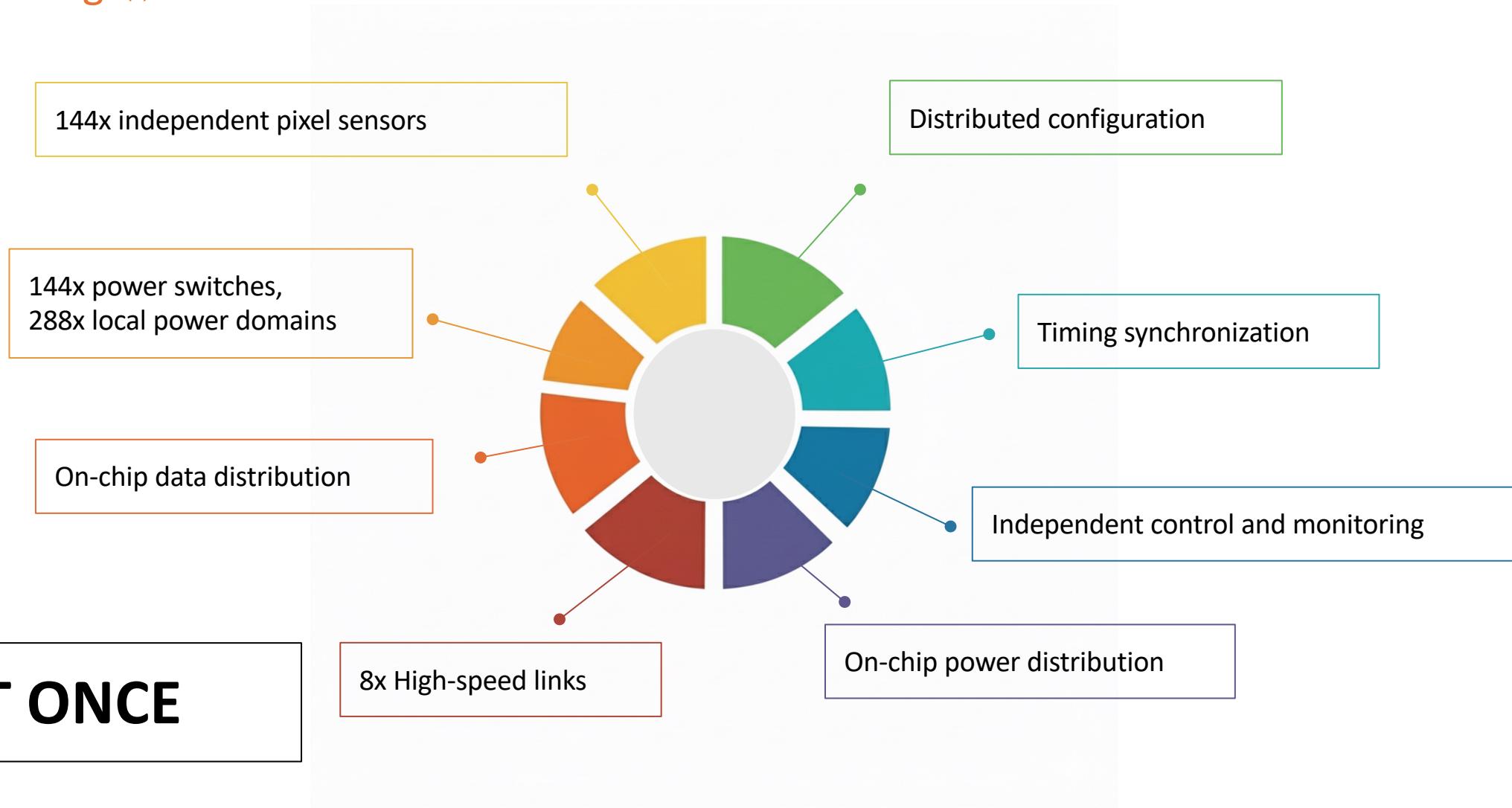

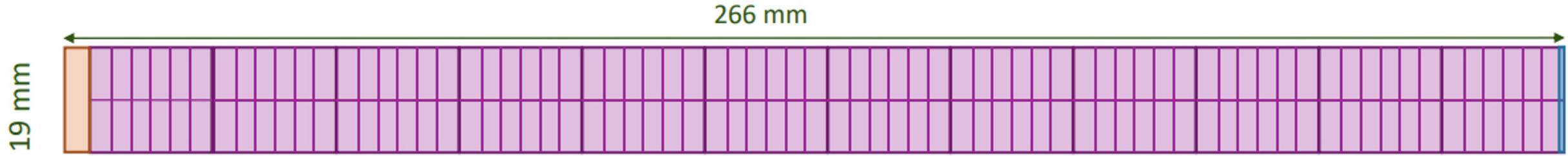

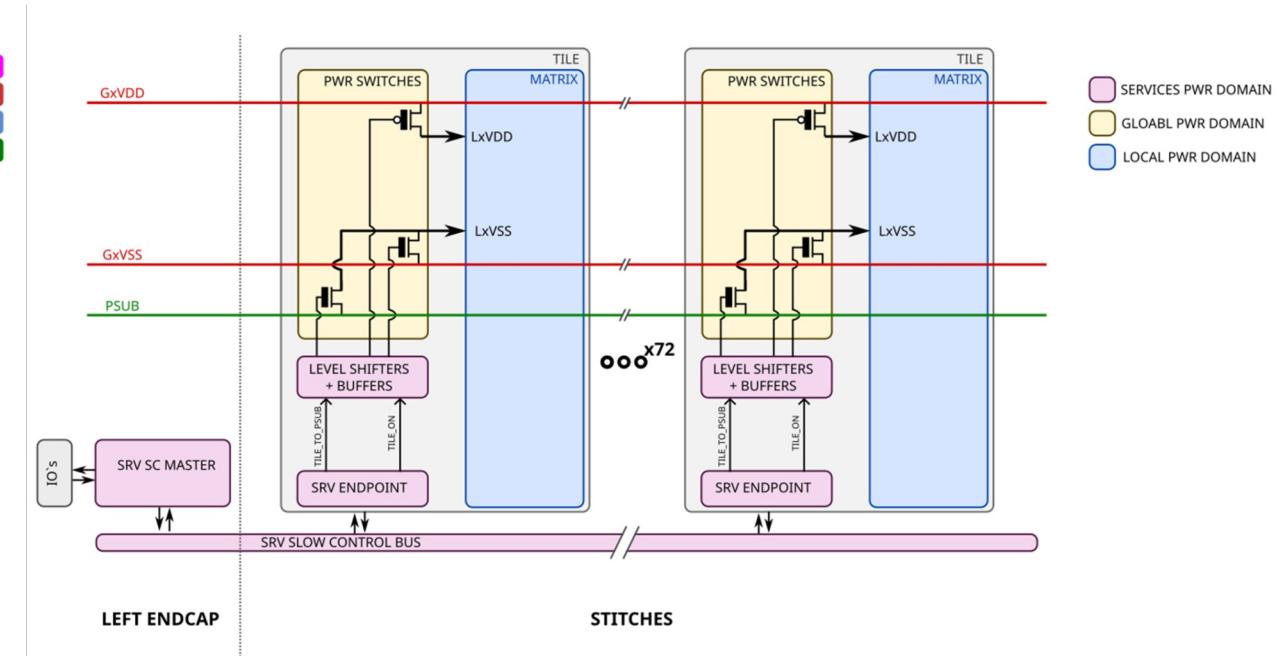

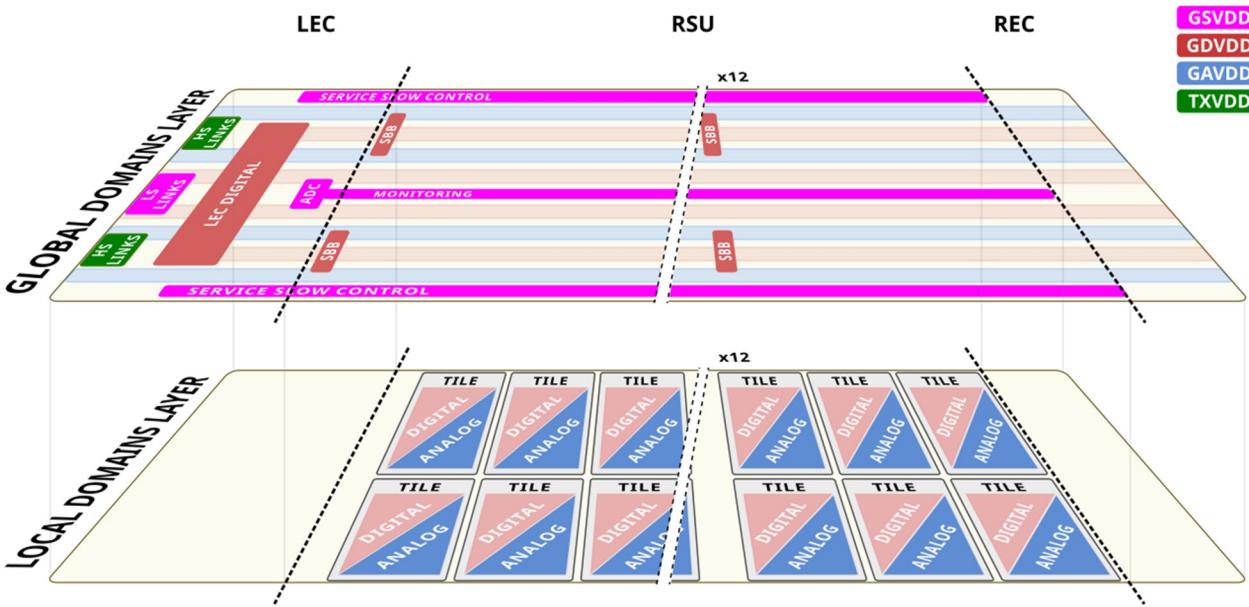

# MOSAIX anatomy

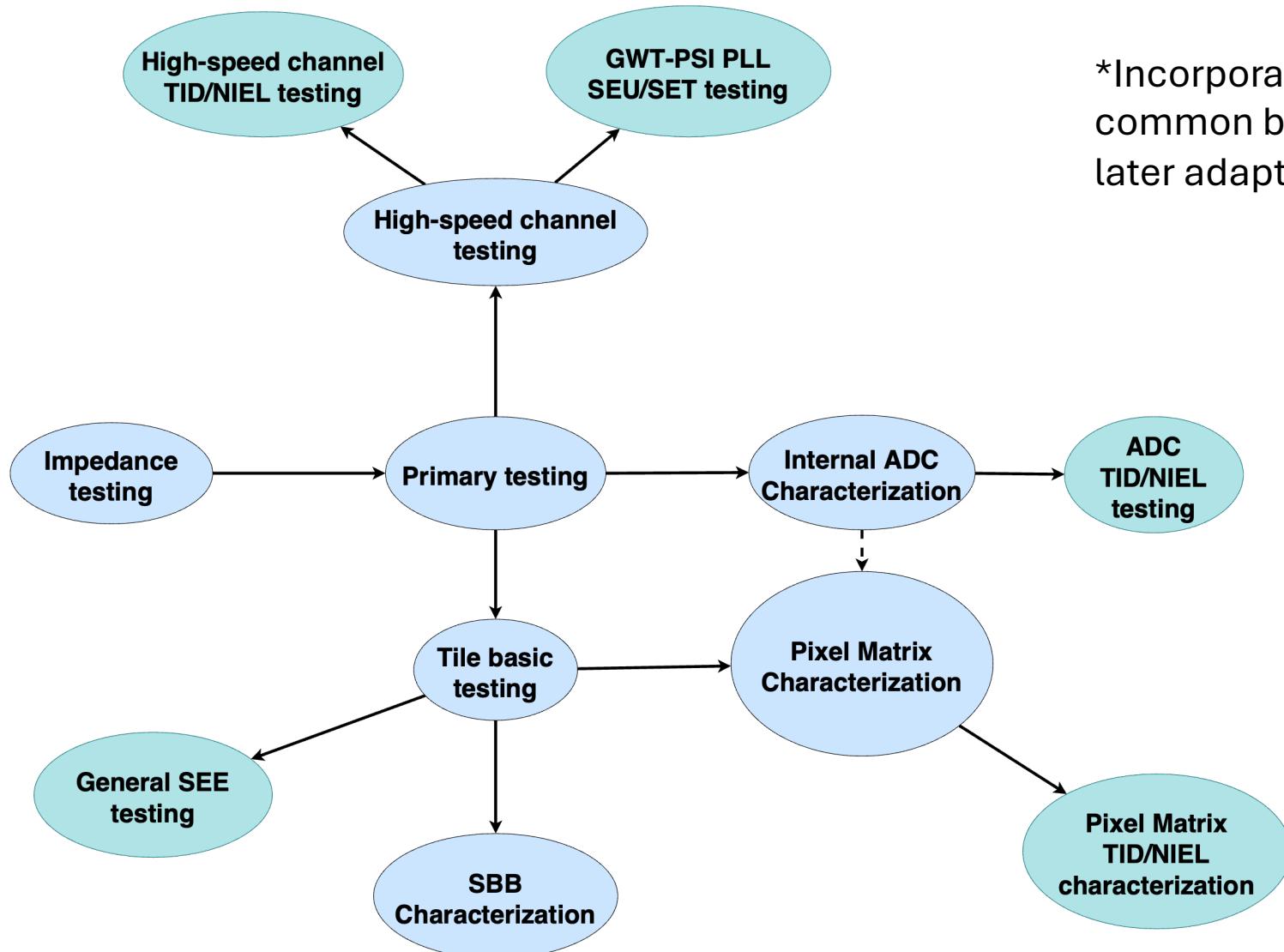

# MOSAIX qualification goals

- Verify functionality of all features

- Yield of blocks

- Identify the pixel variant

- 10 Gb/s transmission on-wafer

- Radiation effects

- *ambition for day one readiness*

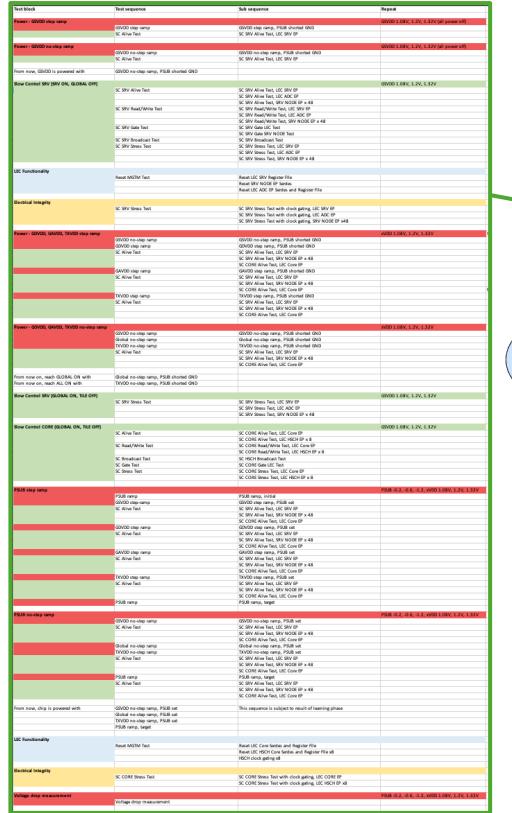

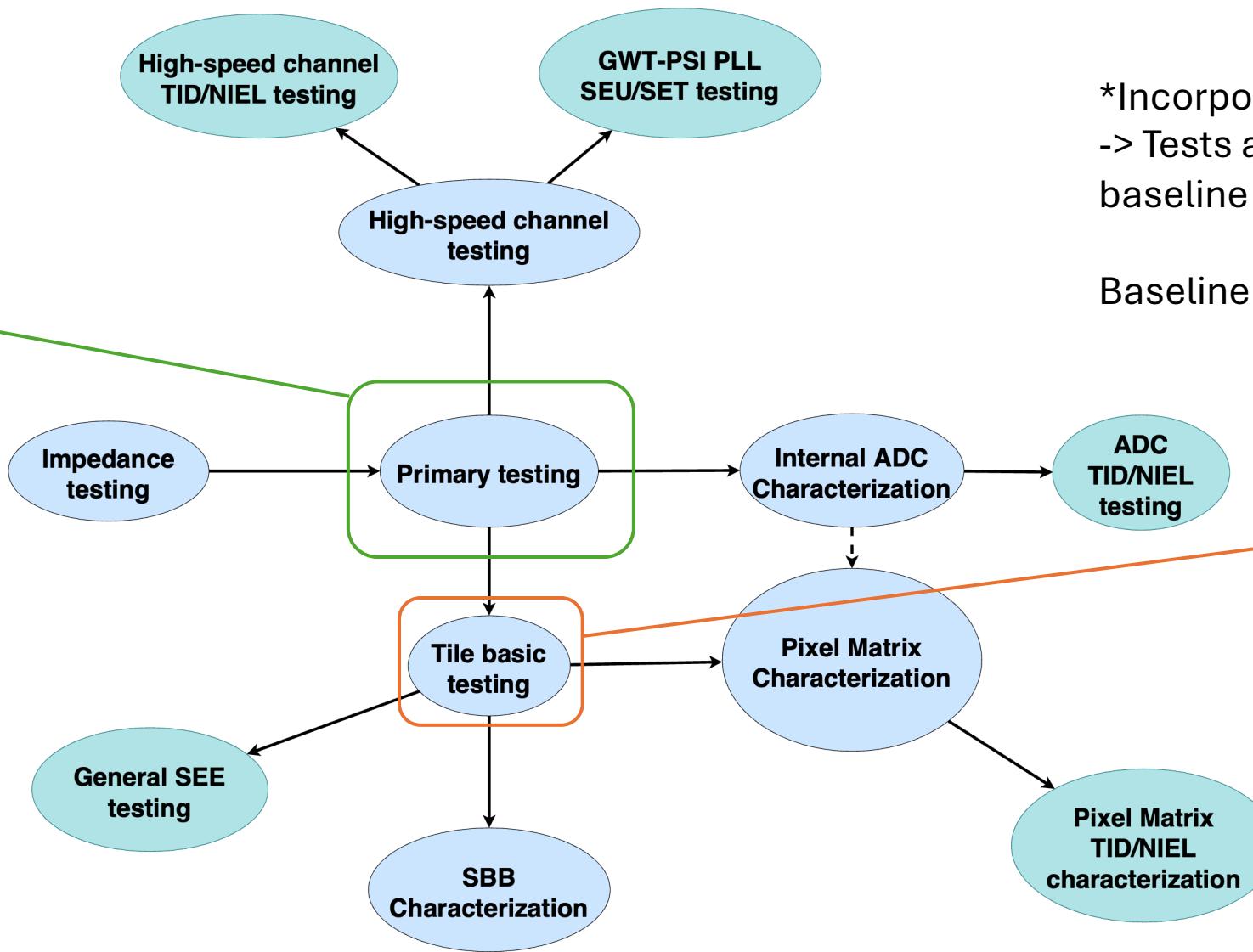

| Test stage                             | Dependencies                     | Description                                                                                                                                            |

|----------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Primary testing                        | Impedance testing                | Testing of services and global supplies, slow control access and critical features, e.g., service node control. Pre-requisite for all further testing. |

| Impedance testing                      | Primary testing                  | TBD                                                                                                                                                    |

| Tile basic testing                     | Primary testing                  | Testing tile-level functionality. SBB data transfer.                                                                                                   |

| Analog circuitry and ADC testing       | Primary testing                  | Characterization of on-chip ADC and analog monitoring network. Includes also testing of bandgap reference.                                             |

| Pixel matrix characterization          | Tile basic testing /ADC testing? | Characterization of pixel matrix.                                                                                                                      |

| High-speed channel                     | Primary testing                  | Testing high-speed channel                                                                                                                             |

| SBB characterization                   | Tile basic testing               | Full characterization of the SBB. Check margins for data transfer.                                                                                     |

| General SEE testing                    | Tile basic testing               | SEU cross-section, SEL susceptibility                                                                                                                  |

| Pixel matrix TID/NIEL characterization | Pixel matrix characterization    | Pixel matrix performance after radiation                                                                                                               |

| High-speed channel TID/NIEL testing    | High-speed channel               | LEC/serializer performance after radiation                                                                                                             |

| ADC TID/NIEL testing                   | ADC testing                      | ADC performance after radiation                                                                                                                        |

| GWT-PSI PLL SEU/SET testing            | High-speed channel               | Check PLL susceptibility for SEU/SET                                                                                                                   |

\*ITS3 stage plan

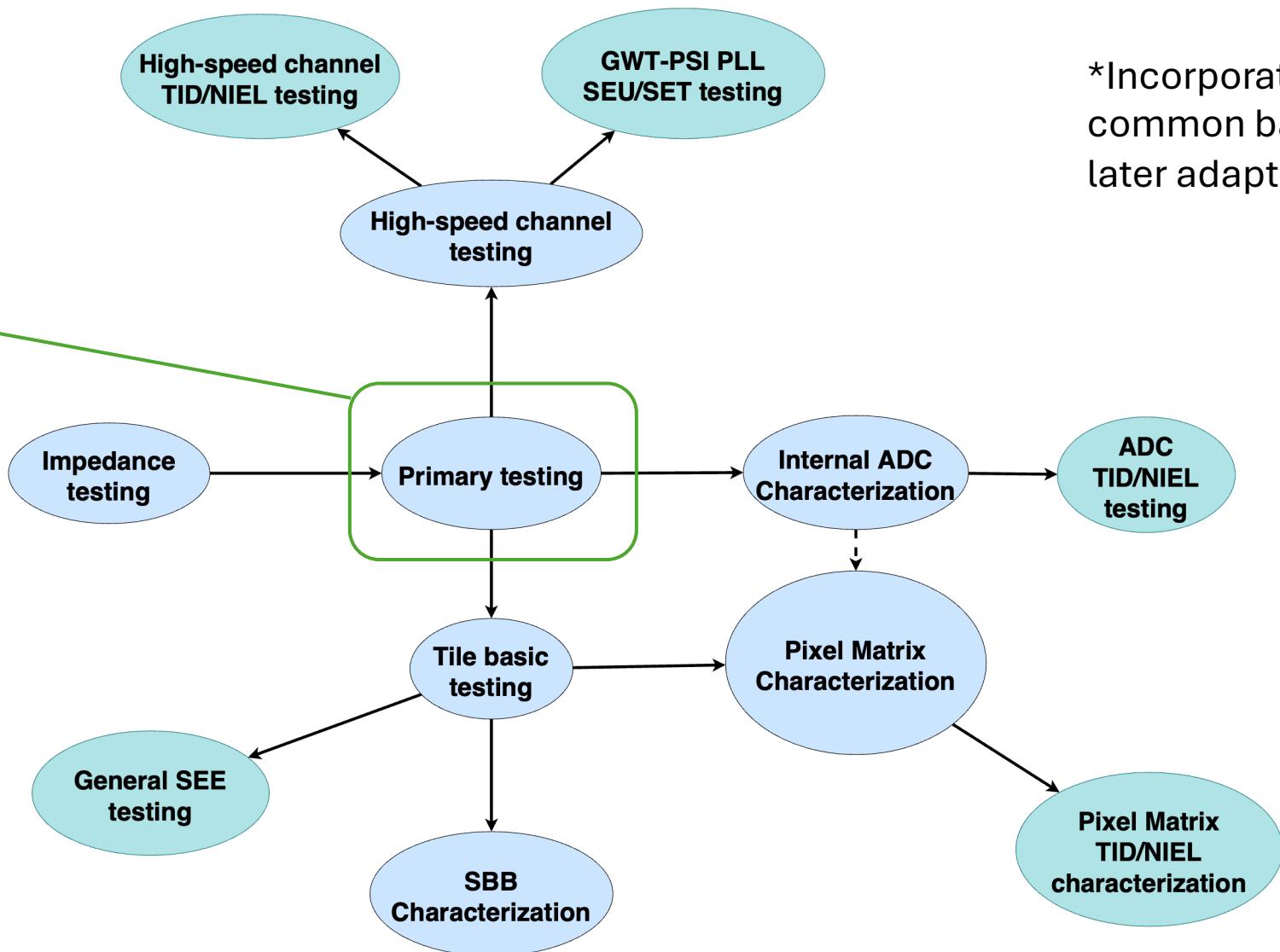

# Qualification and characterisation stages

\*Incorporation of ITS3 plan as common baseline in ER2, later adapted for SVT

# Qualification and characterisation stages

## Tests *before* powering on the individual tiles

\*Incorporation of ITS3 plan as common baseline in ER2, later adapted for SVT

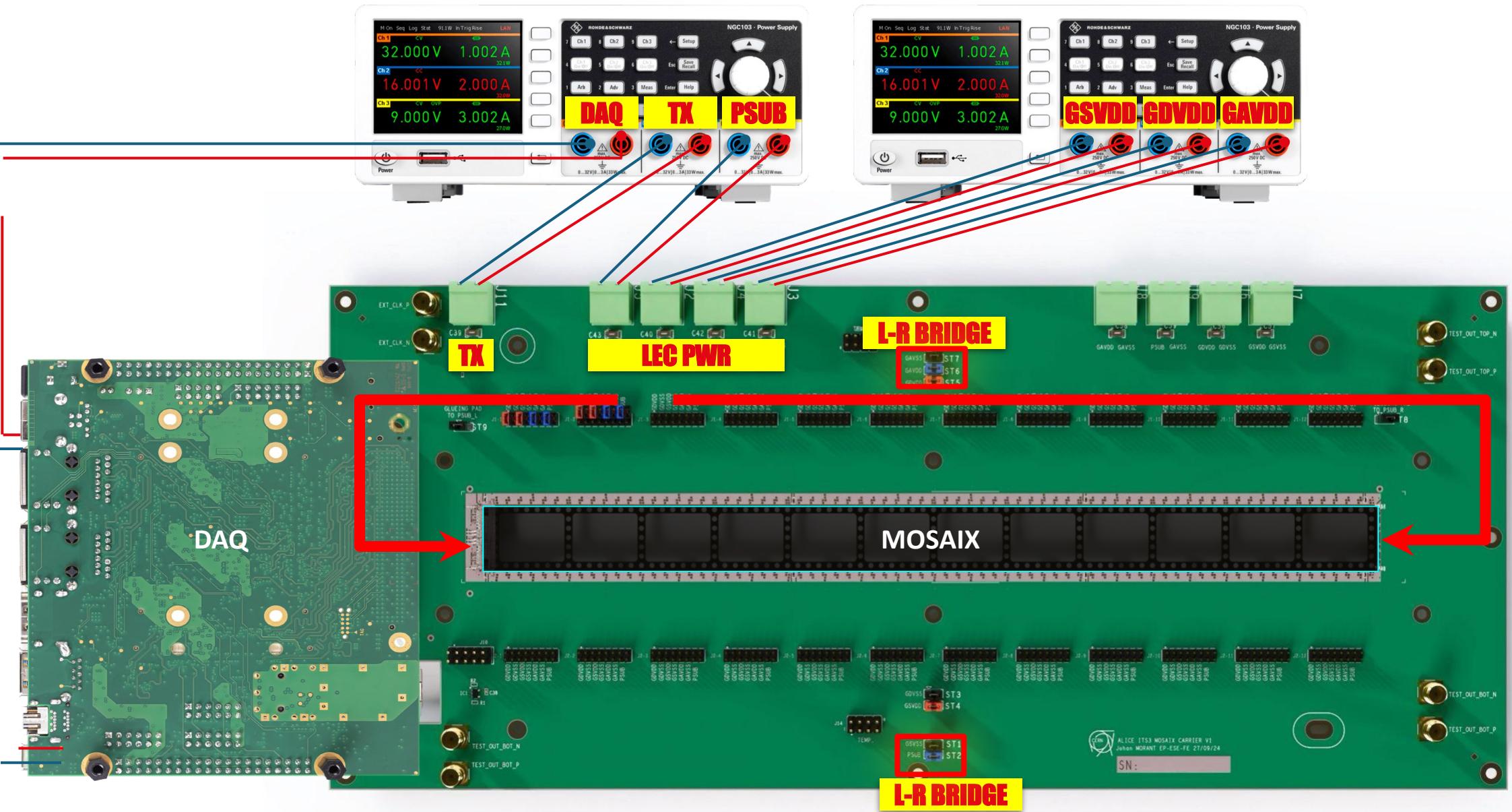

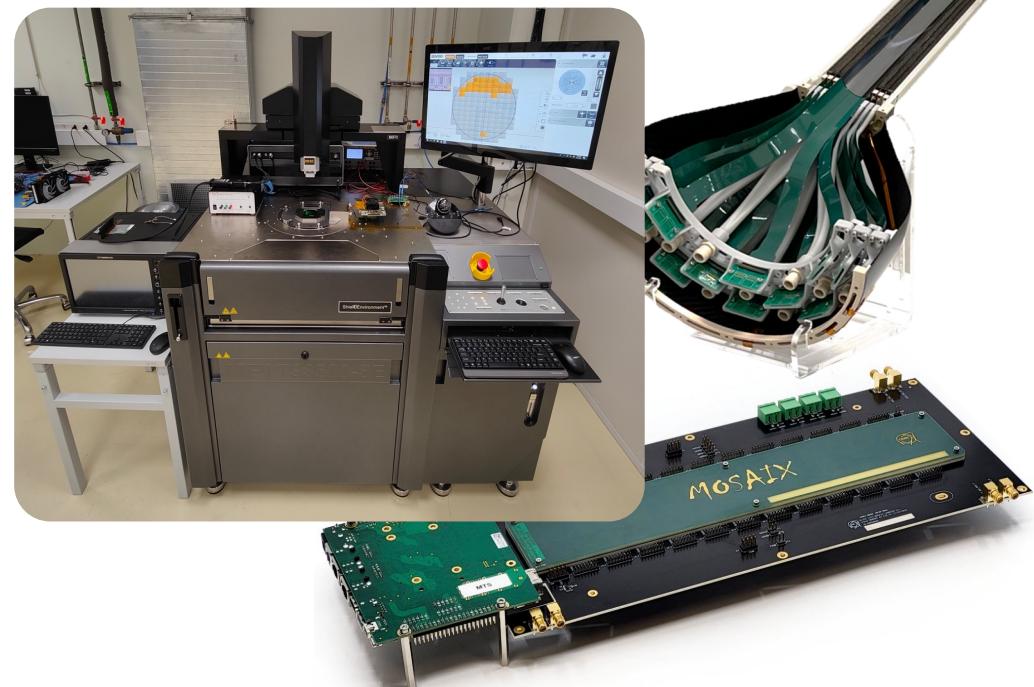

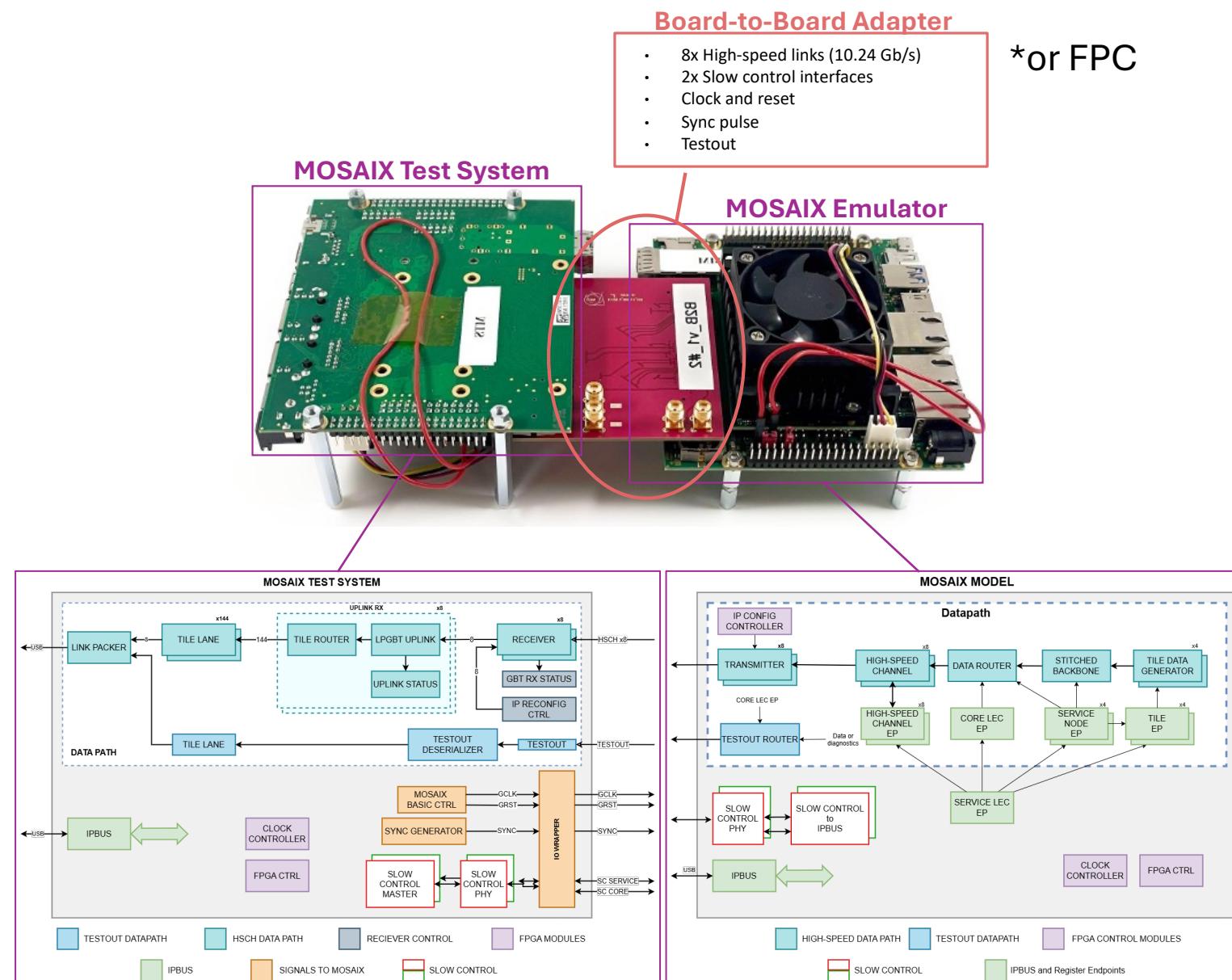

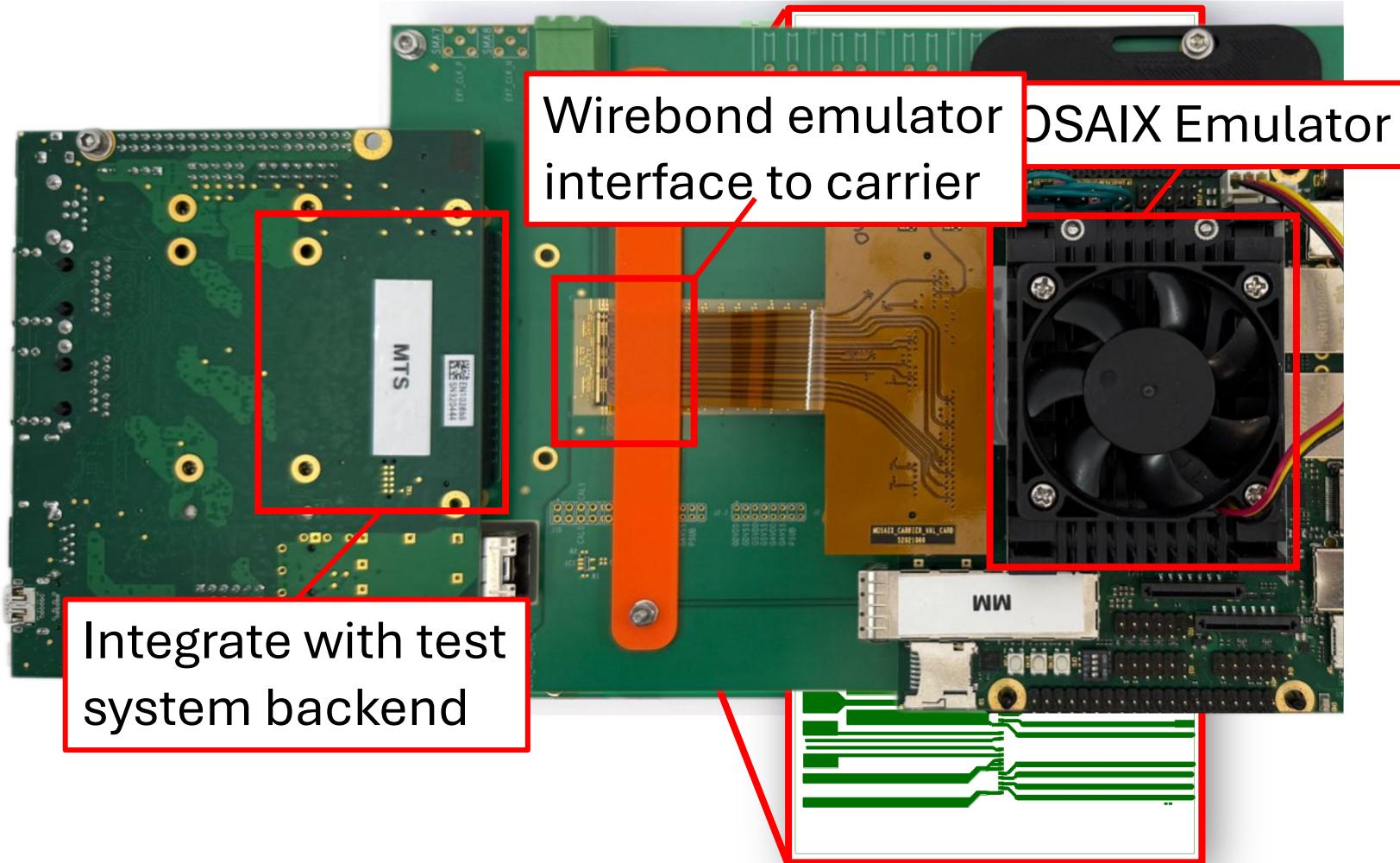

# Testing Infrastructure

2x power supply

SMU & multiplexer

for impedance

Altera Arria 10 & Enclustra baseboard

1 set/MOSAIX (Segment)

Connected via USB3 <> PC

MOSAIX targets:

- **Wafer Probing** see *Stefano's presentation*

- Carrier PCB

- Bent models/test beams

# Tests and readiness

- Firmware -> done (ITS3)

- Includes emulator allows to test framework

- Hardware agnostic API -> ongoing (ownership of small part)

- List of tests & status thereof

- Readiness report this week

- It will be possible to run set of tests when chips are available

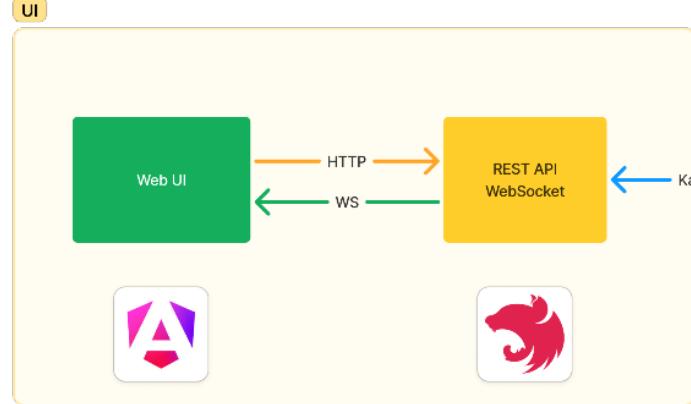

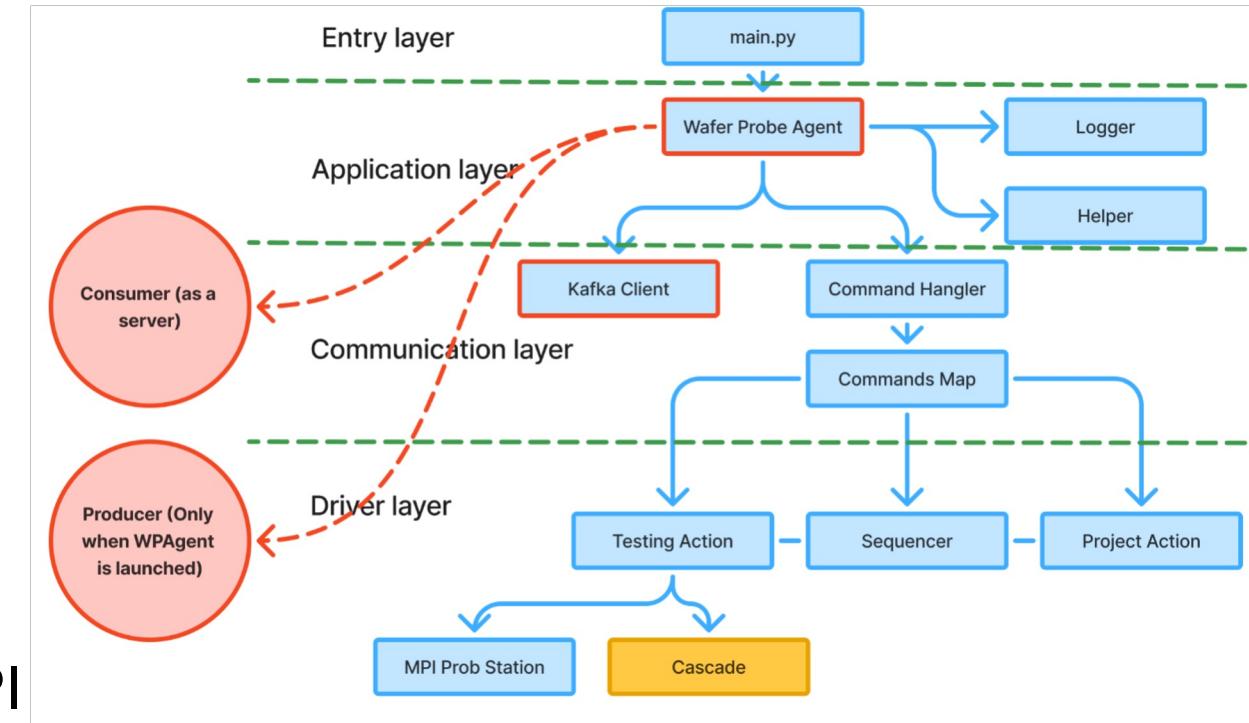

# SVT SW framework

Web based UI

Produces commands

& visualizes data

## Distributed Kafka backbone

## UI

- Web based service, consist of 2 parts:

- Front-end

- running in the browser

- Back-end

- ensure communication between other services, provides HTTP, WS, Kafka interfaces for communication

- Assignment

- UI for start/stop operations

- UI for data overview/analysis

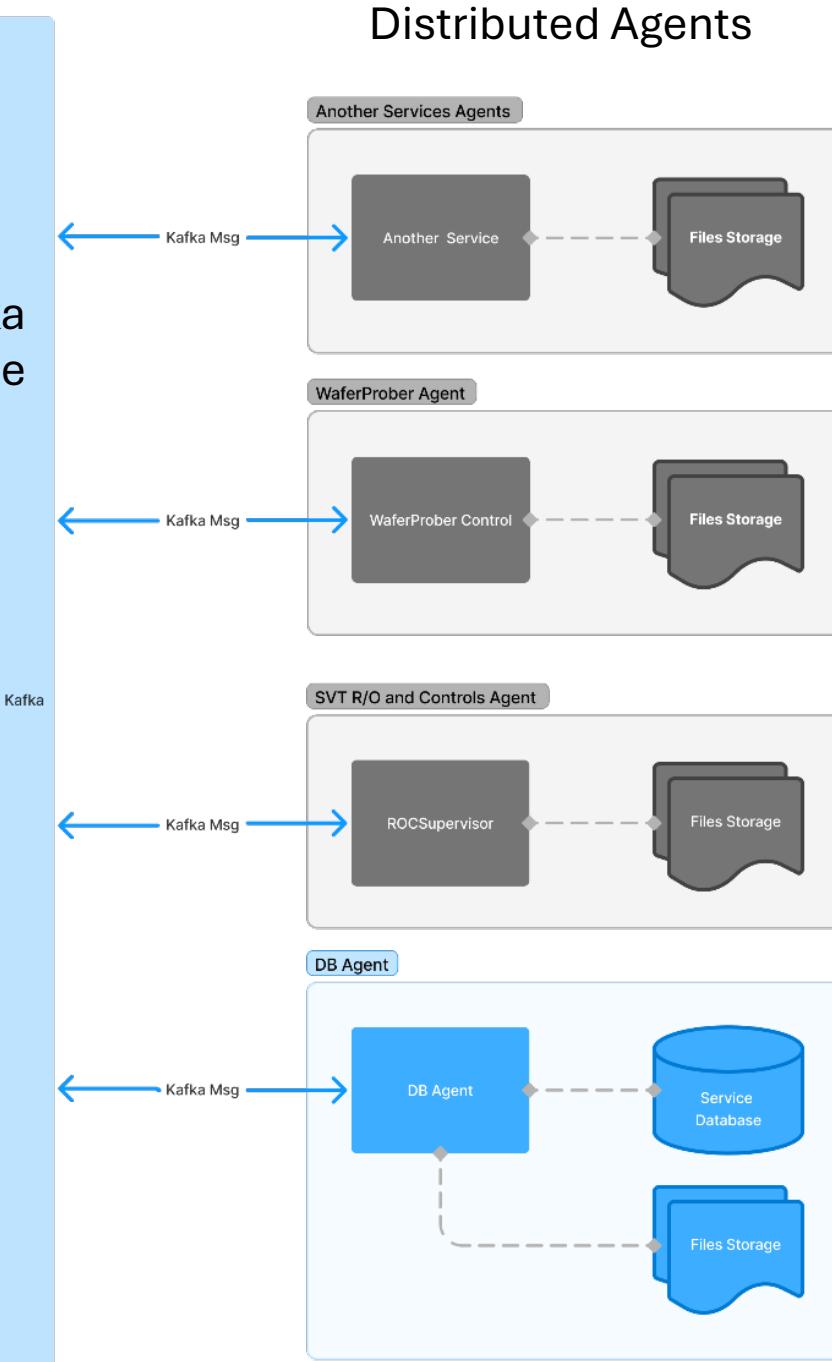

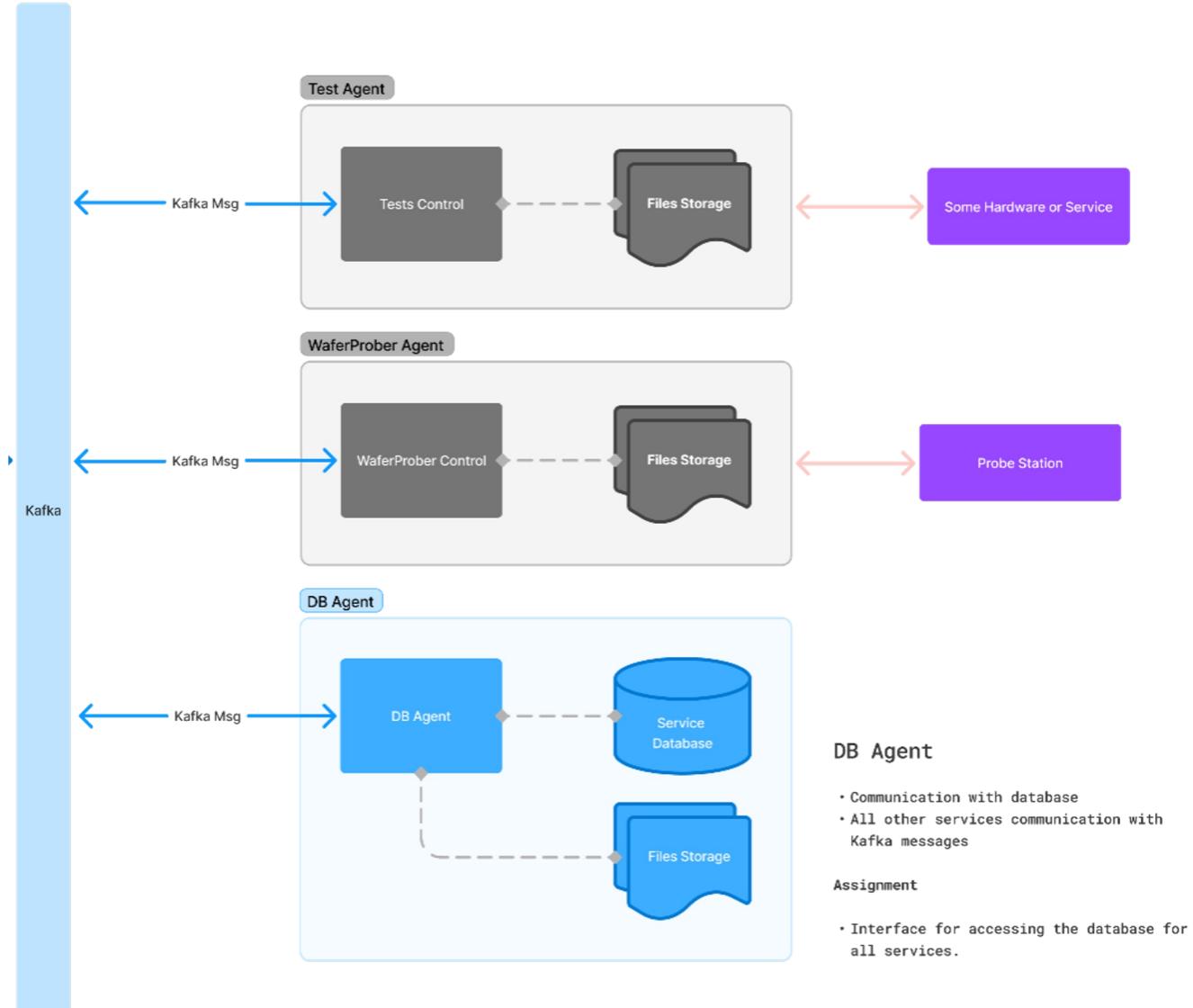

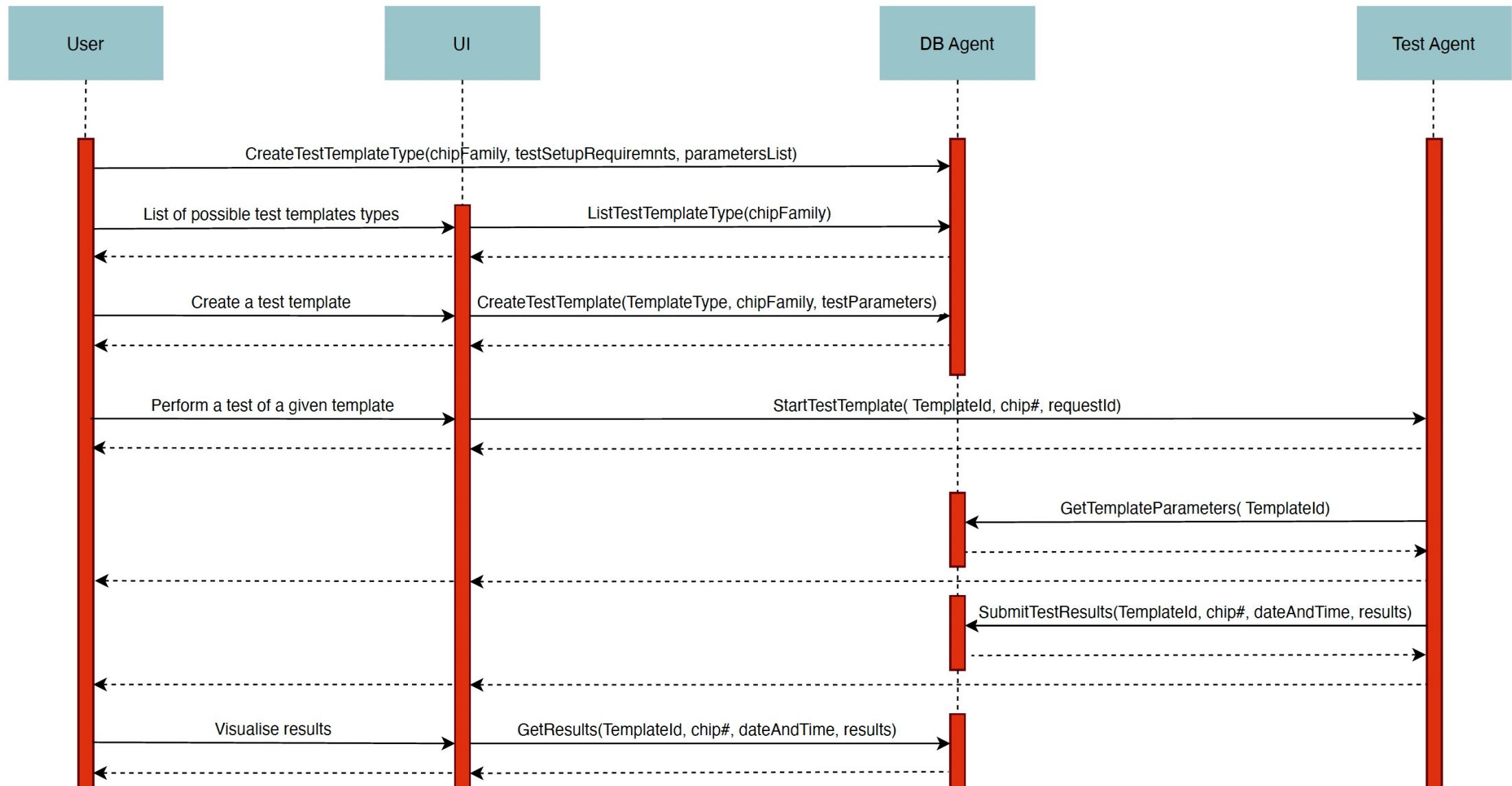

# Agents under development

- **Test Agent**

- Runs the chip tests

- **Wafer Probe Agent**

- Controller to operate the wafer prober

- **Database Agent**

- Communication with DB (CERN DB on demand service)

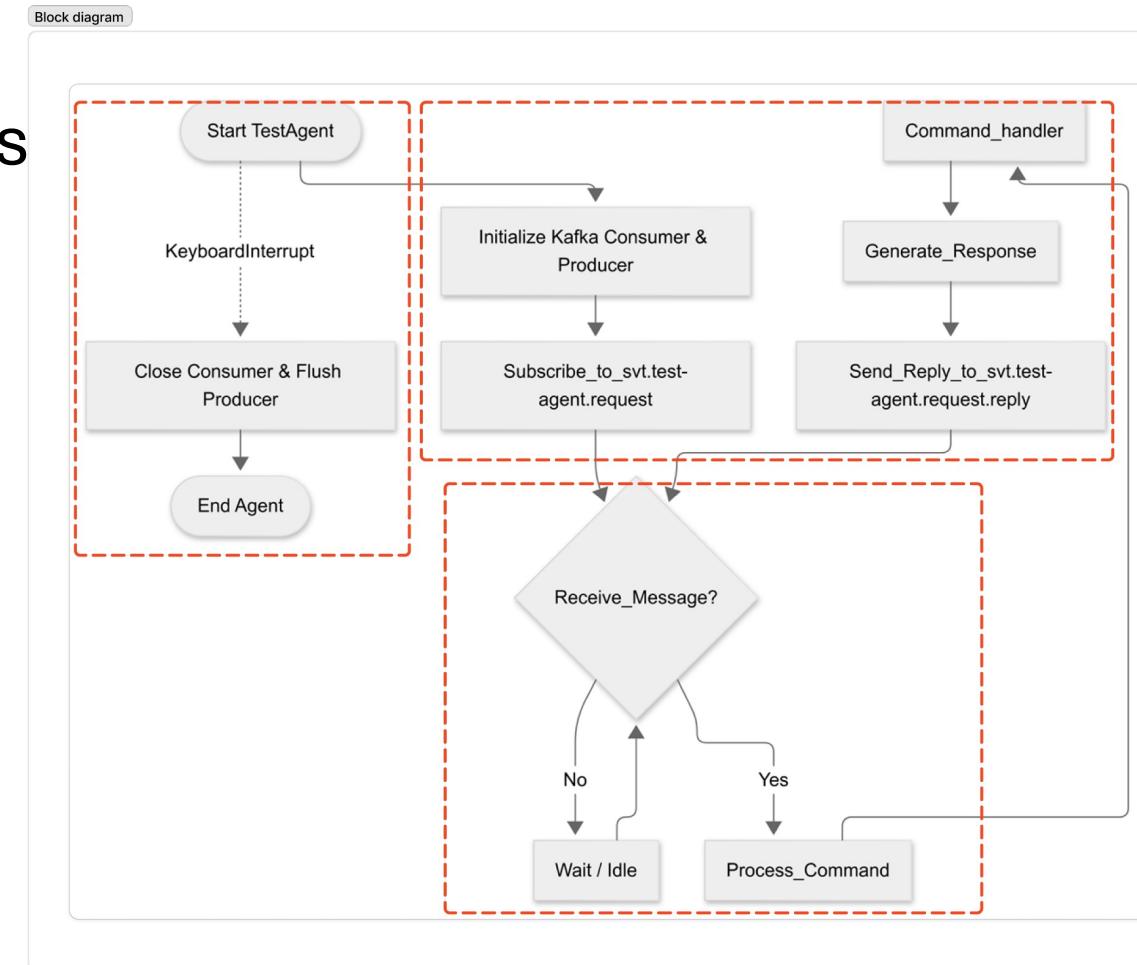

# Test Agent

- Individual agents for separate SVT ASICs

- For MOSAIX:

- Full integration of ITS3 ER2 qualification and characterisation tests in SVT SW framework

- Derive qualification strategy for ER3

- Use emulator setup (running) to create dummy tests

- Status: ongoing

- New: test sequencer, direct DB Agent access, direct feedback to UI

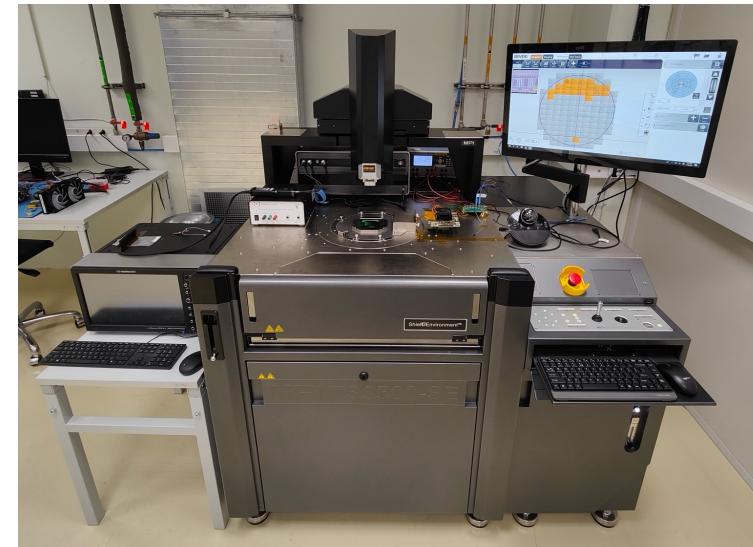

# Wafer Probe Agent

- Central controller to operate wafer probe stations autonomously

- Interface with the remaining testing framework

- I.e. move to chip, perform test (sequence)

- Status: ongoing

- New: set of interface commands for MPI wafer prober, retrieving DB info, command sequences(json), wafer maps -> see *Stefano's presentation*

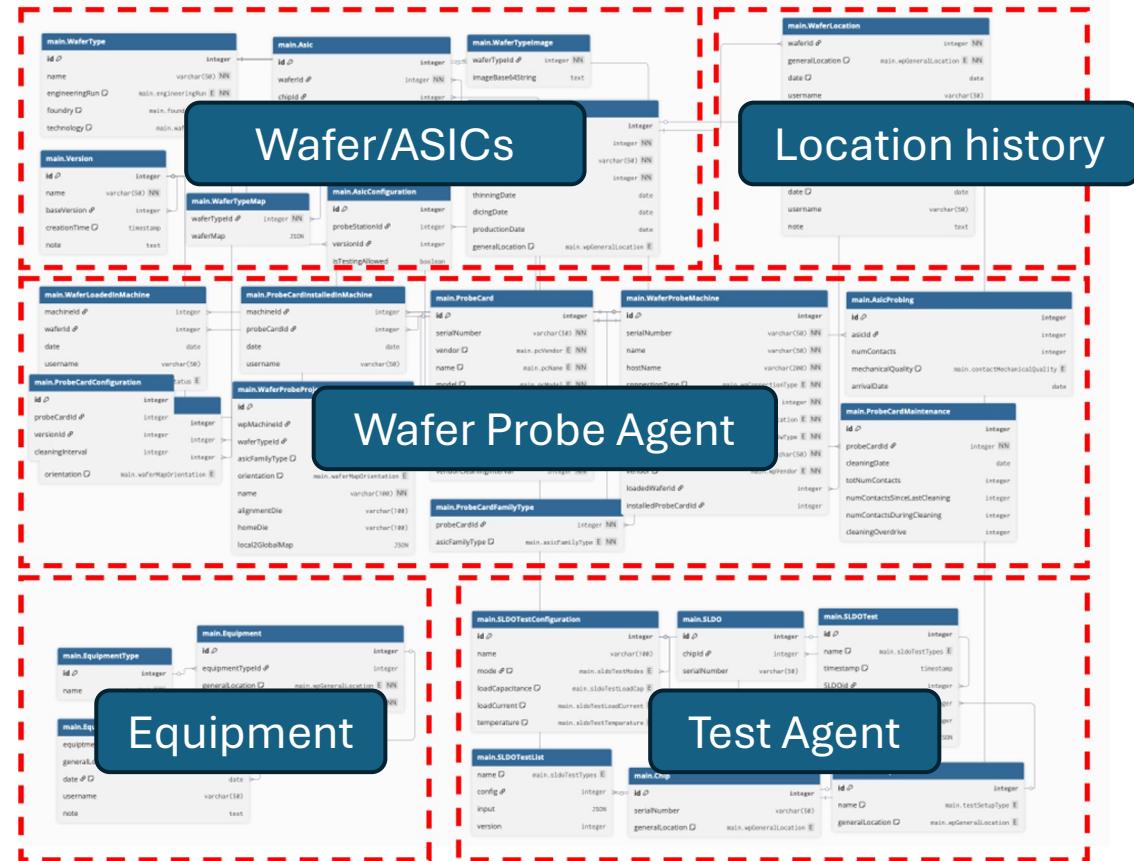

# DB Agent

- DB Agent is the main communication layer with the Database

- Kafka consumer/producer for pull and push request/reply messages

- DB structure: work in progress

- New: history tracking

- Database on temporary dev instance

# User interface (UI)

- Global interface between operator, DB, and all Agents

- Status: ongoing

- New: chip tracking, creation of new ASICs individually or in bulk

The screenshot displays the ePIC user interface for managing ASICs. On the left, a sidebar menu includes options for WFM, ASICS, Wafers, Admin, and DEV. The main content shows details for an ASIC labeled 'asic-1' with ID 1, Serial No. asic-1, and Family Type Ancillary. A 'Voltage Scan' card is open, showing a table with a single row: 'Status' (Nan), 'IV' (100), and 'Done'. Below this are buttons for 'Location History' and 'Update Location'. A red box highlights these buttons. A red arrow points from this box to a larger 'Chip Location History' modal window on the right. This window lists location changes for the chip, with rows for 'CERN\_106\_R\_E10' (Changed At 2025-10-31, Note 'Some reason'), 'Prague' (Changed At 2025-10-21, Note 'Some reason ...'), and several entries from 2025-10-25 at 13:19:34. A red arrow points from the 'Update Location' button to a 'Update Chip Location' modal window at the bottom right. This modal window contains fields for 'New Location\*' (Prague), 'Location Change Date' (2025-10-21), 'Note\*' (Some reason ...), and buttons for 'Cancel' and 'Update'.

# Conclusions

- MOSAIX wafers arrive early 2026

- Foundational infrastructure ready and tested, using emulator for pre-testing

- MOSAIX test sequence development in progress

- SVT SW framework is steadily growing, Agents need still work. Next: use emulator to run realistic test cases

- Input and contributions very welcome

- Agnostic and flexible in regard to adding Agents and functionality for testing sites and production

- Goal of plug-and-play with tested hardware

# BACKUP

# Example communication

# Qualification and characterisation stages

## Tests *before* powering on the individual tiles

\*Incorporation of ITS3

-> Tests assumed in WP2,

baseline later adapted for SVT

Baseline common plan for ER2, then

| Test block                                                                | Test sequence                                              | Sub sequence                         | Report                                                        |

|---------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------|

| <b>Power on a single tile(s) at a time - LVOD(n)</b>                      |                                                            |                                      | <b>GYVO0: 1.0V, 1.2V, 1.3V</b>                                |

|                                                                           | LVOD<0> close switch                                       | SC CORE Alive Test, Tile EP          |                                                               |

|                                                                           | SC Alive Test                                              | SC CORE Alive Test, Tile EP          |                                                               |

|                                                                           | LVOD<0> open switch                                        | SC CORE Alive Test, Tile EP          |                                                               |

| Loop over all tiles, extract information on how many tiles are alive.     |                                                            |                                      |                                                               |

| <b>Show Control CORE - tile(s) for alive tiles, single tile at a time</b> |                                                            |                                      | <b>GYVO0: 1.0V, 1.2V, 1.3V</b>                                |

|                                                                           | LVOD<0> close switch                                       | SC CORE Read/Write Test              |                                                               |

|                                                                           | SC CORE Read/Write Test                                    | SC CORE Read/Write Test, LEC Core EP |                                                               |

|                                                                           | SC CORE Read/Write Test                                    | SC CORE Read/Write Test, LEC HCH EP  |                                                               |

|                                                                           | SC CORE Read/Write Test                                    | SC CORE Stress Test, LEC Core EP     |                                                               |

|                                                                           | SC CORE Read/Write Test                                    | SC CORE Stress Test, LEC HCH EP      |                                                               |

|                                                                           | SC CORE Stress Test                                        | SC CORE Stress Test, LEC Core EP     |                                                               |

|                                                                           | SC CORE Stress Test                                        | SC CORE Stress Test, LEC HCH EP      |                                                               |

|                                                                           | LVOD<0> open switch                                        | SC CORE Stress Test, Tile EP         |                                                               |

| <b>Power on all tiles - LVOD(n)</b>                                       |                                                            |                                      | <b>GYVO0: 1.0V, 1.2V, 1.3V (WARNING, difference in order)</b> |

|                                                                           | Power on all tiles, left to right                          | SC CORE Alive Test, Tile EP <ALIVE>  |                                                               |

|                                                                           | SC Alive Test                                              | SC CORE Alive Test, Tile EP <ALIVE>  |                                                               |

| <b>Show Control CORE - tile(s) for alive tiles</b>                        |                                                            |                                      | <b>GYVO0: 1.0V, 1.2V, 1.3V (WARNING, difference in order)</b> |

|                                                                           | Power on all tiles, left to right                          | SC CORE Read/Write Test              |                                                               |

|                                                                           | SC CORE Read/Write Test                                    | SC CORE Read/Write Test, LEC Core EP |                                                               |

|                                                                           | SC CORE Read/Write Test                                    | SC CORE Read/Write Test, LEC HCH EP  |                                                               |

|                                                                           | SC Broadcast Test                                          | SC Tile Broadcast Test               |                                                               |

|                                                                           | SC CORE Stress Test                                        | SC CORE Stress Test, LEC Core EP     |                                                               |

|                                                                           | SC CORE Stress Test                                        | SC CORE Stress Test, LEC HCH EP      |                                                               |

|                                                                           | Power off all tiles, right to left                         | SC CORE Stress Test, Tile EP         |                                                               |

| <b>BBB Testing</b>                                                        |                                                            |                                      | <b>GYVO0: 1.0V, 1.2V, 1.3V</b>                                |

|                                                                           | Test single 580 Buffer                                     |                                      |                                                               |

|                                                                           | Test step range go to 580 DATA TRANSFER READY              |                                      |                                                               |

|                                                                           | Test step range go to 580 DATA TRANSFER READY              |                                      |                                                               |

|                                                                           | Memory check jitter on EEC                                 |                                      |                                                               |

| <b>Power on all tiles with SMB DATA TRANSFER READY - LVOD(n)</b>          |                                                            |                                      | <b>GYVO0: 1.0V, 1.2V, 1.3V (WARNING, difference in order)</b> |

|                                                                           | Power on all tiles, left to right                          | SC CORE Alive Test, Tile EP <ALIVE>  |                                                               |

|                                                                           | SC Alive Test                                              | SC CORE Alive Test, Tile EP <ALIVE>  |                                                               |

|                                                                           | Power off all tiles, right to left                         | SC CORE Alive Test, Tile EP <ALIVE>  |                                                               |

| <b>BBB Data Transmission Test per tile(s)</b>                             |                                                            |                                      | <b>GYVO0: 1.0V, 1.2V, 1.3V</b>                                |

|                                                                           | Test one step range go to SMB DATA TRANSFER READY          |                                      |                                                               |

|                                                                           | LVOD<0> close switch                                       |                                      |                                                               |

|                                                                           | Test(s) PRBS Test                                          |                                      |                                                               |

|                                                                           | Poweroff: SMB parameter reset                              |                                      |                                                               |

|                                                                           | Poweroff: SMB parameter reset                              |                                      |                                                               |

|                                                                           | LVOD<0> open switch                                        |                                      |                                                               |

| <b>BBB Data Integrity Test</b>                                            |                                                            |                                      | <b>GYVO0: 1.0V, 1.2V, 1.3V (WARNING, difference in order)</b> |

|                                                                           | Power on all tiles, left to right                          | SC CORE Alive Test, Tile EP <ALIVE>  |                                                               |

|                                                                           | SC Alive Test                                              | SC CORE Alive Test, Tile EP <ALIVE>  |                                                               |

|                                                                           | Test(s) PRBS Test                                          |                                      |                                                               |

|                                                                           | Poweroff: SMB parameter reset                              |                                      |                                                               |

|                                                                           | Poweroff: SMB parameter reset                              |                                      |                                                               |

|                                                                           | Power off all tiles, right to left                         |                                      |                                                               |

| <b>Serial digital readout</b>                                             |                                                            |                                      | <b>GYVO0: 1.0V, 1.2V, 1.3V (WARNING, difference in order)</b> |

|                                                                           | LVOD<0> close switch                                       |                                      |                                                               |

|                                                                           | Link Packet Test                                           |                                      |                                                               |

|                                                                           | Config Data Packet Test                                    |                                      |                                                               |

|                                                                           | Empty Data Packet Test, Dry Mode, Sequencer                |                                      |                                                               |

|                                                                           | Empty Data Packet Test, Dry Mode, External Sync,           |                                      |                                                               |

|                                                                           | Empty Data Packet Test, Dry Mode, Internal Sync, Sequencer |                                      |                                                               |

|                                                                           | Empty Data Packet Test, Make all points, Sequencer         |                                      |                                                               |

|                                                                           | Empty Matrix Test                                          |                                      |                                                               |

|                                                                           | Pixel Matrix Test                                          |                                      |                                                               |

|                                                                           | Pixel Matrix Universe                                      |                                      |                                                               |

|                                                                           | Pixel Digital Pulse Test, 40 MHz                           |                                      |                                                               |

|                                                                           | Pixel Digital Pulse Test, 20 MHz                           |                                      |                                                               |

|                                                                           | Pixel Matrix Digital Pulse Test, with clock going          |                                      |                                                               |

|                                                                           | LVOD<0> open switch                                        |                                      |                                                               |

| <b>Serial digital readout</b>                                             |                                                            |                                      | <b>GYVO0: 1.0V, 1.2V (WARNING, difference in order)</b>       |

|                                                                           | Power on all tiles, left to right                          | Data Readout Test, Functional        |                                                               |

|                                                                           | Data Readout Test                                          | Data Readout Test, Stress            |                                                               |

|                                                                           | Power off all tiles, right to left                         |                                      |                                                               |

| <b>Thermal special features test</b>                                      |                                                            |                                      |                                                               |

|                                                                           | LVOD<0> close switch                                       |                                      |                                                               |

|                                                                           | Inductor Memory integrity Test                             |                                      |                                                               |

|                                                                           | Temperature Max Counter Test                               |                                      |                                                               |

|                                                                           | LVOD<0> open switch                                        |                                      |                                                               |

# Qualification of MOSAIX

## The Challenge(s)

# Qualification Infrastructure

# Pre-Silicon Verification

# Wafer probing @ CERN DSF

## Status

- Two probe setups

- Both probers are fitted for:

- impedance measurements

- power ramping

- functional testing

- All equipment acquired and at CERN

- Contact and automation testing with pad wafers:

**ONGOING**

### **CERN prober** – Standard cantilever needle probing

- Probe card: 1x **DELIVERED**, 2x **ARRIVING SOON**

- Functional tests with emulator: **ONGOING**

### **MIT prober** – High-speed vertical needle probing (R&D)

- Studies on high-speed probing: **DONE**

- Probe card: **ORDERED**, expected delivery EOY (single-segment) and January 2026 (multi-segment)

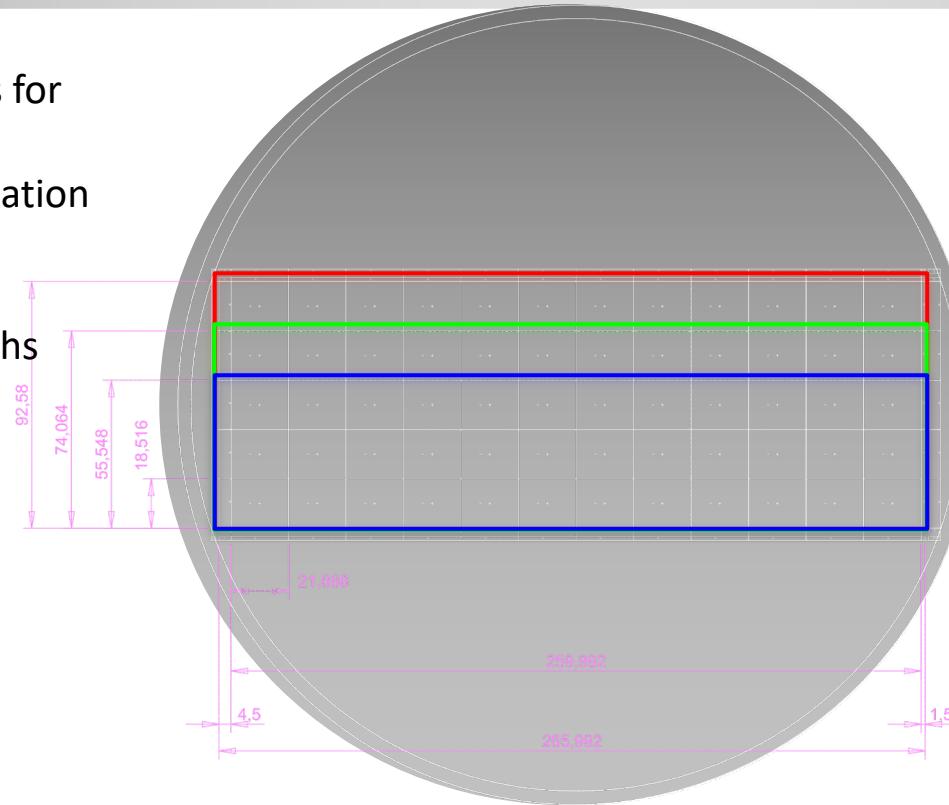

# MOSAIX Core Specs

- 93% sensitive area

- 0.7% modularity

- 144 tiles

- 4.4 MHz/cm<sup>2</sup> particle rate

- 30.72 Gb/s off-chip data transmission

- minimum 2  $\mu$ s integration time

- < 40 mW/cm<sup>2</sup>

- 1013 NIEL (1 MeV neq cm<sup>-2</sup> )

- 10 kGray TID

- Triple modular redundancy

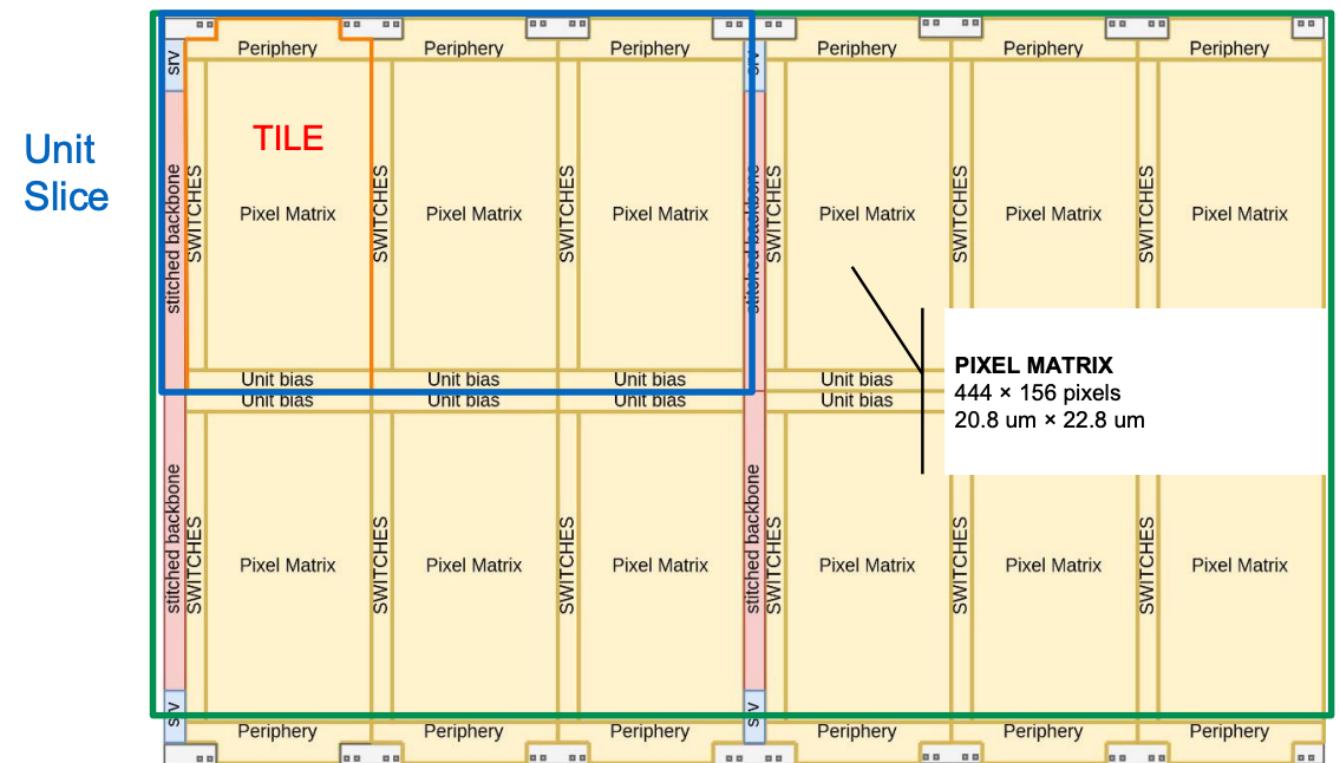

- 20.8 x 22.8  $\mu$ m<sup>2</sup> pixel size

- 444 x 156 pixels per tile

- Detection efficiency > 99%

- Fake-hit rate: < 0.1 pixel<sup>-1</sup>s<sup>-1</sup>

# MOSAIX

# Detector R&D

## Production: ER2 & ER3

Now

### Engineering Run 2

- Different pixel variants for operational margins

- Design in-depth verification ongoing

- 33 wafers: 4 months

- 25 pad wafers: 3 months

- 1 month for dicing

|     |     |     |      |      |      |

|-----|-----|-----|------|------|------|

| PX1 | PX2 | PX3 | PX4  | PX5  | PX6  |

| PX7 | PX8 | PX9 | PX10 | PX11 | PX12 |

Q3 2026

### Engineering Run 3

- Final pixel variant

- Functionally identical to ER2

- ER2 implementation procedure and scripts identical for ER3-For ER3 much shorter design and verification

- As little as 6 wafers needed

|   |   |   |   |   |   |

|---|---|---|---|---|---|

| ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? |

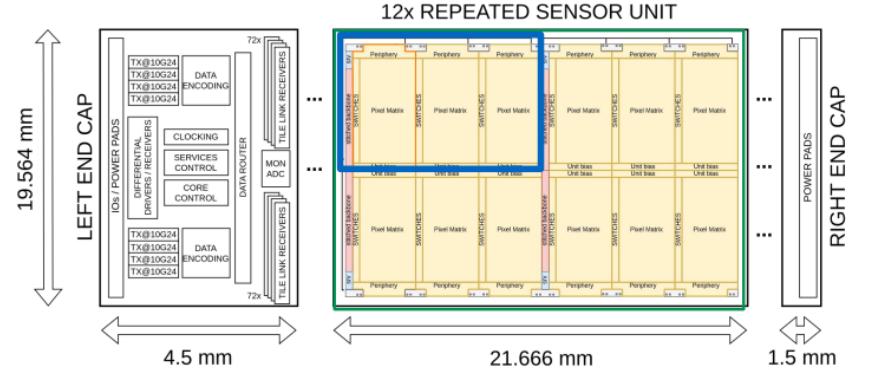

# Simplified overview

- 12 RSUs

- 4 unit slices per RSU

- 1 service node per unit slice

- 12 tiles per RSU (6 top & 6 bottom)

- 4 readout regions per tile

- Combined into 1 tile readout link

RSU

Unit Slice