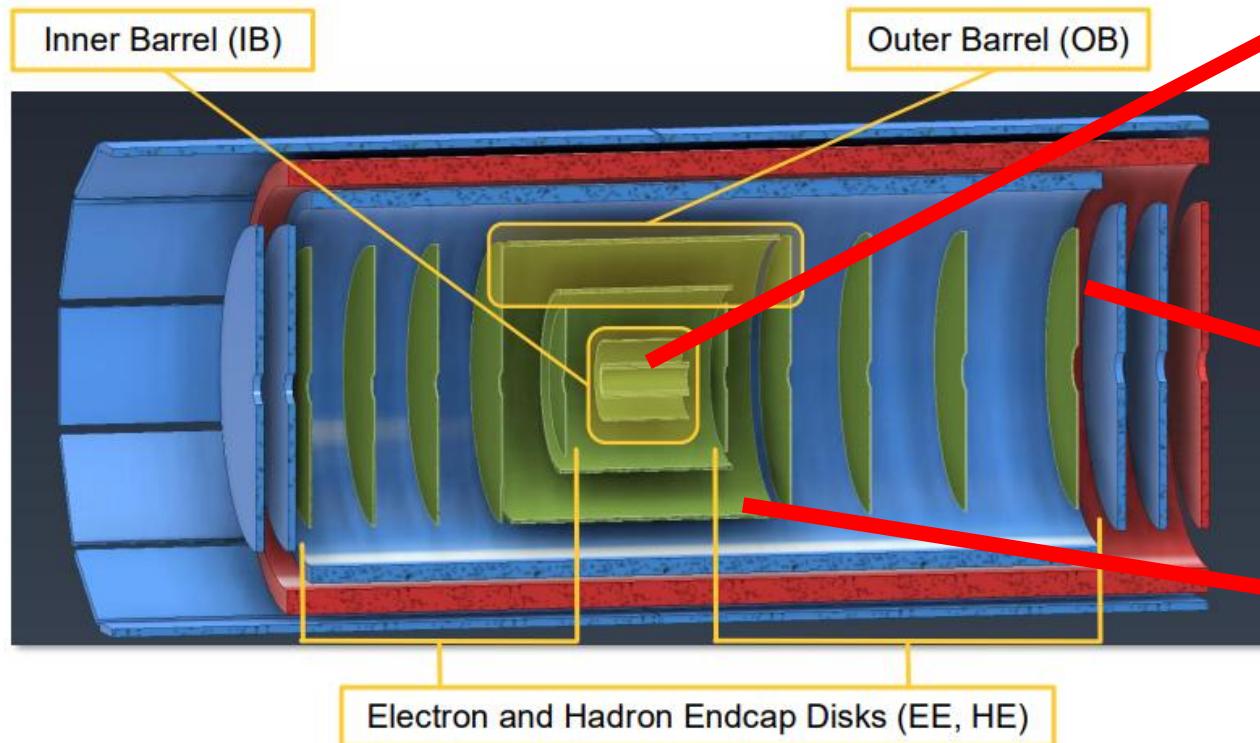

# Outer Barrel System

Electron-Ion Collider

# Introduction

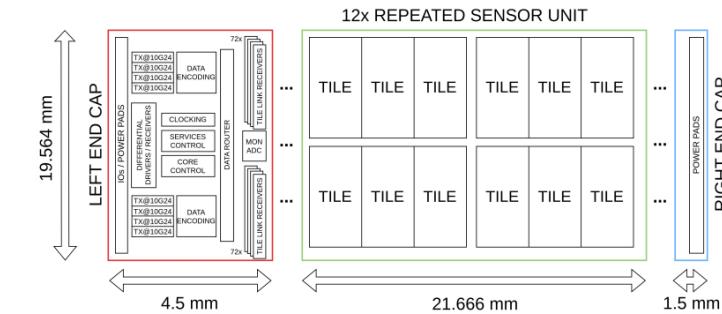

## SVT Silicon Scheme

### Inner Barrel

- Thinned silicon bent around beampipe

- Use wafer-scale MOSAIX from ITS3

### Outer Barrel and Discs

- Smaller Version of MOSAIX with minimum necessary changes (EIC-LAS)

- Supporting AncASIC

# AncASIC and LAS

Electron-Ion Collider

# Ancillary ASIC

## Why AncASIC?

- Some MOSAIX/LAS features require adaptation to stave/disc operation:

- Point-to-point slow control

- Point-to-point powering

- Precise negative back bias

- May be technically unfeasible to integrate these features in the LAS

- Limited prototyping

- MOSAIX schedule is an external dependency

- For these reasons, develop supporting ASIC instead

<https://ep-news.web.cern.ch/content/alice-its3-clears-major-milestone>

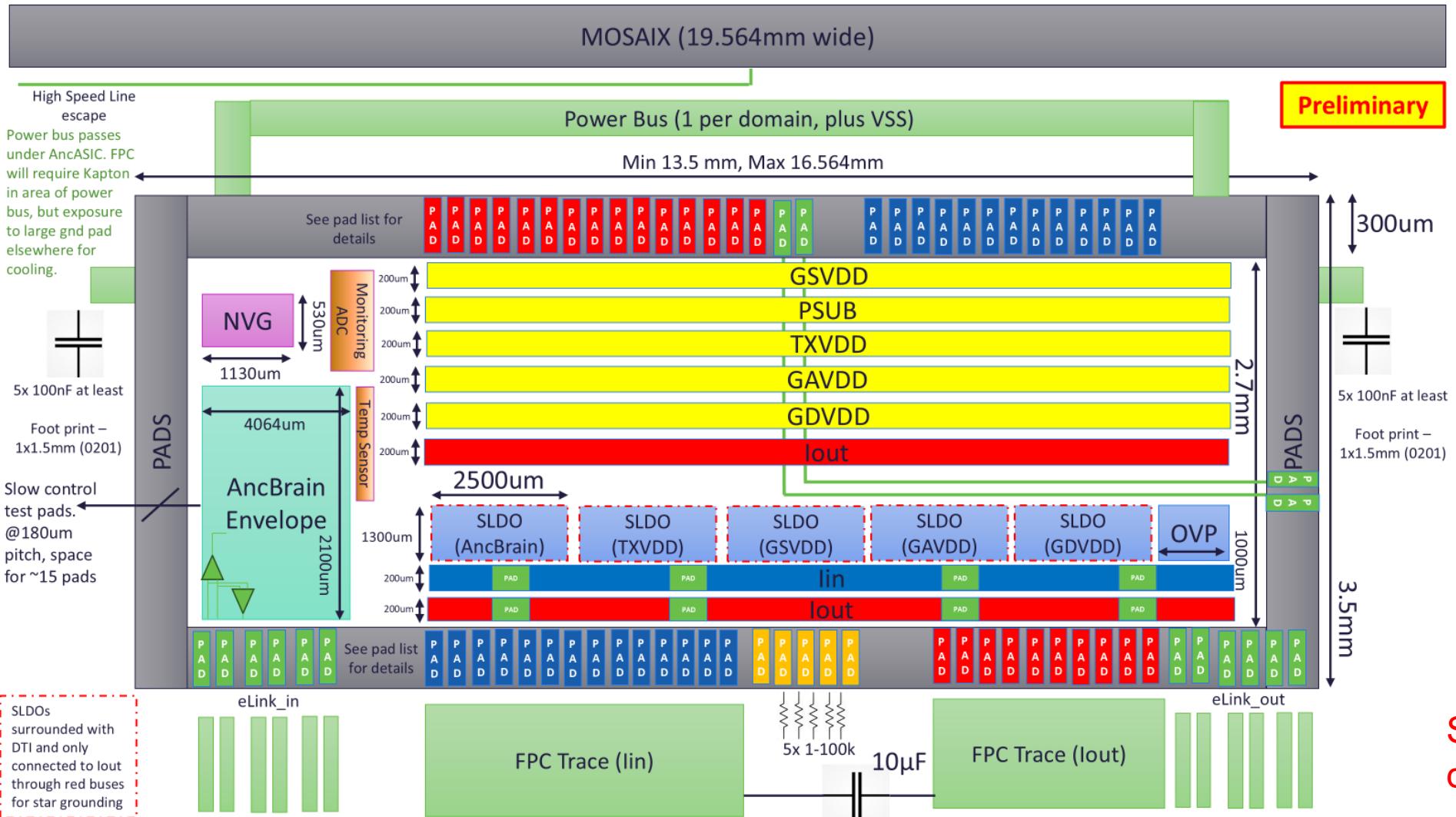

MOSAIX

# Ancillary ASIC

## Why AncASIC?

- Some MOSAIX/LAS features require adaptation to stave/disc operation:

- Point-to-point slow control

- Point-to-point powering

- Precise negative sensor bias

- May be technically unfeasible to integrate these features in the LAS

- Limited prototyping

- MOSAIX schedule is an external dependency

- For these reasons, develop supporting ASIC instead

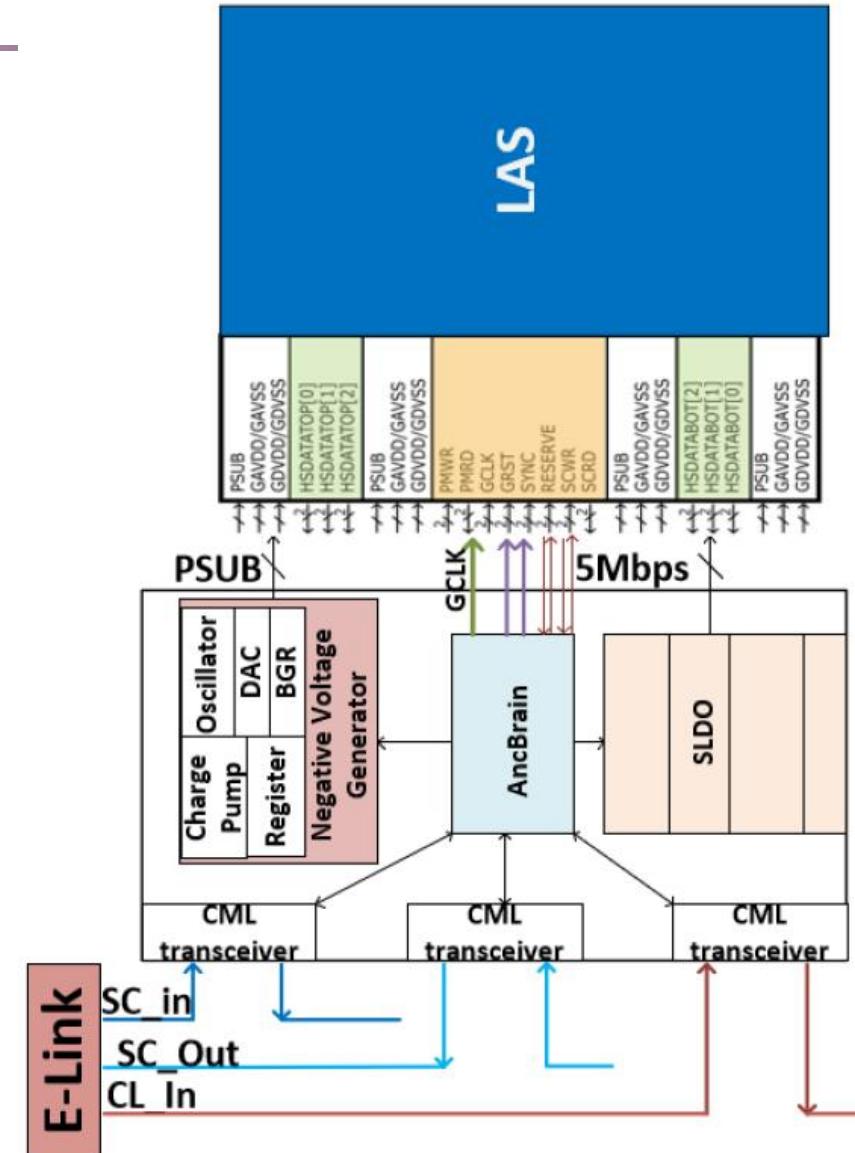

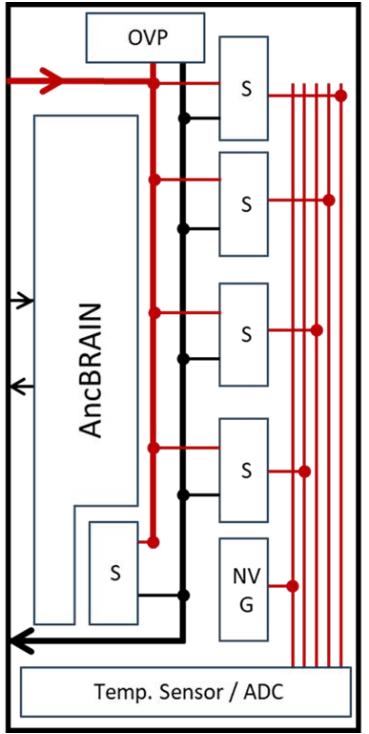

- Serialised Slow Control interface from EIC-LAS to IpGBT

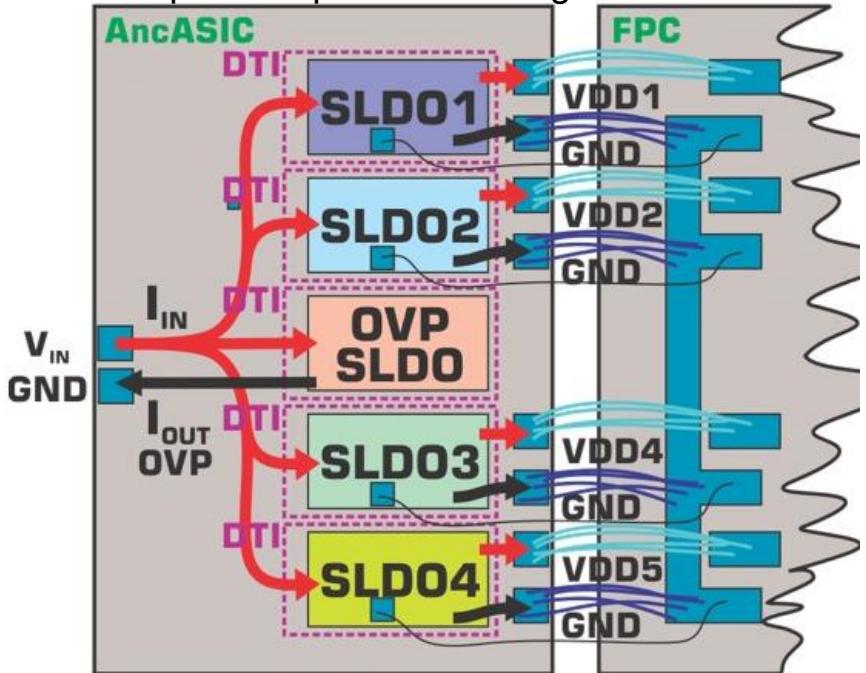

- SLD0 for serial powering

- Local Negative Voltage Generator

- Develop independent supporting chip

- Development decoupled from MOSAIX availability

- No modification of MOSAIX needed

- 110nm XFAB process

- 4 MPW runs a year

- Cost effective

# Ancillary ASIC

## Why AncASIC?

- Some MOSAIX/LAS features require adaptation to stave/disc operation:

- Point-to-point slow control

- Point-to-point powering

- Precise negative back bias

- May be technically unfeasible to integrate these features in the LAS

- Limited prototyping

- MOSAIX schedule is an external dependency

- For these reasons, develop supporting ASIC instead

# AncASIC - Updated Plan

Still being

developed...

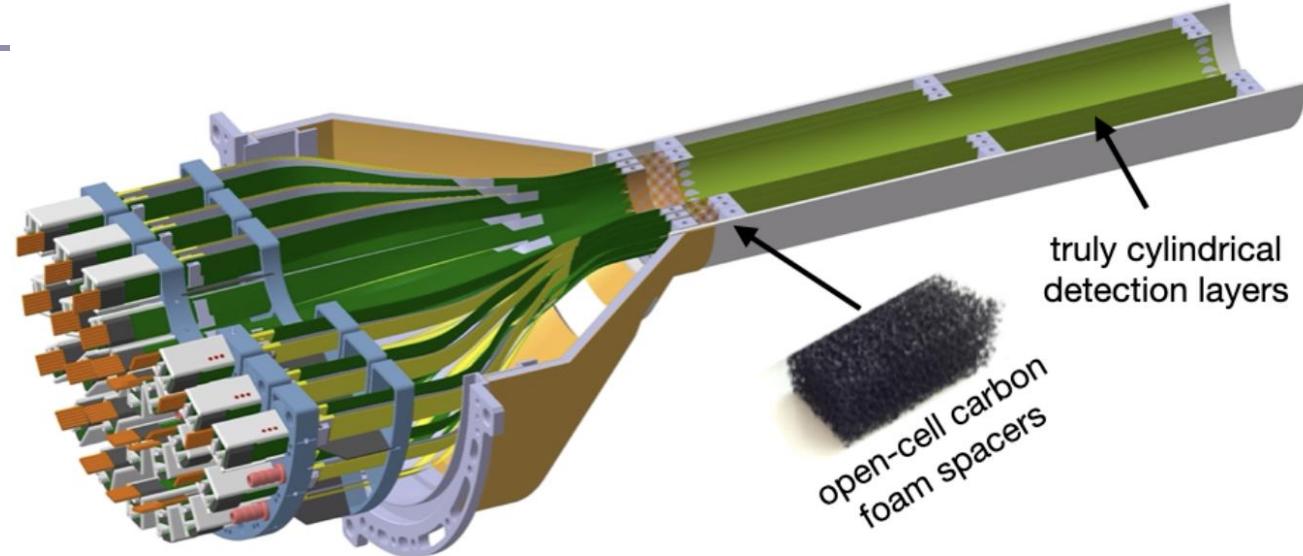

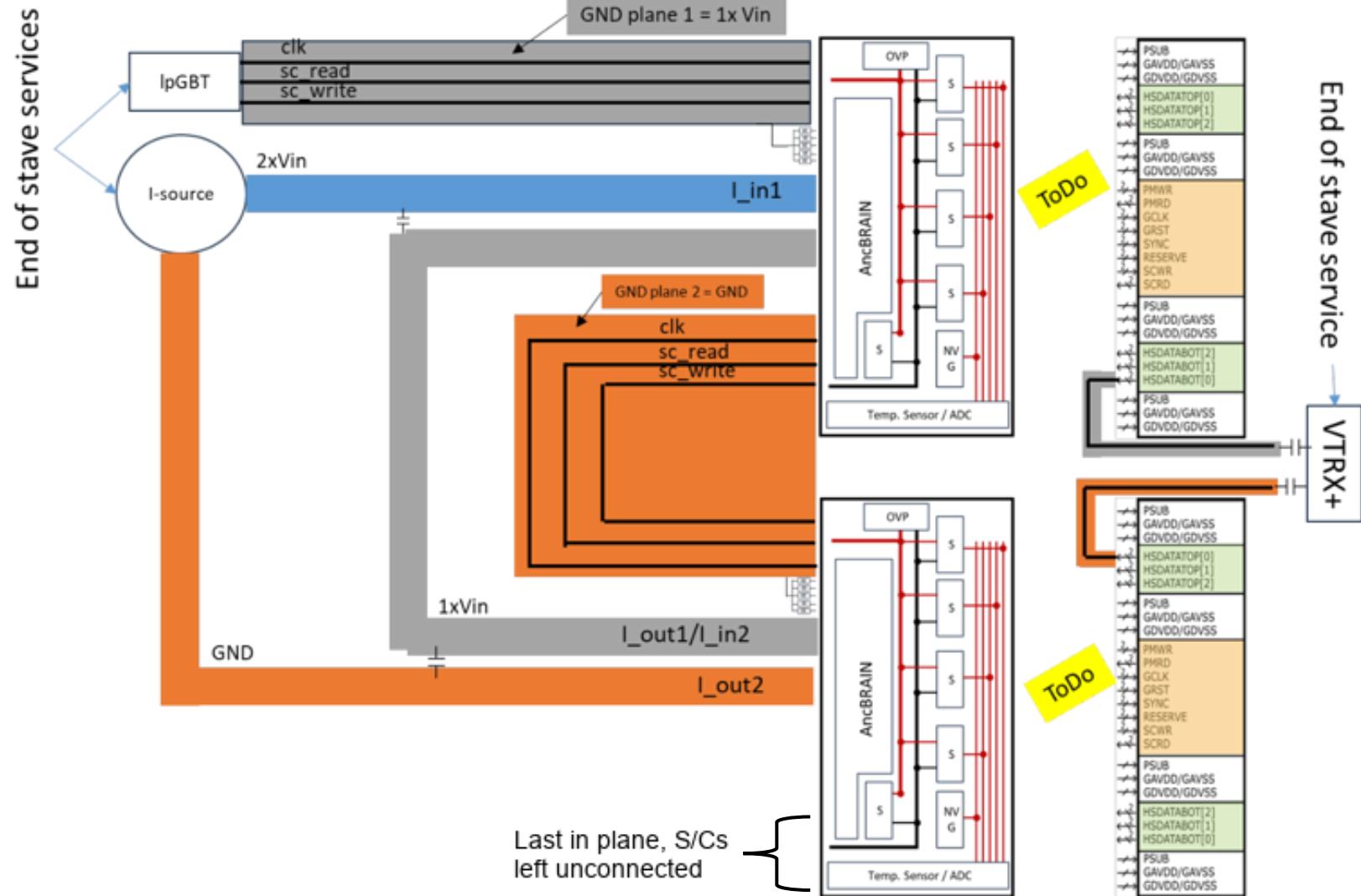

# FPC

Electron-Ion Collider

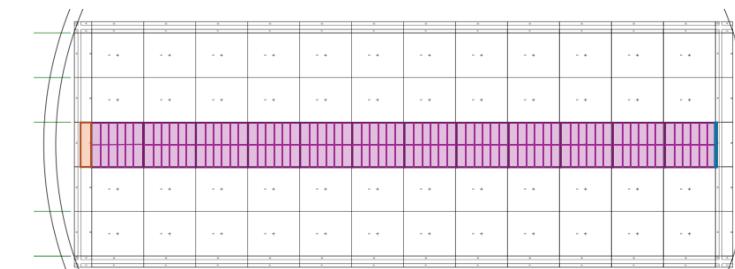

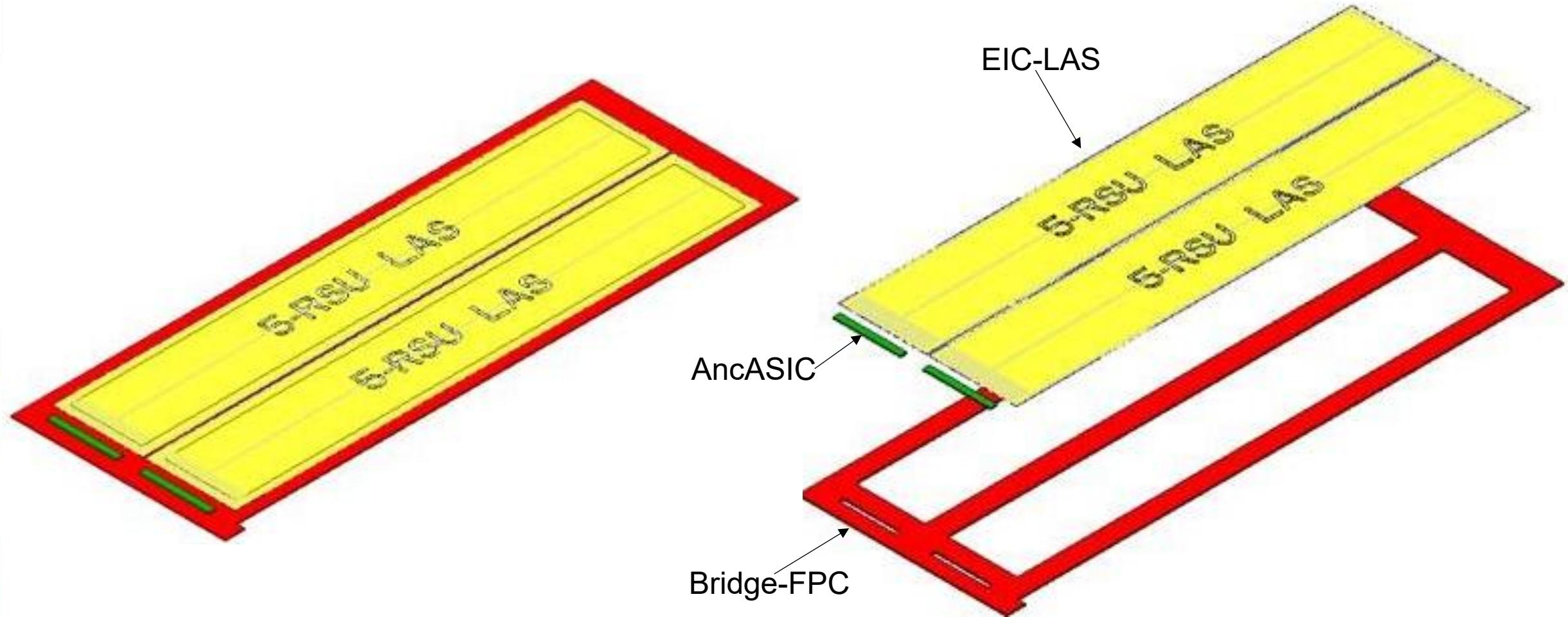

# OB Module on Bridge-FPC

# OB Module Connections

Topological sketch

$I_{in} = \text{const}$

clk, sc\_read, sc\_write:

AC or DC coupled?

# From and To AncBrain

## Summary (ePortTX.pptx / ePortRx.pptx)

Main questions:

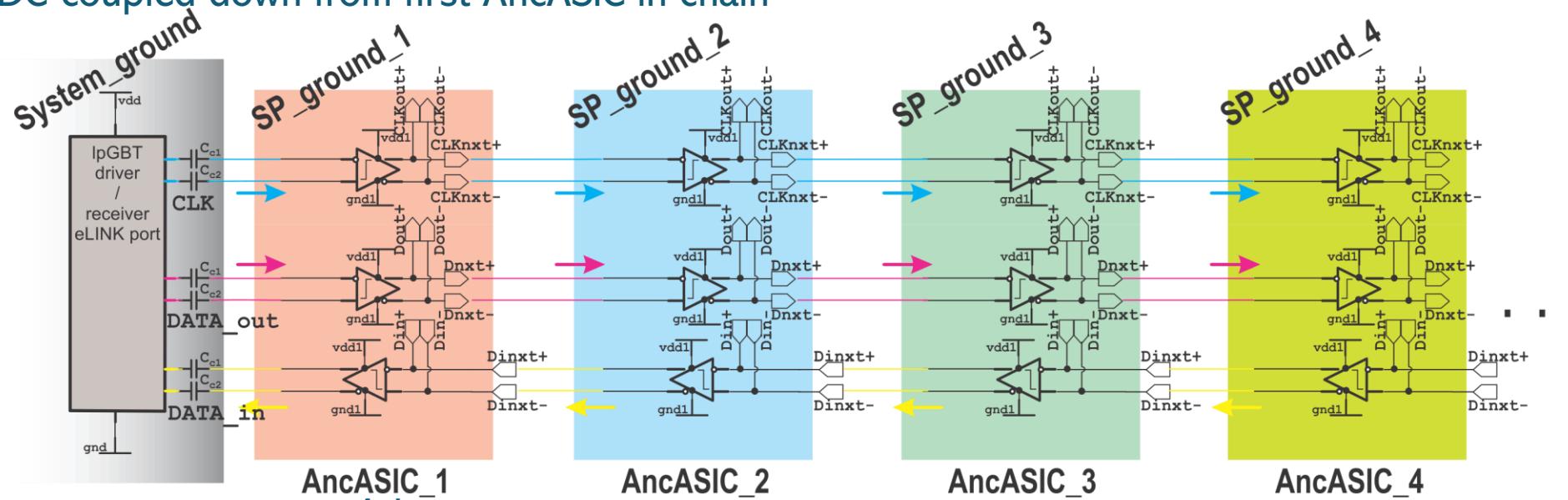

- (2) where AC and DC coupling should be used and how wired to EPort Group / eLinks ?

- Proposal:

- AC-coupled only to IpGBT (up-link and down-link), with coupling capacitors next to IpGBT

- DC-coupled down from first AncASIC in chain

**Advantages:**

- Best for long chain of AncASICs,

- All but first AncASIC can entirely stop transmission

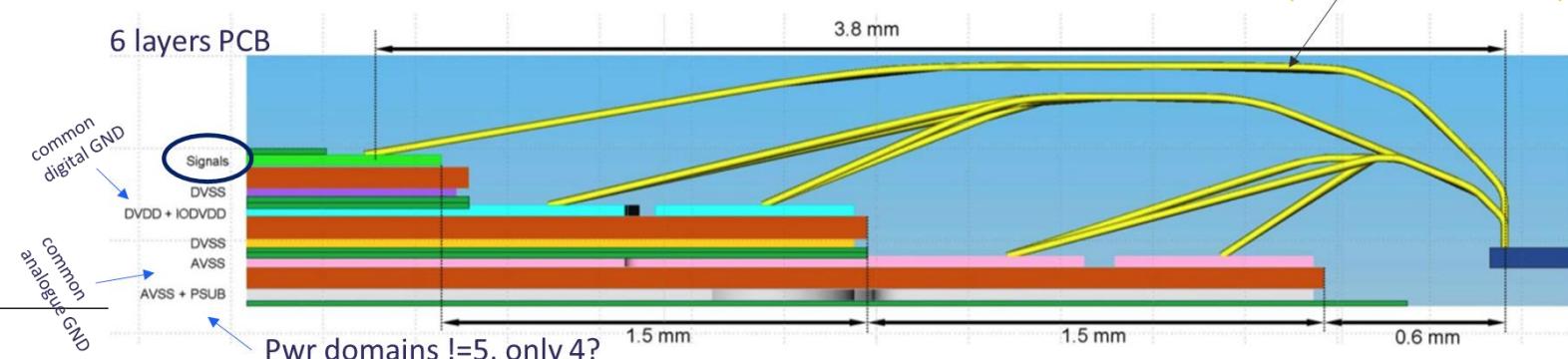

# Grounding: AncAsic – LAS

GSVDD/GSVSS

GAVDD/GAVSS

GDVDD/GDVSS

TXVDD/TXVSS

PSUB

HS DATA

CTRL,CLK, ETC

Common gnd? Yes?

Or common analogue gnd

and common digital gnd? No?

G.Deptuch <https://indico.bnl.gov/event/30317/>

MOSAIX (From ITS3 TDR)

# Beyond the FPC...

Electron-Ion Collider

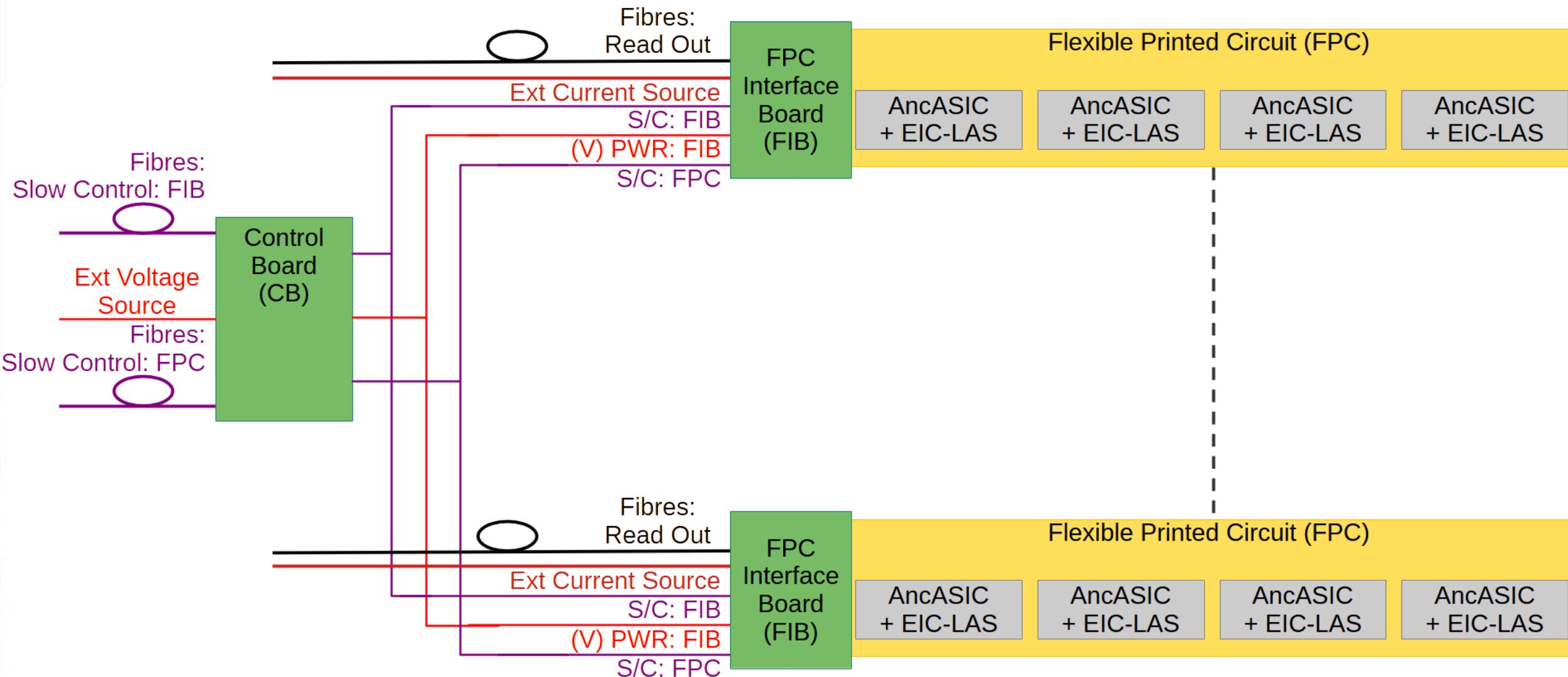

# Basic OB/Disk architecture

# Beyond the CB and FIBs

---

- All connections exiting the SVT volume go via a patch panel (PP).

- e-side and h-side PP used on all staves.

- From the PPs:

- FIB power connects to current sources (1 channel per L3 FIB, 2 channels per L4 FIB).

- FIB fibres (HS data) connect to a data aggregator board. Prior to being received at the control room.

- CB power connects to voltage sources (1+ CB per channel).

- CB fibres (S/Cs) connect to an aggregator board.