# Fast Readout Control for the Upgraded Readout Architecture LHCb of the LHCb Experiment at CERN

F. ALESSIO, R. JACOBSSON

CERN, Geneva, Switzerland on behalf of the LHCb Collaboration

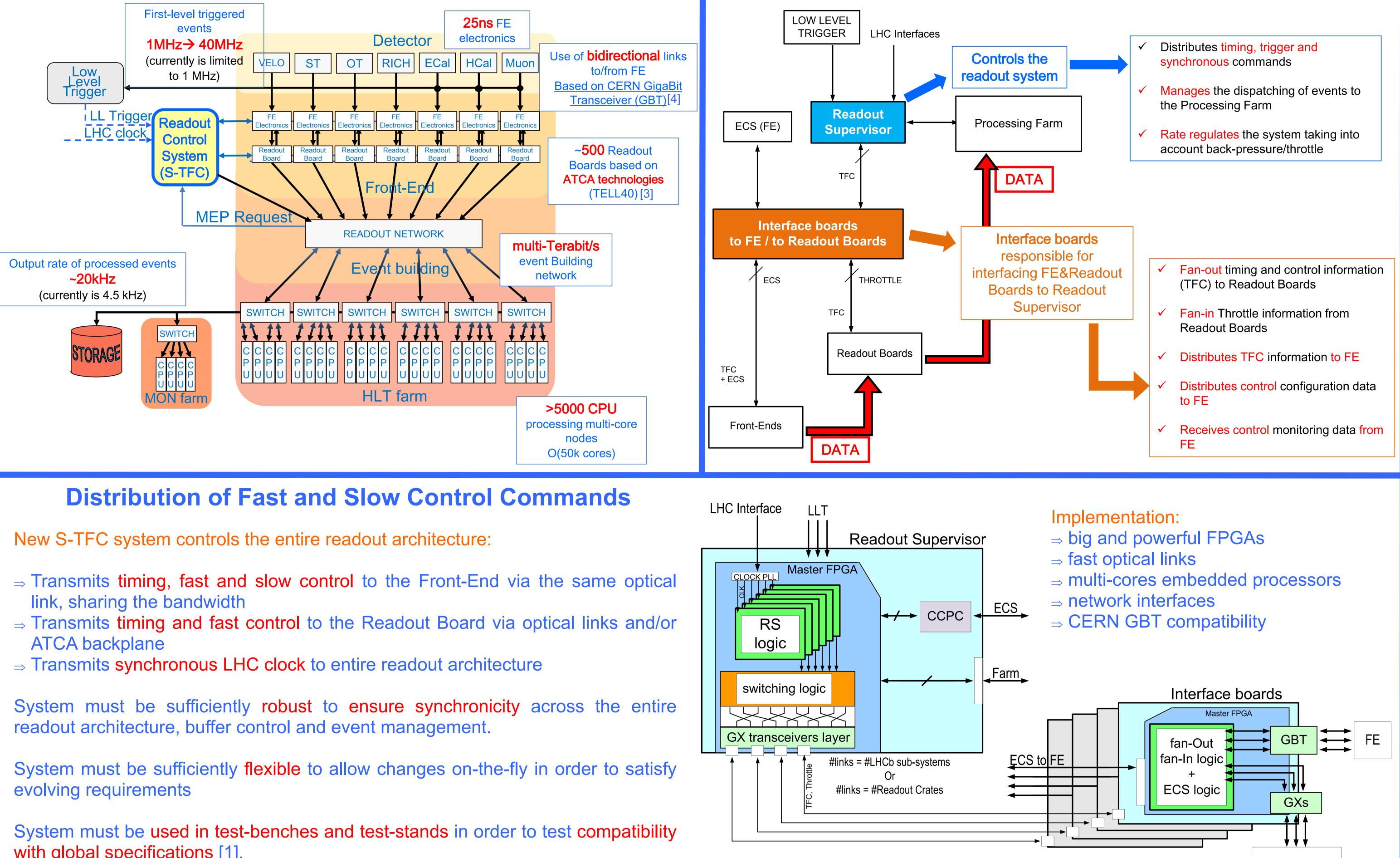

## The LHCb Upgraded Readout Architecture

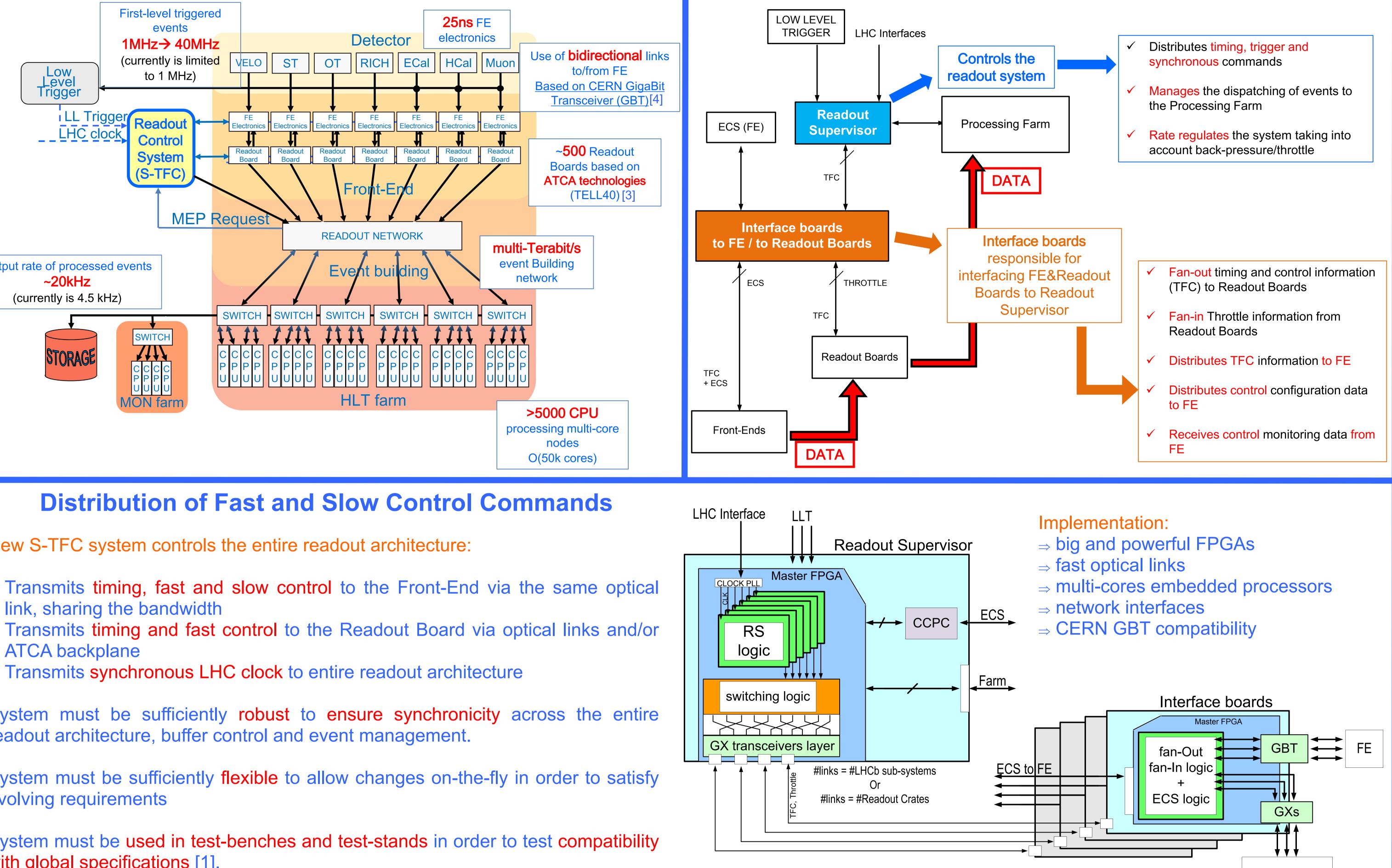

The New Timing and Fast Readout Control System (S-TFC)

with global specifications [1].

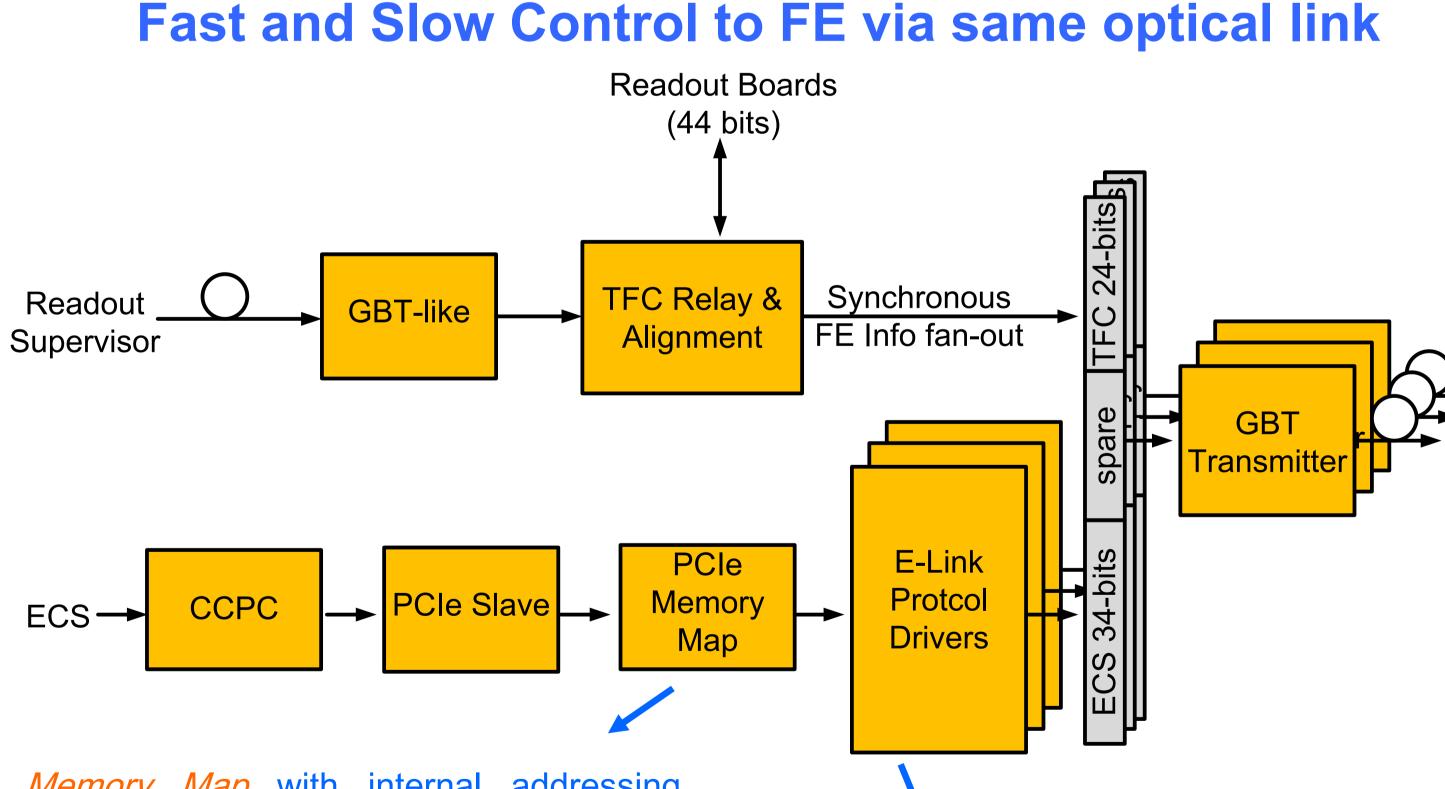

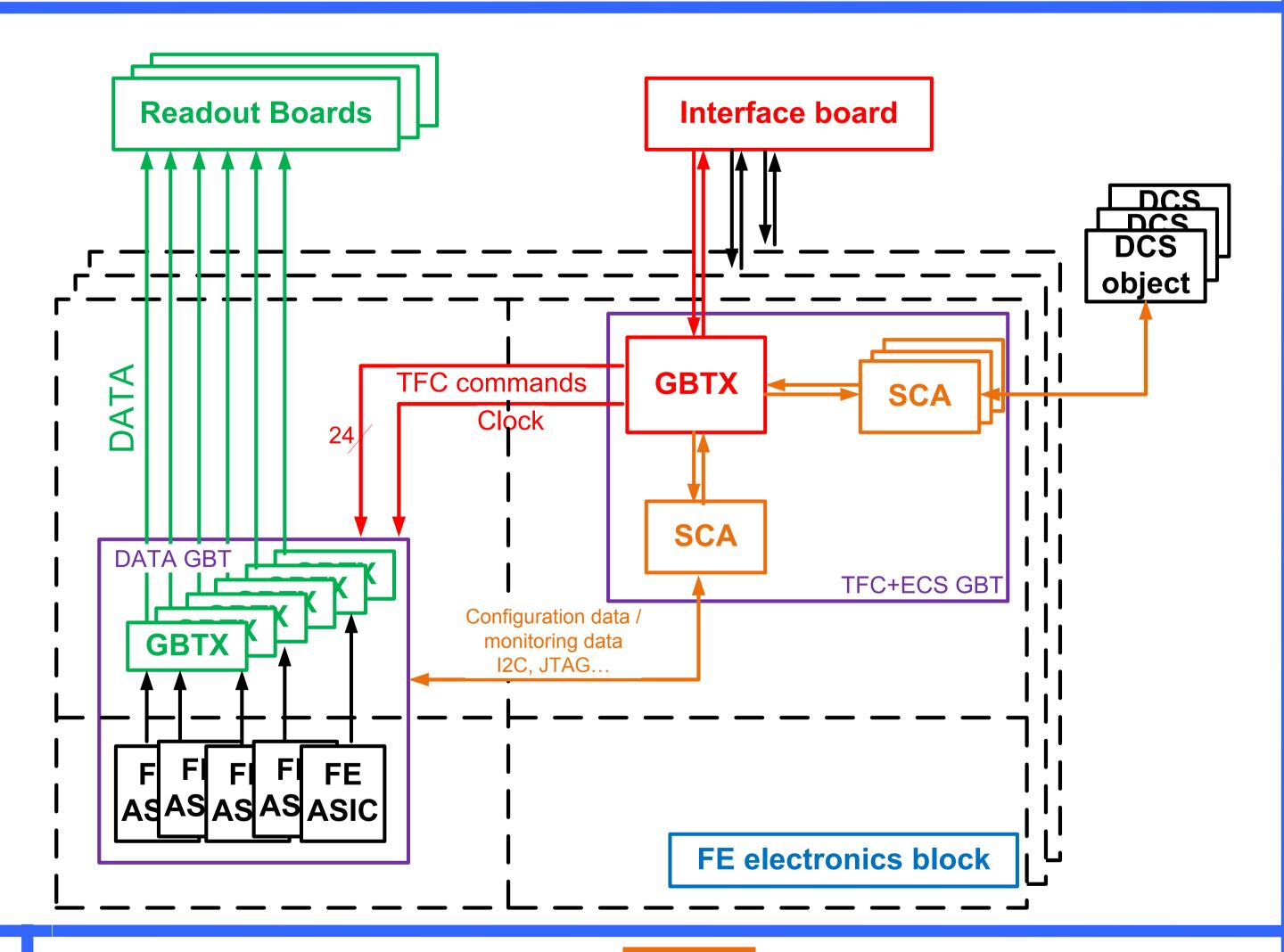

*Memory Map* with internal addressing scheme for GBT-SCA chips + FE chips addressing, e-link addressing and bus type: content of memory loaded from ECS

Protocol drivers build GBT-SCA packets with addressing scheme and bus type for associated GBT-SCA user busses to selected FE chip (GBT-SCA supported protocols)

Clock generators

ONLINE

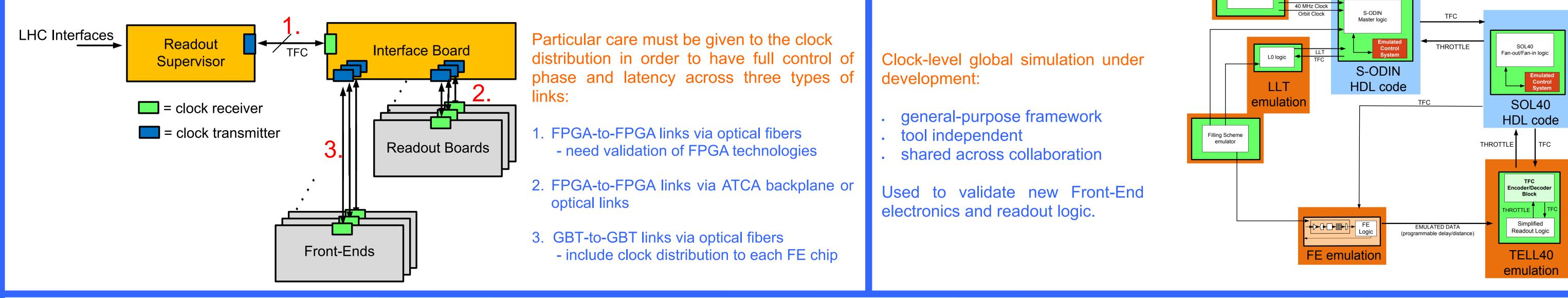

### **Clock Distribution**

### References:

[1] K. Wyllie, et al., "Electronics Architecture of the LHCb Upgrade", CERN LHCb Public Note, LHCb-PUB-2011-011

[2] F. Alessio, R. Jacobsson, "System-level specifications of the Timing and Fast Control system for the LHCb Upgrade", CERN LHCb Public Note, LHCb-PUB-2012-001

[3] J-P Cachemiche et al., "Study for the LHCb upgrade readout board", JINST 5 (2010) C12036

[4] Moreira P et al., "The GBT Project", Proceedings of TWEPP09, pp. 342-346