## Nalu Scientific: Advanced Micro Electronics for Particle Physics

Isar Mostafanezhad, Ph.D.

Founder and CEO, Nalu Scientific, LLC

July 9, 2019, <u>isar@naluscientific.com</u>

Supported by DE-SC0019531, SC0019527, SC0015231, SC0017833

Waveform Digitizer SoCs for Single Photon Time of Flight Detection: Compact, Low Cost, Low Power

#### **<u>1. Various Front-end Chips:</u>**

- Event based digitizer+DSP

- 4-32 channel scope on chip

- 1-15 Gsa/s, 12 bit res.

- Low SWaP

- Low cost

- User friendly

- 2. Integration:

- SiPMPMT

- LAPPD

- Antenna arrays

**3a. Main application:** Particle collider experiments (Belle II at KEK in Japan)

#### **3b. Other applications:**

- Beam diagnostics

- Plasma/Fusion diagnostics

- Lidar

- Medical imaging

# About Nalu Scientific

#### **Integrated Circuits Design**

Analog + digital System-on-Chip (SoC) **Digital implementation**

#### Hardware Design

Field Programmable Gate Arrays (FPGA) Complex multi-layer Printed Circuit Board (PCBs)

#### Expertise in:

Time of Flight (ToF) measurements Fast timing Radiation detection **Readout electronics for Particle Physics**

### Team

Isar M. Founder and CEO UH PhD EE **3x Entrepreneur**

Ben R.

Staff Physicist

PhD Phys

Particle Physics Guru

Luca M. Senior Engineer PhD EE, 20+ vrs IC Design Lead

Chris C.

Design Engineer

BS CE

Agile R&D

Dean U. Senior Engineer 30+ yrs experience Digital IC Design

Angela A.

Office Manager

Admin Guru

Senior RF Engineer 10+ vrs experience High Frequency Design

Marcus L.

SW/PM

Advisors

Shawn U. Gov. Relations

Craig O.

Prof. Gary V. UH Subcontract

+ 3 Postdocs and 3 PhD candidates at University of Hawaii

Kenneth L. EE

Technology Analysis Vertical Market Analysis

Ryan O. Media Consultant

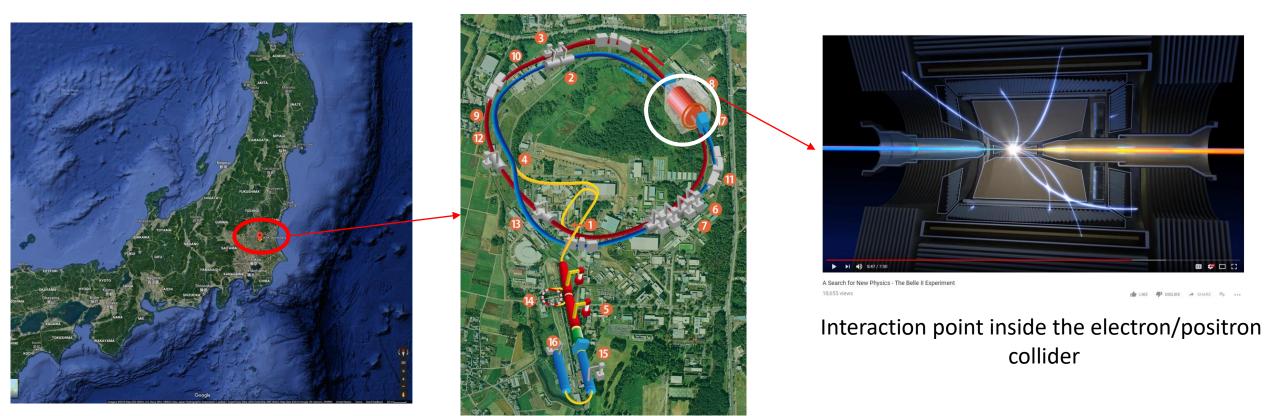

## Where did we start? A Search for New Physics – The Belle II Experiment

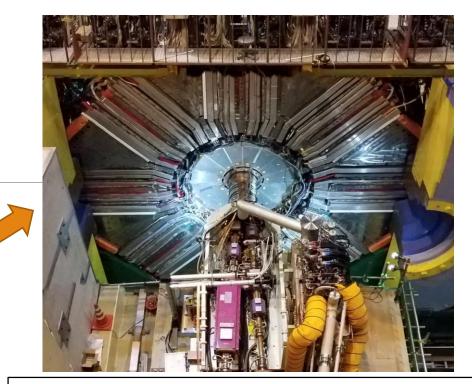

Tsubuka City Located 60 mi north of Tokyo

High Energy Accelerator Research Facility (KEK) in Tsukuba

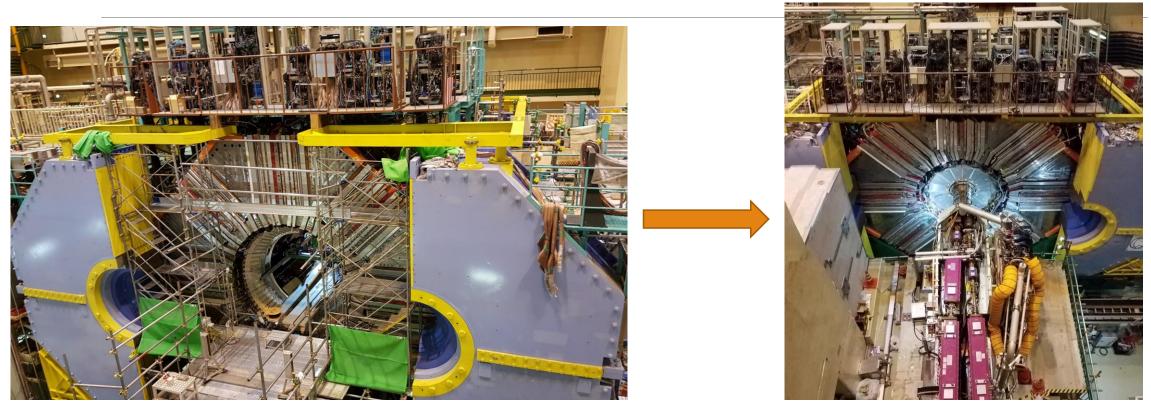

## Some History: Belle II Upgrade is a 26 Country, 900+ member Collaboration

## 2015

2018

Belle II: e+ e- experiment at 40x luminosity of Belle -> Detector needs to operate at severe beam background

## Lesson 1:

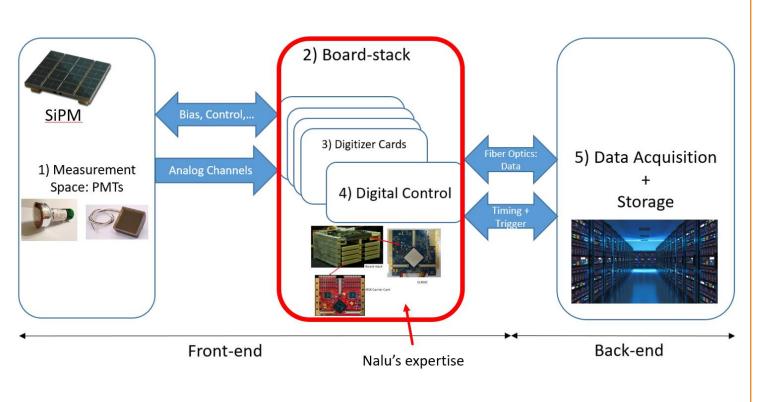

## How does a Particle Physics Experiment Work?

## Lesson 2: Opportunities

Next gen Particle Physics electronics need to be:

- Radiation hard

- High performance

- Low cost, low power

- And user friendly

Solution: New System-on-Chip Integrated Circuit Design

**Opportunity**: Not many commercial options available

# Benefits of Higher Integration - SoC

#### •Analog memory:

- Sampling always on (1-10 Gsa/s), but at low power

- Digitize only Region of Interest (ROI)

- Long analog buffer -> suitable for large experiments

#### • Digital processing:

- Per channel cost reduction by a factor of 4

- Relax thermal design by 40% reduction in power dissipation

- Trigger time-stamping at the front-end

- Eliminating the need for costly high-end FPGAs

- User friendly: substantially reducing the FPGA firmware development labor

- Reduced complexity and design and cabling effort/cost for the front-end boards

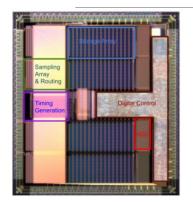

System-on-Chip (SoC)

# Funded SBIR Programs

#### • Various event based digitizers (US DOE):

- ASoC: High speed event based digitizer (4GSa/s, 80mW/ch, 4 channels)

- Phase I, II SBIR: Feb 2016-Nov 2019, Grant: DE-SC0015231

- AARDVARC: High speed event based digitizer (14GSa/s, 80mW/ch, 4 channels)

- Phase I, II SBIR: May 2017-Aug 2020, Grant: DE-SC0017833

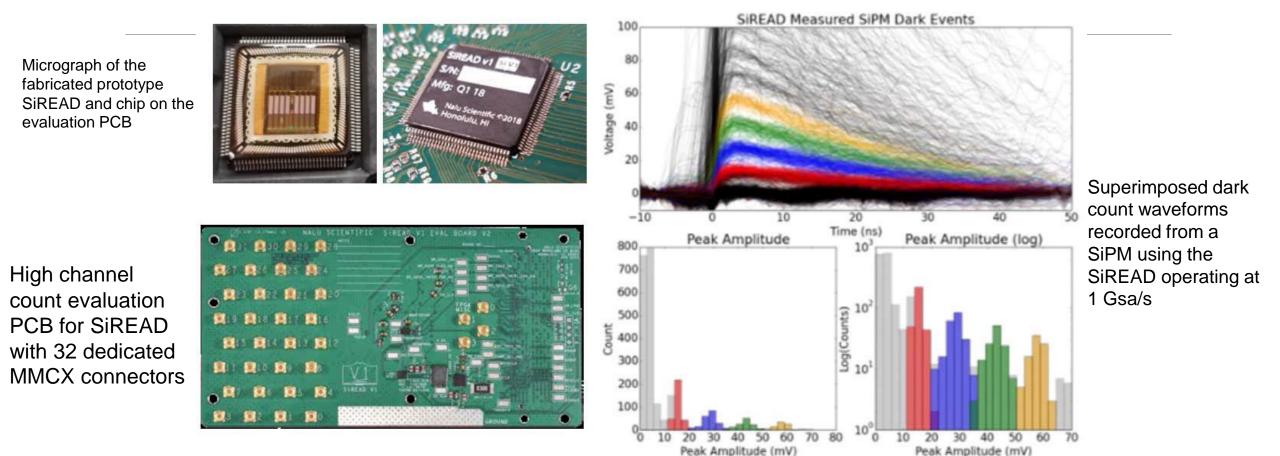

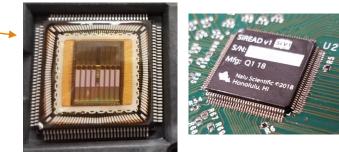

- SiREAD: High channel count digitizer (1GSa/s, 32 channels, 20mW/ch)

- Phase I: Feb 2017-Nov 2017

- AODS: Very compact digitizer with high dynamic range

- Phase I: Feb 2019-Nov 2019, Grant: DE-SC0019531

#### • Advanced Fast Diagnostics Tools (US DOE):

- TR-BHM: Time Resolved Beam Halo Monitor for accelerator beam diagnostics

- Phase I: Feb 2019- Nov 2019, Grant: DE SC0019527

- UPAC: Ultrafast Pixel Array Camera for fusion energy plasma diagnostics

- Phase I: July 2019- June 2020, Grant: DE-SC0019790

#### • Lidar (NASA)

- SWELL: Single-photon-sensitive Waveform Enhanced and Lightweight Lidar

- Phase I: July 2019- Dec 2019 (tentative award pending contract negotiation)

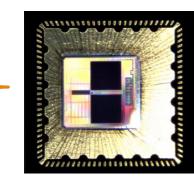

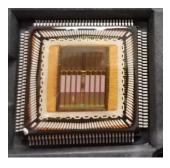

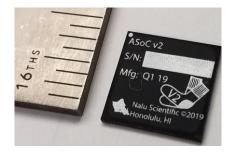

# Nalu Scientific SBIR Project: ASoC

Compact, high performance waveform digitizer

#### Fabricated

| Parameter                     | Spec (measured) |  |  |

|-------------------------------|-----------------|--|--|

| Sample rate                   | 2.4-3.2GSa/s    |  |  |

| Number of Channels            | 4               |  |  |

| Sampling Depth                | 16kSa/channel   |  |  |

| Signal Range                  | 0-2.5V          |  |  |

| Resolution                    | 12 bits*        |  |  |

| Supp <mark>ly V</mark> oltage | 2.5V            |  |  |

| RMS noise                     | ~1 mV           |  |  |

| Digital Clock frequency       | 25MHz           |  |  |

| Timing resolution             | <25ps**         |  |  |

| Power                         | 140mW/channel   |  |  |

| Analog Bandwidth              | 950MHz          |  |  |

#### **Key Contribution:**

- High performance digitizer: 3+ Gsa/s

- Highly integrated

- Commercially available

- 5mm x 5mm die size

Skips 10 windows (640ns)

~600ns separation

#### Live demo at IEEE NSS-MIC 2018

Nalu Scientific- ASIC developments

NALU SCIENTIFIC, LLC-

All chips, are designed with commercial grade tools and licenses and can be sold once commercialized.

#### **NEW DEVELOPMENTS**

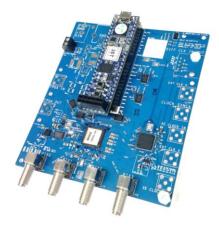

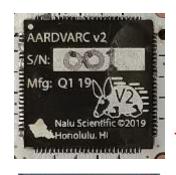

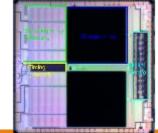

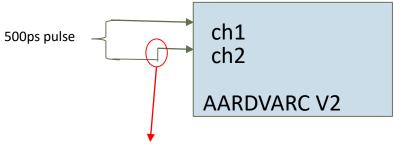

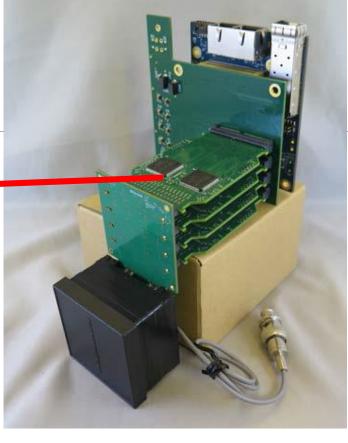

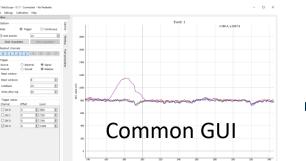

# AARDVARC V2 under test

- AARDVARC V2 fabricated and packaged

- Test board V2 designed, fabricated and assembled

- Lower cost FPGA dev card identified and purchased (x5)

- Test firmware V2 developed

- New software and GUI designed and implemented

| AARDVARC Parameter      | Specification (measured) |  |  |  |

|-------------------------|--------------------------|--|--|--|

| Process node            | 130 nm                   |  |  |  |

| Channels                | 4                        |  |  |  |

| Sampling Rate           | 10-14.5GSa/s*            |  |  |  |

| Storage Samples/ch      | 32768                    |  |  |  |

| Analo <mark>g</mark> BW | >1GHz**                  |  |  |  |

| Dynamic Range           | 1.0 V**                  |  |  |  |

| Time accuracy           | <5 ps***                 |  |  |  |

| Readout                 | Parallel/Fast Serial     |  |  |  |

| ADC bits                | 12                       |  |  |  |

| Power/ch                | 80 mW*                   |  |  |  |

# AARDVARCTest Xilinx A7 FPGA dev

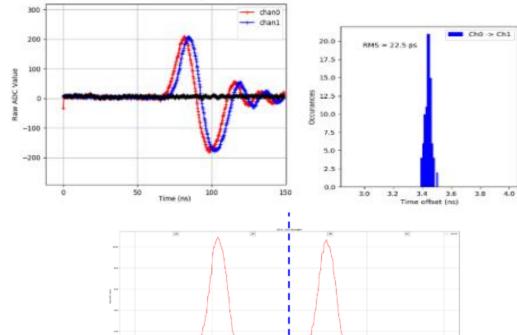

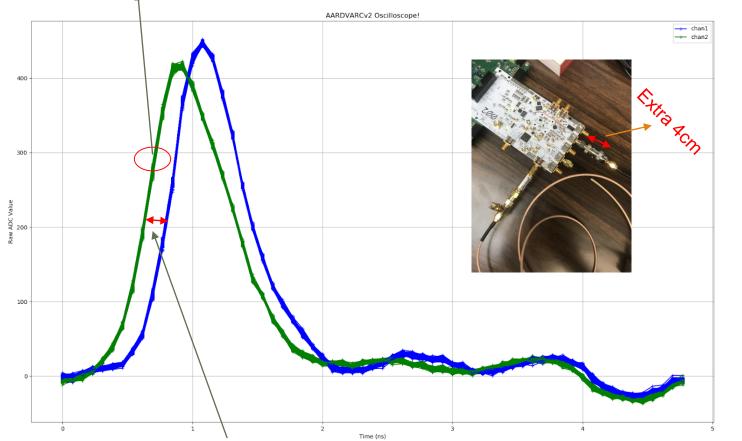

## Overlayed 250 events showing very small timing jitter

#### Two pulses in two channels in 250 events

Pulses created by shunting Si5341 square wave output

Difference in timing created by adding a right angle connector to cable

Extra SMA connector

**Note:** the pulse gen is synced with ASIC sampling clock.

Delay caused by an extra SMA connector ~ 140ps (1-2 Samples at 13 GSa/s) Jitter measured at ~1-2ps

More results to be shown in conferences in the next 2-3 months

# Synergies: LAPPD

In June 2019 we measured LAPPD pulses using ASoC and AARDVARC chips. We are still analyzing the data.

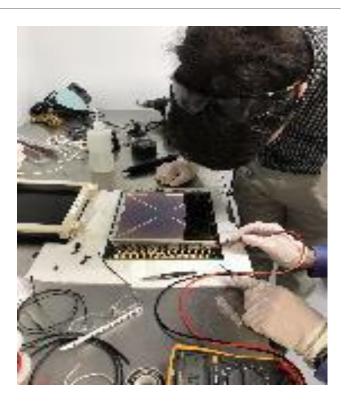

## SiREAD Electronics Evaluation

## MaPMT Readout

Photograph of the 64 channel SiREAD based (2x SiREAD rev.1) readout card as a building block for the 256 MA-PMT readout.

Photograph of the first generation of 256-anode 2" PMT readout for use with mRICH prototype in the Fermilab beam test facility.

## Current SoC-ASIC Projects

| Project  | Sampling<br>Frequency<br>(GHz) | Input<br>BW<br>(GHz) | Buffer Length<br>(Samples) | Number of<br>Channels | Timing<br>Resolution<br>(ps) | Available<br>Date |

|----------|--------------------------------|----------------------|----------------------------|-----------------------|------------------------------|-------------------|

| ASoC     | 3-5                            | 0.8                  | 32k                        | 8                     | 35                           | Rev 2 avail       |

| Siread   | 1-3                            | 0.6                  | 4k                         | 64                    | 80-120                       | Rev 1 avail       |

| AARDVARC | 6-10                           | 2.5                  | 32k                        | 4-8                   | 4-8                          | Rev 2 avail       |

| AOD      | 1-2                            | 1                    | 8k                         | 1-4                   | 100-200                      | Nov 2019          |

- **ASoC**: Analog to digital converter System-on-Chip

- SiREAD: SiPM specialized readout chip with bias and control —

- **AARDVARC**: Variable rate readout chip for fast timing and low deadtime

- AODS: Low density digitizer with High Dynamic Range (HDR) option

All chips, are designed with commercial grade tools and licenses and can be sold once commercialized.

# Acknowledgements

**US Department of Energy**

Hawaii Technology Development Corporation (HTDC)

University of Hawaii Department of Physics

Incom, Inc.

# Funding and Collaboration

Nalu office during a recent meeting with IDLAB

#### FY16-20 FY16-20 FY19-20 New possibilities: \$425k Sponsored Research ✓\$3.7M Secured by Nalu ✓ New tech-dev based on UH capabilities ✓ University of Hawaii ✓ 7x SBIR Phase I ✓ Local testing at UH ✓ 4x post docs ✓ 2x SBIR Phase II ✓ Workforce development ✓ 4x graduate students ✓ Various matching grants ✓ Hiring more UH grads ✓ US-JAPAN Collaboration ✓ Misc. materials and supplies Misc. contracts $\checkmark$ 1x MS and 2x PhDs had their first jobs at Nalu Scientific.

# Why Hawaii?

#### Strategic location!

- Continental US

- Asia

#### University of Hawaii

- Collaboration

- Workforce

- Facilities

- World class faculty

#### Greater impact on State

- Economical (high paying jobs)

- Technological

- "Hawaii Brand"

- Reverse the brain drain

- Lots of resources available

## Good Media Coverage

The problem Mostefanezhad's helping solve is essentia<sup>400</sup> we particle collisions: no small feat, given that the particles billions could fit on the head of a pin, he says — and traper second.

CIVIL BEAT

Isar Mostafanezhad, chief executive of Nalu Scientific, said the High Technology Development Corp. has been instrumental in getting the seven-person company off the ground.

He set up Nalu at the Manoa Innovation Center to develop microchips that would process data from sensors set up close to the point of the collision, inside and around the accelerator's giant cylindrical chamber. The center gave Nalu a location close to UH, with amenties like high-speed and access to meeting rooms, plus a community of entrepreneurs. The price was way below market price for office space, Mostefanezhad says.

#### Startup Pavilion at IMS2019

BESTON

PAVILION

## In the news and events

INNOVATIVE COMPANY Isar Mostaranezhad Founder & CEO Natu Scientific

West Three Treatme

Nilu Scientific might one day help change the world. The Honolul-shased technology company is engineering menabips and

#### Hawaii Biz Magazine Most Innovative Small Biz of the year

Hawaii Congressman Ed Case visit

Booth and AARDVARC Live demo at US-Japan Particle Physics Symposium in Honolulu (April 2019)

Pacific Biz News 40 under 40

**IEEE Young Professionals Panel** IMS2019 - Boston

**Next Top Startup Pitch Competition**

Runner up - IMS2019 - Boston

IPAC 2019 booth- Melbourne