# Front-end electronics for EIC - PID

Isar Mostafanezhad - Nalu Scientific

Gary Varner – University of Hawaii

#### Next Generation Photosensor Readout

- Building upon lessons learned from the development of photosensor readout for the Belle II upgrade (picosecond timing, low-cost, large muon system) and CTA SCT cameras (\$1.40/channel)

- ASIC development important, but firmware and support have been the most critical issues

- UH has partnered with Nalu Scientific team to develop commercial variants (with functional extensions), to provide engineering support

- UH can then focus on strengths of an academic institution for innovation, testing and data analysis

## Current Nalu's SoC-ASIC Projects

| Project  | Sampling<br>Frequency<br>(GHz) | Input<br>BW<br>(GHz) | Buffer Length<br>(Samples) | Number of<br>Channels | Timing<br>Resolution<br>(ps) | Available<br>Date |

|----------|--------------------------------|----------------------|----------------------------|-----------------------|------------------------------|-------------------|

| ASoC     | 3-5                            | 0.8                  | 32k                        | 8                     | 35                           | Rev 2 avail       |

| SiREAD   | 1-3                            | 0.6                  | 4k                         | 64                    | 80-120                       | Rev 1 avail       |

| AARDVARC | 6-10                           | 2.5                  | 32k                        | 4-8                   | 4-8                          | Rev 2 avail       |

| AODS     | 1-2                            | 1                    | 8k                         | 1-4                   | 100-200                      | Nov 2019          |

- ASoC: Analog to digital converter System-on-Chip

- Rev 1 under test Funded Phase II Eval card available

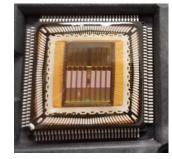

- SiREAD: SiPM specialized readout chip with bias and control

- Rev 1 under test

- AARDVARC: Variable rate readout chip for fast timing and low deadtime

- Rev 1 under test Funded Phase II

All chips, are designed with commercial grade tools and licenses and can be sold once commercialized.

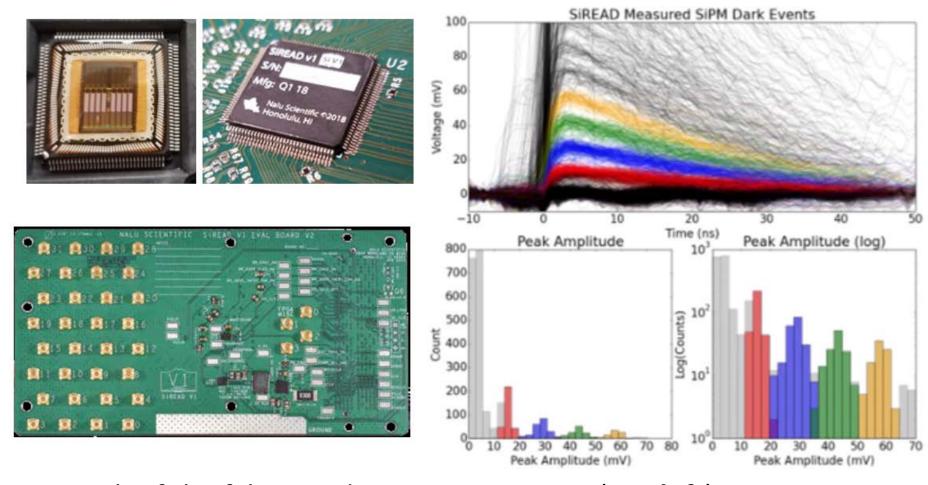

#### SiREAD Electronics Evaluation

Micrograph of the fabricated prototype SiREAD (top left). Prototype SiREAD on the evaluation PCB (top middle). Superimposed dark count waveforms recorded from a SiPM using the SiREAD operating at 1 Gsa/s (right). High channel count evaluation PCB for SiREAD with 32 dedicated MMCX connectors (bottom left).

### PMT Readout

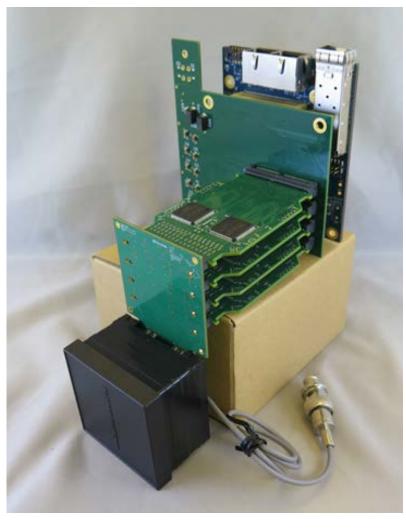

Photograph of the first generation of 256-anode 2" PMT readout for use with mRICH prototype in the Fermilab beam test facility.

Photograph of the 64 channel SiREAD based (2x SiREAD rev.1) readout card as a building block for the 256 MA-PMT readout.

## HW/FW development

- Need for robust firmware development

- Nalu Scientific team provides in-house FW development, with institutional memory

- UH provides comprehensive bench, environment and picosecond laser/photosensor testing

- UH hiring new EE post doc on July 3<sup>rd</sup> (pending hiring paperwork)

- Immediate push is to get SiREAD version of 256 anode PMT readout working; evaluate performance; design more compact version