# Development of the SiREAD based readout solution for the Particle Identification Detectors of the EIC

Shivang Tripathi <sup>a</sup>, Gary Varner <sup>a</sup> Benjamin Rotter <sup>b</sup>, Isar Mostafanezhad <sup>b</sup>

<sup>a</sup> ID Lab, University of Hawaii at Manoa <sup>b</sup> Nalu Scientific, Honolulu

eRD14 PID Consortium Meeting May 25, 2020

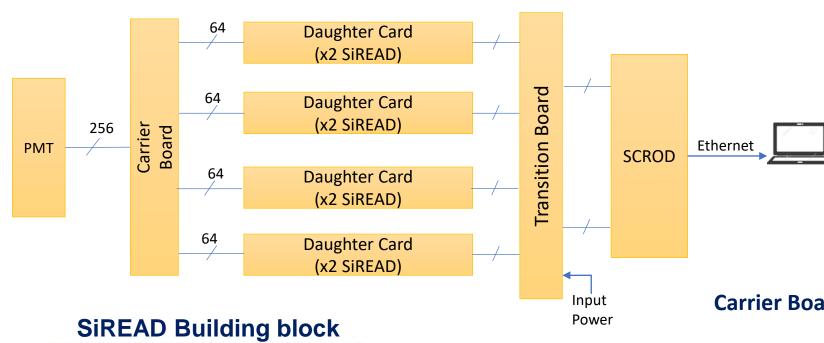

# Readout Electronics for mRICH Detectors

PMT would be mounted on the other side of the Carrier **Board**

## **Carrier Board**

SiREAD DCs x4

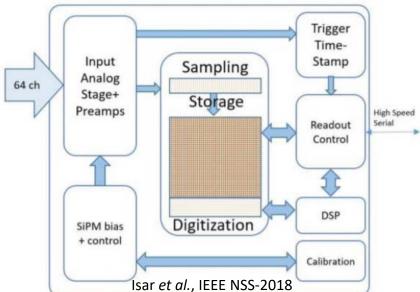

| SiREAD Parameter     | Specifications |

|----------------------|----------------|

| Channels             | 32             |

| Sampling rate        | 1 GSa/s        |

| Storage samples/ch   | 4096           |

| Est. Analog BW       | 0.7-1.1 GHz    |

| RMS voltage noise    | 1.3 mV         |

| Signal voltage range | 2.1 V          |

| ADC on chip          | 12 bits        |

| Readout              | Serial LVDS    |

| Power consumption    | 20-40 mW/ch    |

**Transition Board**

**SCROD**

Input power

optical gigabit transceiver

# **Development Status**

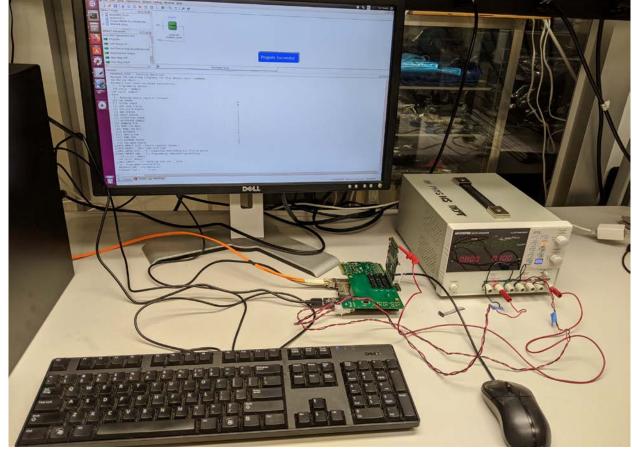

- 25 Nos. of SiREAD Daughter Cards (IDL\_19\_004) have been fabricated

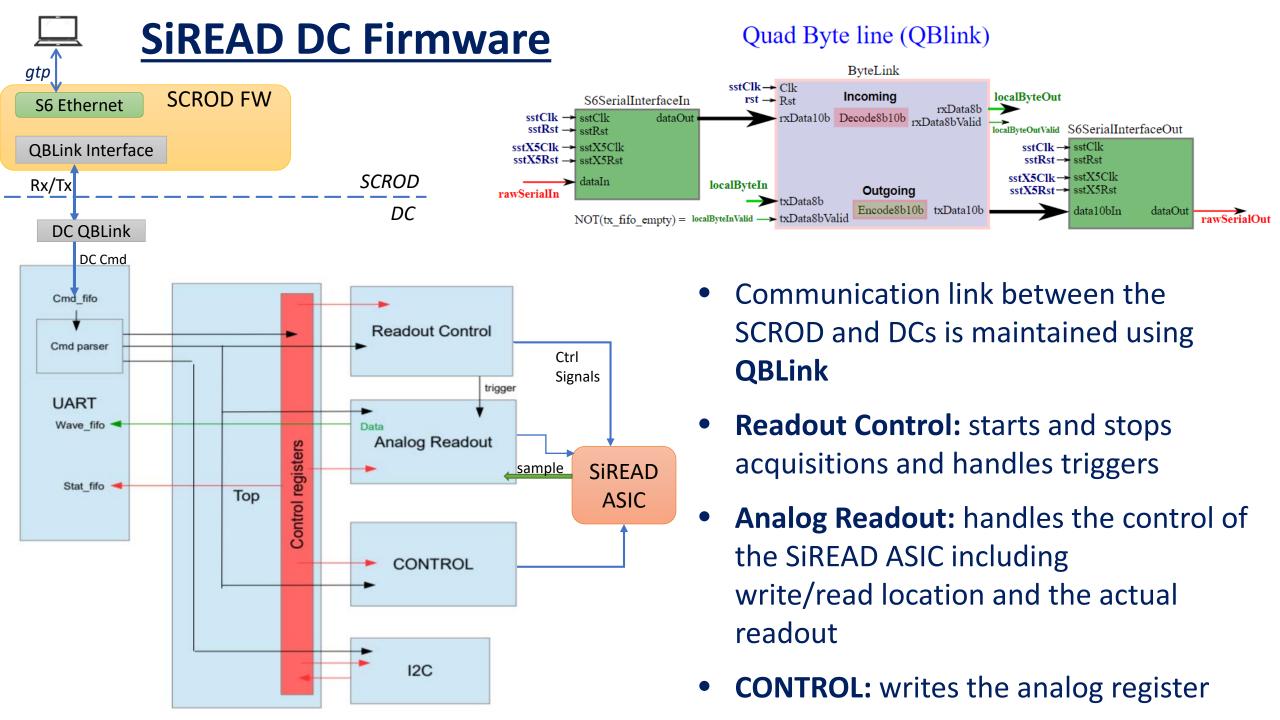

- The first version of the SiREAD DC firmware has been developed and ready for initial testing

- The communication between PC and SCROD FPGA has been tested with old firmware

- Upgradation of the SCROD FW is underway to implement the communication between SCROD and DCs

- Team from Nalu Scientific is actively involved and accelerated the development of firmware

SiREAD Daughter Card

DC powered up and programmed successfully with the first version of the FW

# **Plan Ahead**

| Activities Planned                                                                                                                                                                                                 | Time-line         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Upgradation of SCROD FW                                                                                                                                                                                            | May 2020          |

| <ul> <li>Testing, Verification &amp; debugging of:</li> <li>SCROD communication with PC (optical link, Reg Readback)</li> <li>SCROD communication with DC (QBLink module)</li> <li>DC Register Readback</li> </ul> | Summer 2020       |

| Hardware Test with 4 DCs & PMT                                                                                                                                                                                     | Early Autumn 2020 |

| Characterization of timing, noise and trigger rate performance                                                                                                                                                     | Late Autumn 2020  |