# Recent SOI Detector Test Results 3D Integrated Pixel Sensor with SOI Technology for the ILC

Miho Yamada, <u>myamada@metro-cit.ac.jp</u> (TMCIT)

Shun Ono, Yasuo Arai, Ikuo Kurachi, Toru Tsuboyama, Akimasa Ishikawa (KEK)

Kazuhiko Hara, Shikie Iwanami, Hitoshi Murayama (Univ. Tsukuba)

Ayaki Takeda (Miyazaki Univ.)

June 12th, 2020 SOIPIX for the EIC at BNL

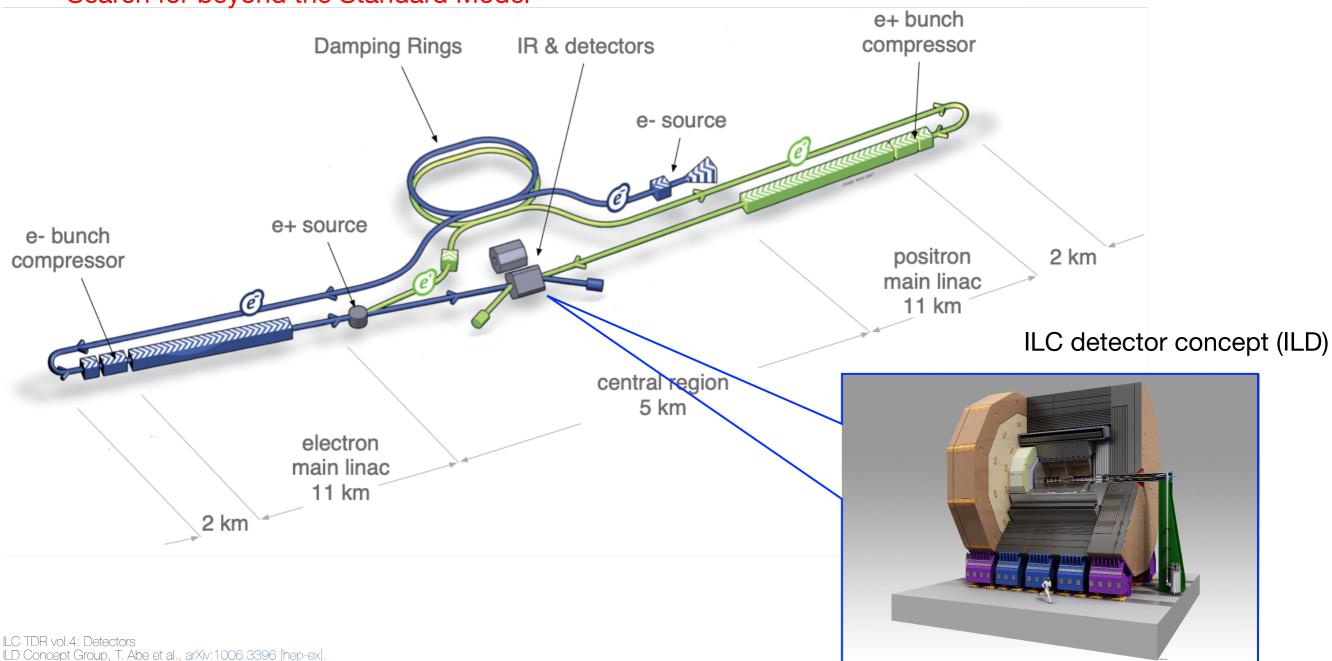

# ILC Experiment

### **ILC Experiment**

- e+e- linear collider

- Center of mass energy: 250 500 GeV (extendable to 1 TeV)

- Precise measurement of the Higgs boson

- Search for beyond the Standard Model

2020/06/12

### ILC Vertex detector

### **Requirements:**

1) Single point resolution: better than 3 μm

Pixel size:  $\sim$ 20  $\times$  20  $\mu$ m<sup>2</sup>

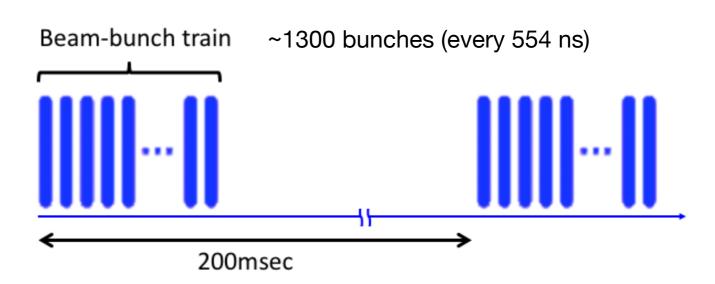

- 2) Time resolution: single-crossing (554 ns interval) time resolution

- 3) Detector occupancy: < 2 %

- 4) Low material budget: X ≤ 0.1 0.2 % X<sub>0</sub> / Layer corresponds to ~ 100 - 200 μm Si, (supports, cables and cooling add further material) low-power ASICs (~ 50 mW/cm²) + gas-flow cooling

- 5) Radiation hardness:

TID : < 1 kGy / year

NIEL:  $< 10^{11}$  1MeV  $n_{eq}$  /  $cm^2$  / year

We are designing and evaluating prototype pixel sensor with SOI technology to fulfill the requirements.

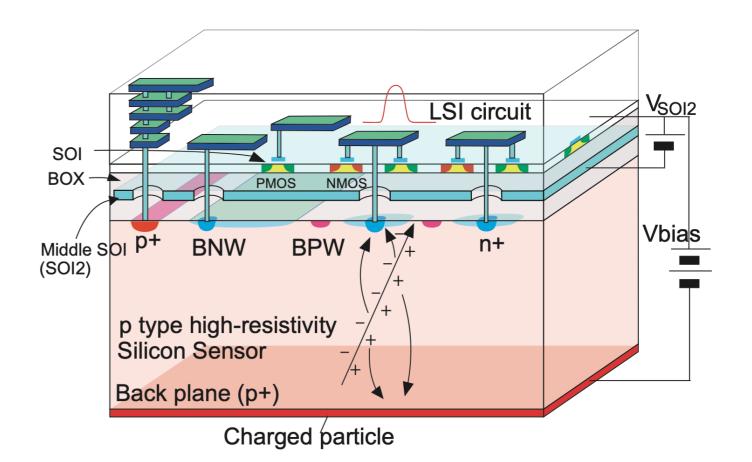

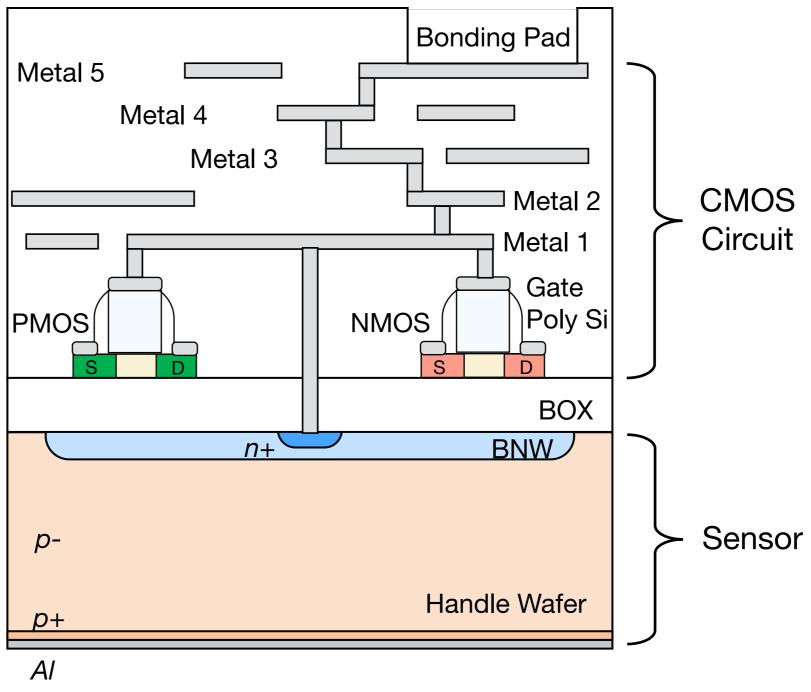

### SOI Pixel Detector

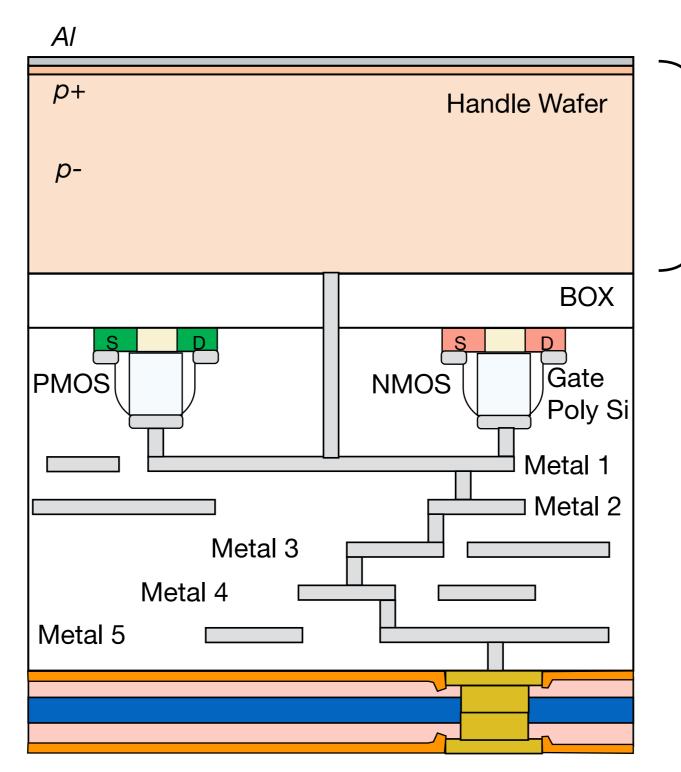

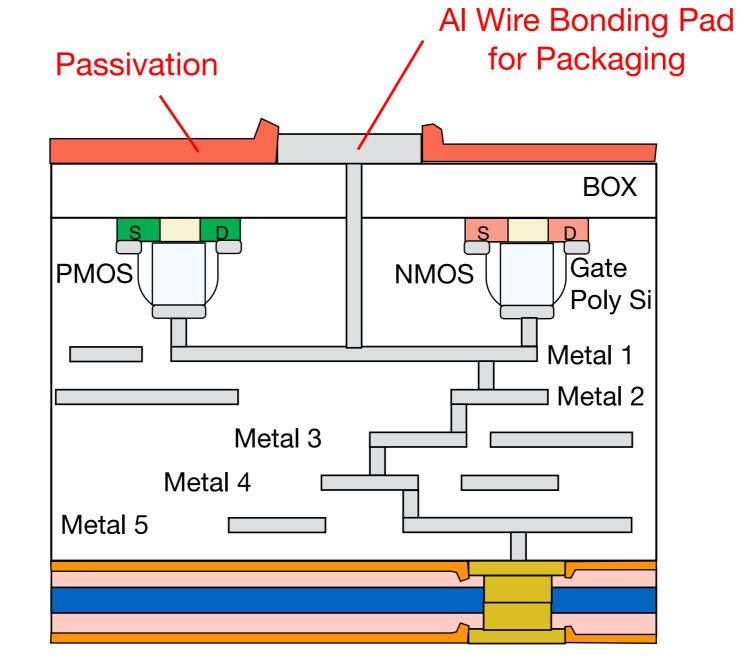

### **SOI: Silicon-on-Insulator technology**

Utilize 0.2  $\mu$ m FD-SOI CMOS process by Lapis Semiconductor Co. Ltd. (Japan)

### **SOI Pixel Detector: Monolithic type detector**

- LSI is processed on Buried Oxide layer (BOX)

- Smaller pixel size, complex circuit in pixel

- Low material budget

- High speed, low power

- Less single event effects (SEE) probability

- Low cost

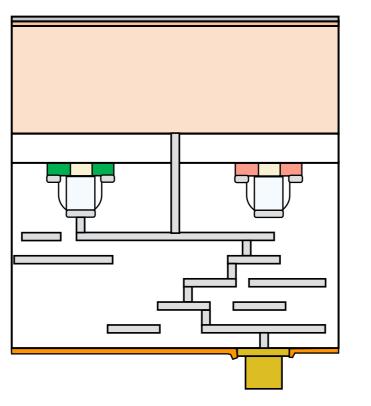

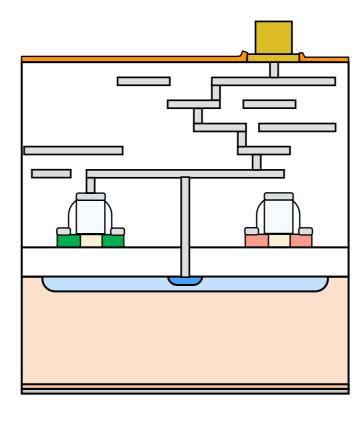

#### **Double SOI Pixel Detector**

Middle Si layer suppresses

- Back gate effect

- Sensor-Circuit cross talk

Middle Si layer shields coupling between sensor and circuit.

It is useful for analog and digital mixed circuit in pixel.

Radiation damage (TID)

It is able to compensate electric field generated by trapped holes in the BOX.

It can be used in high radiation environment (~1MGy).

(K. Hara, Vertex2017, Sep. 11-15, 2017, Las Caldas)

Sensor thickness:  $50 - 500 \,\mu\text{m}$ Sensor Resistivity:  $> 1 \, \text{k}\Omega \cdot \text{cm}$ SOI2 thickness:  $150 \,\mu\text{m}$  (n-type) SOI2 Resistivity:  $< 10 \,\Omega \cdot \text{cm}$

### Functions for ILC Vertex Detector

### **Necessary functions for the ILC vertex detector:**

Single point resolution

Pixel size: less than 20  $\mu$ m

Calculate weighted center of charges (Charges are spread over multi pixels).

- → Record analog signal of hit pixels.

- Timing resolution

Bunch crossing occurs every 554 ns in 1-msec-long bunch train with an interval 200 ms. Identify the collision bunch of hits to reconstruct an event.

- → Record timestamp of hit pixels.

- Detector occupancy

Hit information has to be held during 1 beam-bunch train.

Increase pixel occupancy.

- → Need multiple memories

- High speed data transfer

Data have to be sent to backend before next bunch train injection.

- → Reduce the data to transfer.

We designed a prototype pixel detector SOFIST.

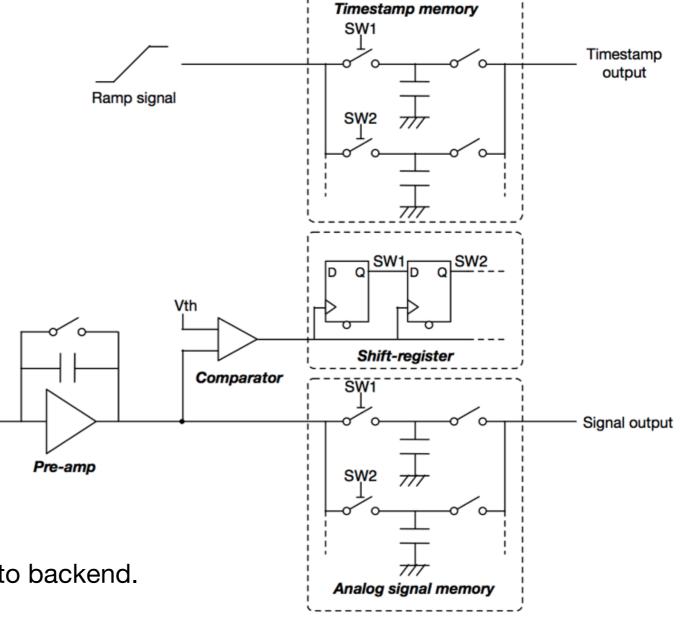

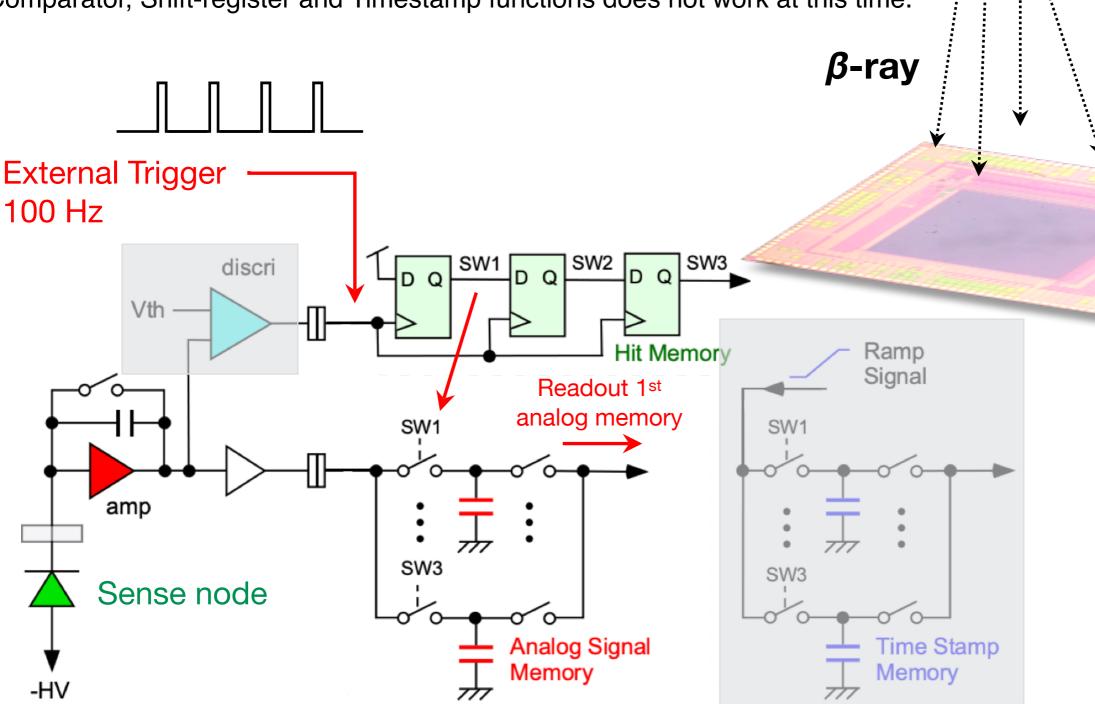

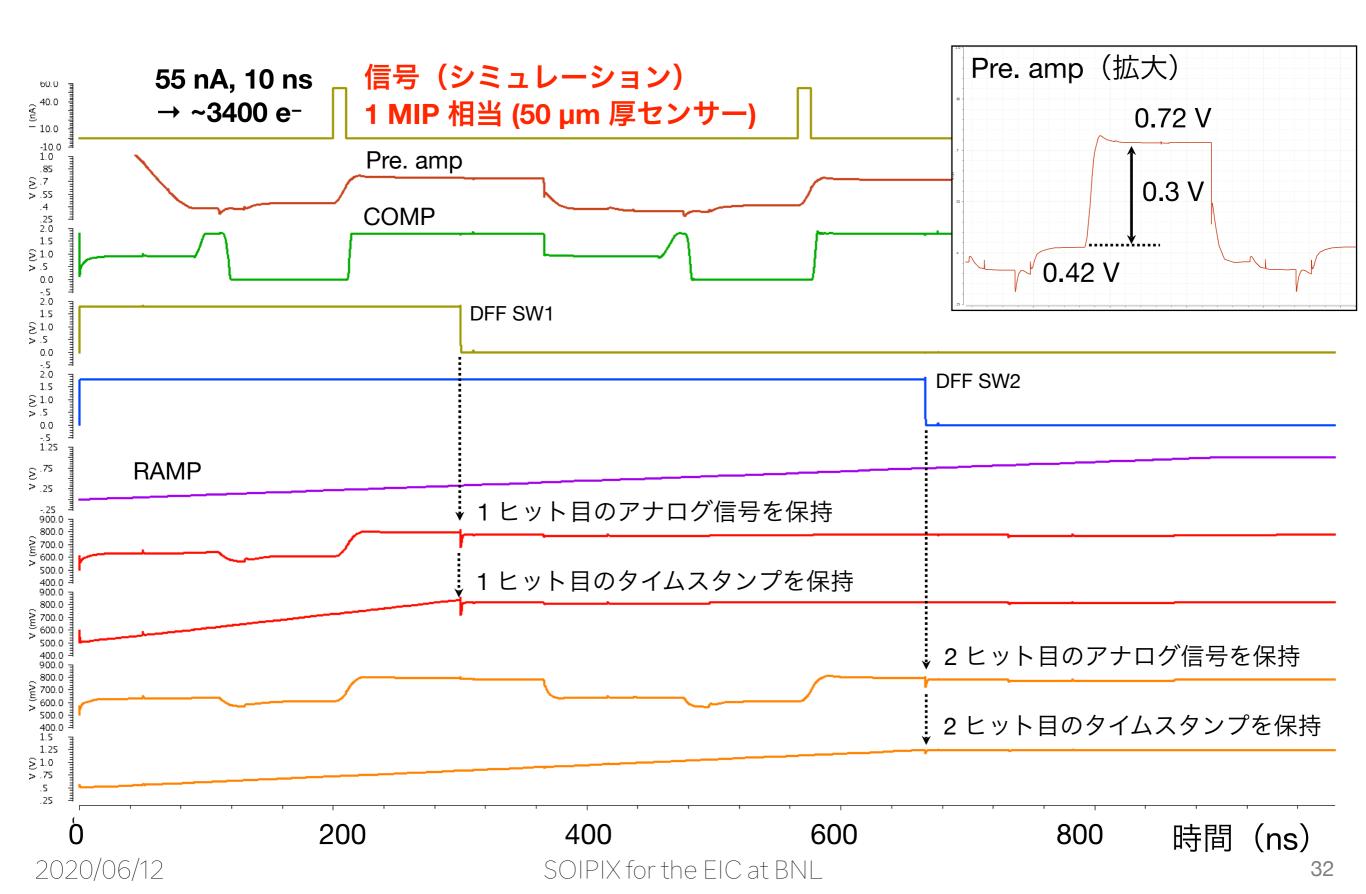

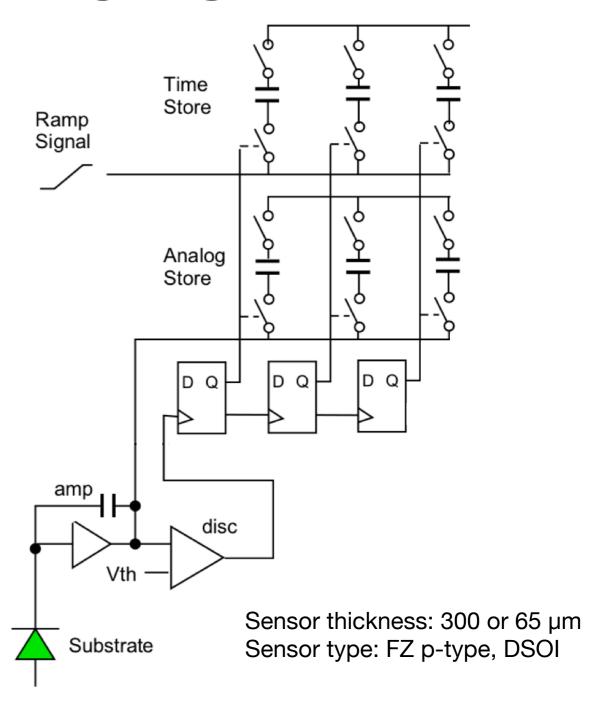

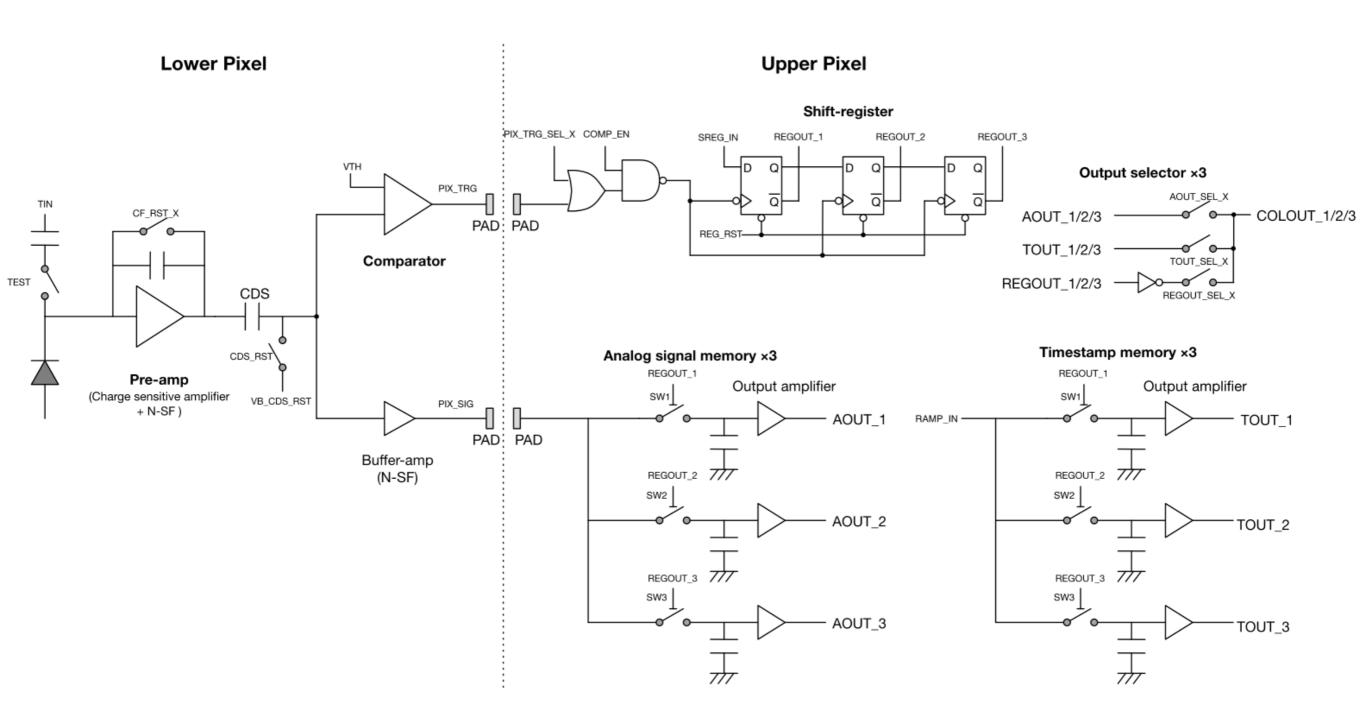

### Architecture of SOFIST

### In a Pixel

- Pre-amplifier

- Comparator

Keep the analog s

Keep the analog signal and time stamp if a signal exceeds a threshold  $V_{th}$ .

- Shift register

- Hit memory

Latch for multiple memories.

Analog signal memory

Store signal charges for three (or more) hits.

Time stamp circuit

Store time stamps for three (or more) hits.

### On Chip

- Column ADC

- Digitize analog signal and time stamp.

- Zero-Suppression logic

Extract hit pixels and reduce the data to transfer to backend.

SOFIST1 SOFIST2 SOFIST3 SOFIST4 (3D)

Beam test at FNAL in Jan. 2017 Analog signal Beam test at FNAL in Feb. 2018

Analog signal or Timestamp

Beam test at FNAL in Feb. 2019

Analog signal and Timestamp

Beam test at FNAL in Feb. 2020 Analog signal

| Chip Size (mm²)                     | $2.9 \times 2.9$                                      | 4.45 × 4.45                                                                                                                             | 6 × 6                                                                                                                                | 4.45 × 4.45                                                                                                                          |

|-------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Pixel Size ( $\mu$ m <sup>2</sup> ) | 20 × 20                                               | 25 × 25                                                                                                                                 | 30 × 30                                                                                                                              | 20 × 20                                                                                                                              |

| Pixel Array                         | 50 × 50 (Analog Signal)                               | $64 \times 64$ (Time Stamp)<br>$16 \times 64$ (Analog Signal)                                                                           | $128 \times 128$ (Analog signal and Time stamp)                                                                                      | $104 \times 104$ (Analog signal and Time stamp)                                                                                      |

| Functions (Pixel)                   | Pre. Amplifier (CSA)<br>Analog signal memory (2 hits) | Pre. Amplifier (CSA) Comparator (Chopper inverter) Shift register (DFF × 2) Analog signal memory (2 hits) or Time stamp memory (2 hits) | Pre. Amplifier (CSA) Comparator (Chopper inverter) Shift register (DFF × 3) Analog signal memory (3 hits) Time stamp memory (3 hits) | Pre. Amplifier (CSA) Comparator (Chopper inverter) Shift register (DFF × 3) Analog signal memory (3 hits) Time stamp memory (3 hits) |

| Functions (On Chip)                 | Column ADC (8 bit)                                    | Column ADC (8 bit)<br>Zero-suppression logic                                                                                            | Column ADC (8 bit)                                                                                                                   | Column ADC (8 bit)                                                                                                                   |

| Wafer                               | FZ n-type (Single SOI)                                | Cz p -type (Double SOI)                                                                                                                 | FZ p -type (Double SOI)                                                                                                              | FZ p -type (Double SOI)                                                                                                              |

| Wafer Resistivity (kΩ·cm)           | 2 ≤                                                   | 1 ≤                                                                                                                                     | 3 - 10                                                                                                                               | 3 - 10                                                                                                                               |

| Status                              | Delivered (Dec. 2015)<br>Position resolution ~1.4 µm  | Delivered (Jan. 2017)<br>Time resolution ~1.55 µs                                                                                       | Delivered (May. 2018)<br>Under evaluation                                                                                            | Delivered (Jan. 2019 ~)                                                                                                              |

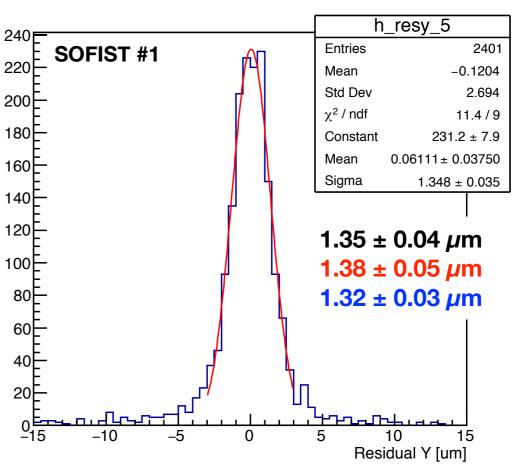

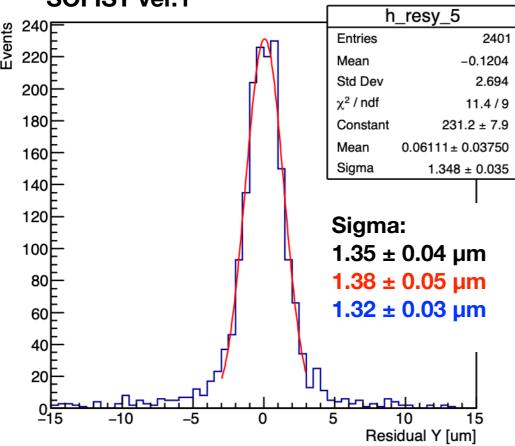

### Hit position reconstruction

Calculate weighted center of charges ( $6 \times 6$  pixels).

#### **Track reconstruction**

Find track candidates by four layers of FPIX. The track that has the minimum chi2 is chosen for calculating the residual.

#### Residual

Difference between reconstructed track and actual hit on the SOFIST.

#### **Residual X** h resx 5 2401 **Entries** SOFIST #1 0.1677 Mean Std Dev 2.721 200 $\chi^2$ / ndf 12.58 / 9 180 $227.7 \pm 7.6$ Constant $0.1668 \pm 0.0386$ Mean 160 Sigma $1.367 \pm 0.035$ 140 120F $1.37 \pm 0.04 \, \mu \text{m}$ 100F $1.49 \pm 0.06 \, \mu \text{m}$ 80 $1.33 \pm 0.03 \, \mu \text{m}$ 60l 40 20 Residual X [um]

### Readout and Sensor depletion layer

12-bit external ADC, 500 μm (Full depletion) 8-bit on-chip ADC, 500 μm (Full depletion) 12-bit external ADC, 200 μm (Partial depletion)

Sensor Thickness: 500 µm

#### **Alignment**

Tracking by telescope (INTPIX4) is not performed. Roughly aligned among SOFIST by hit position correlation.

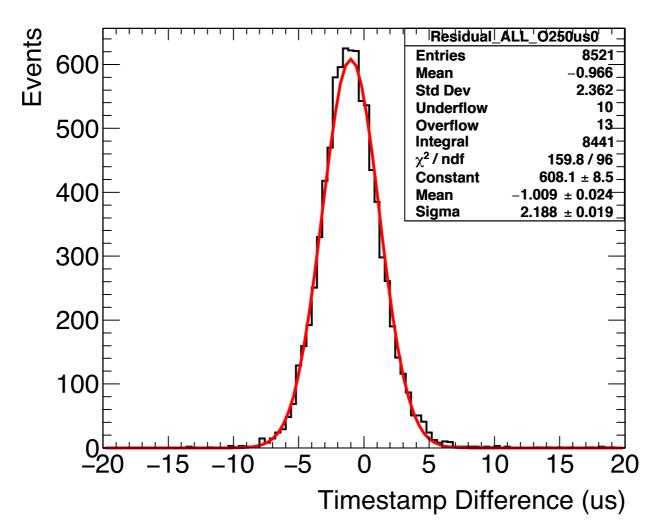

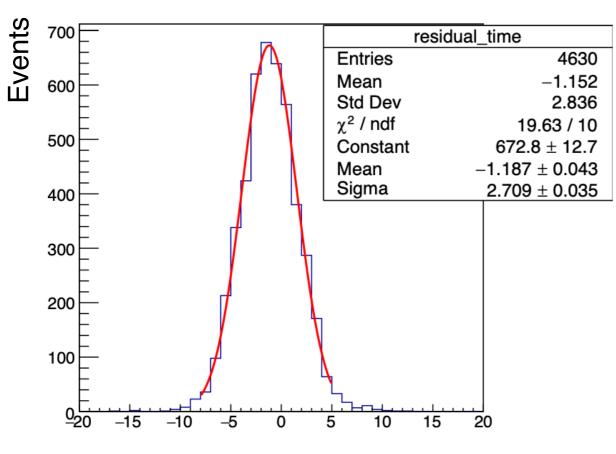

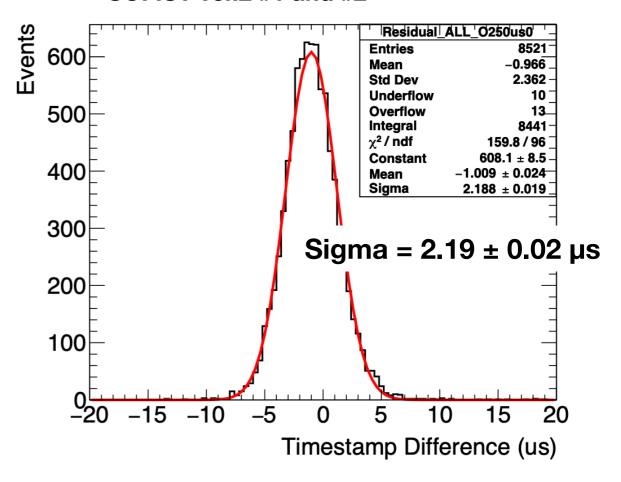

### **Timestamp residual**

Timestamp difference between #1 and #2. (Hit position of #2 is within 2 pixels of #1.)

### Sensor Thickness: 65 µm

Intrinsic resolution:  $2.19/\sqrt{2} \sim 1.55 \mu s$

H. Murayama, Univ. Tsukuba

10

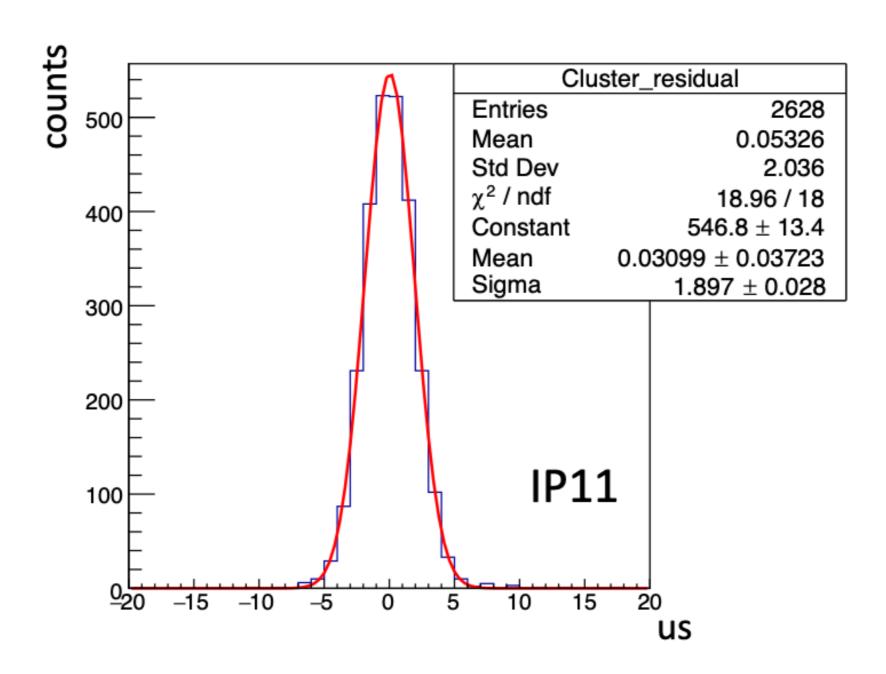

### **Timestamp residual**

Timestamp difference between #1 and #4.

Time difference (µs)

Intrinsic resolution:  $2.71/\sqrt{2} \sim 1.92 \,\mu s$

Sensor Thickness: 300 µm

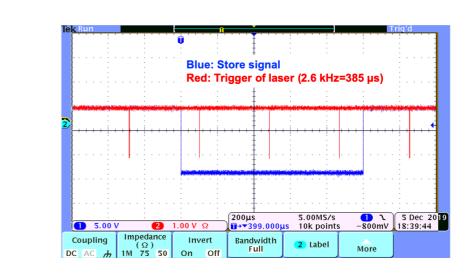

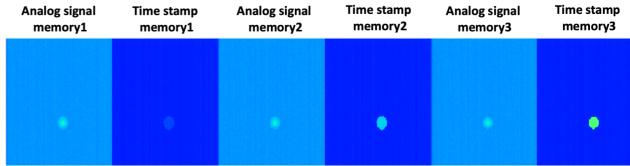

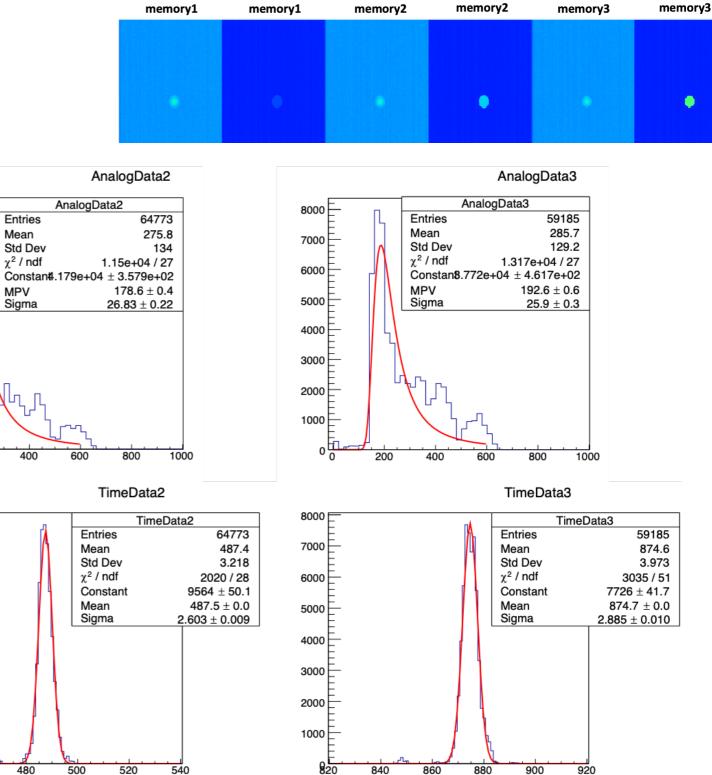

#### **Multi-memory readout test**

SOFIST3 has three hit, analog signal and timestamp memories. Multi-memory readout scheme was tested by injecting a IR laser three times in a 1 ms period.

### **Analog signal**

Represent stable laser pulses (~180 ADC).

### **Timestamp**

Show different timing of the laser injection (110, 490, 880 ADC).

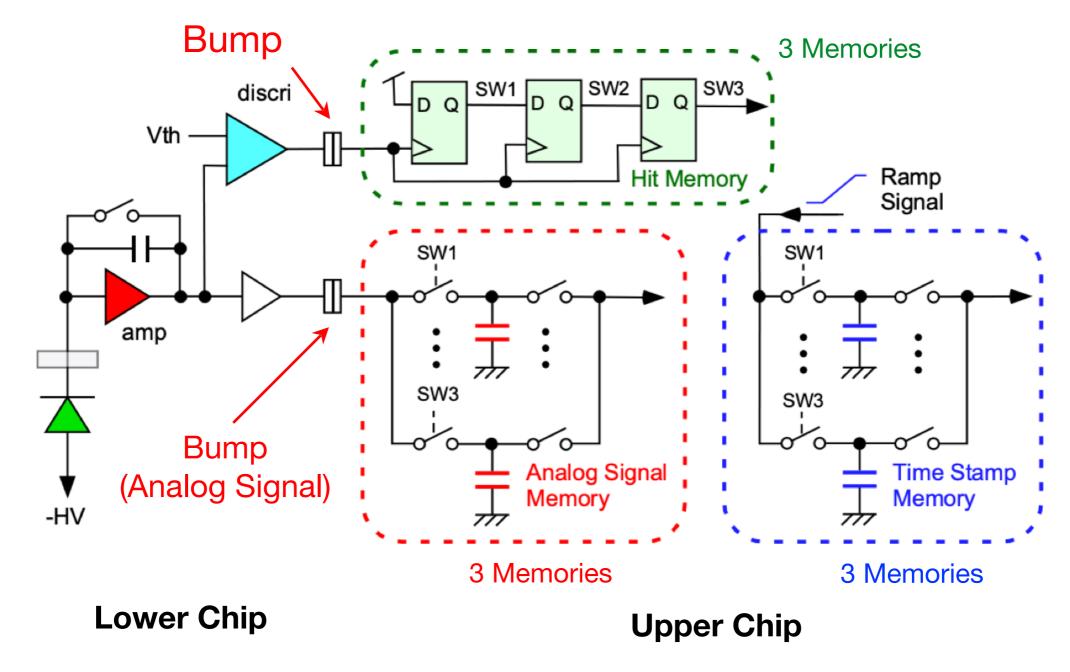

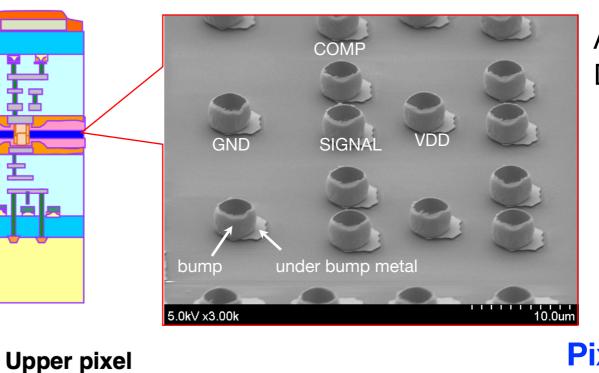

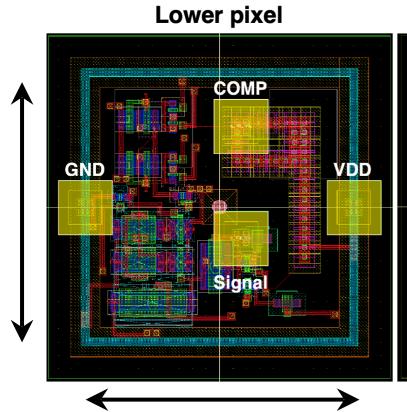

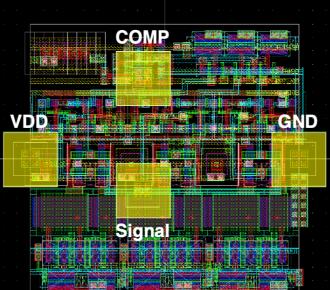

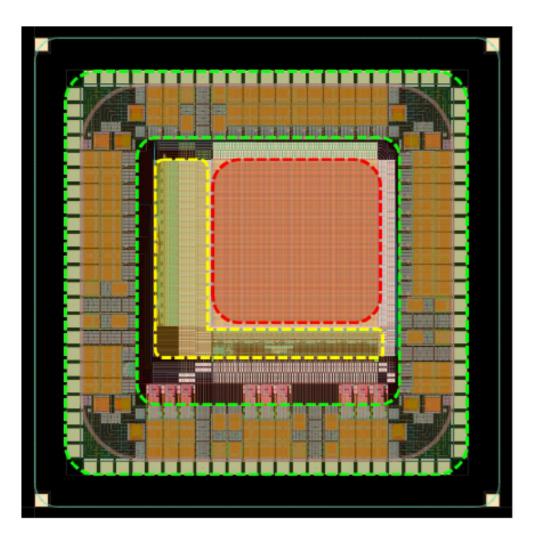

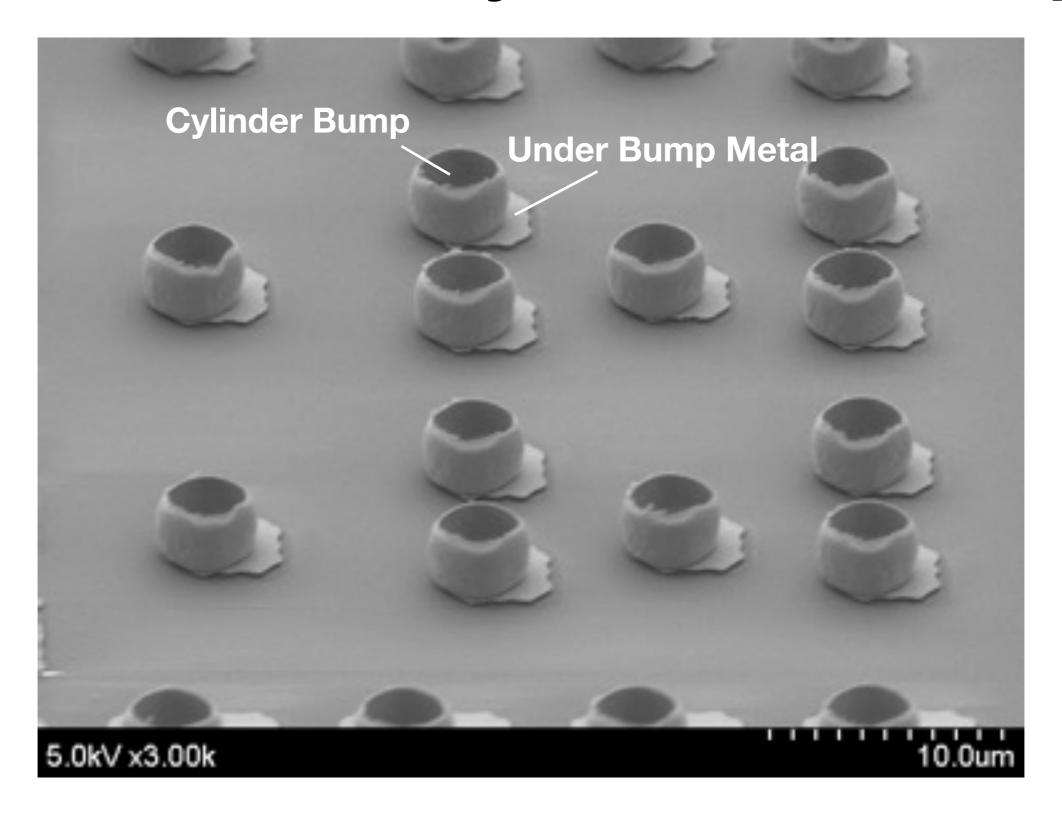

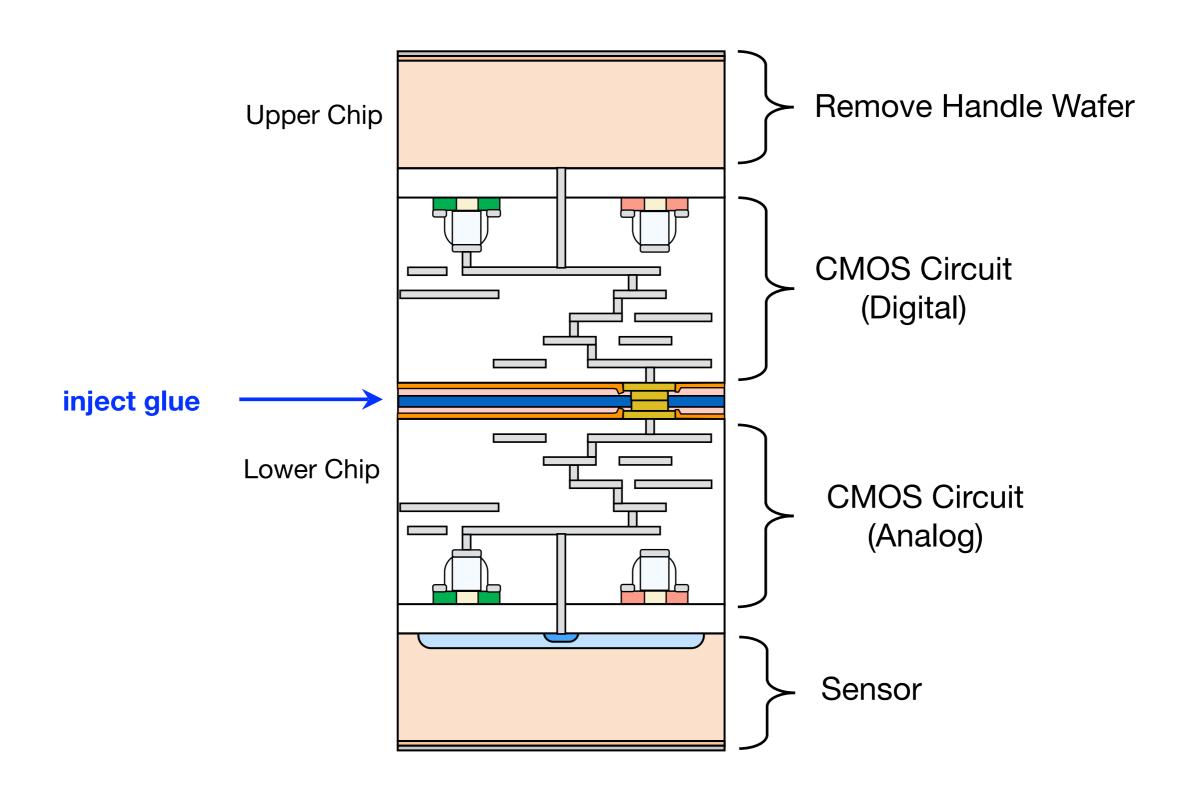

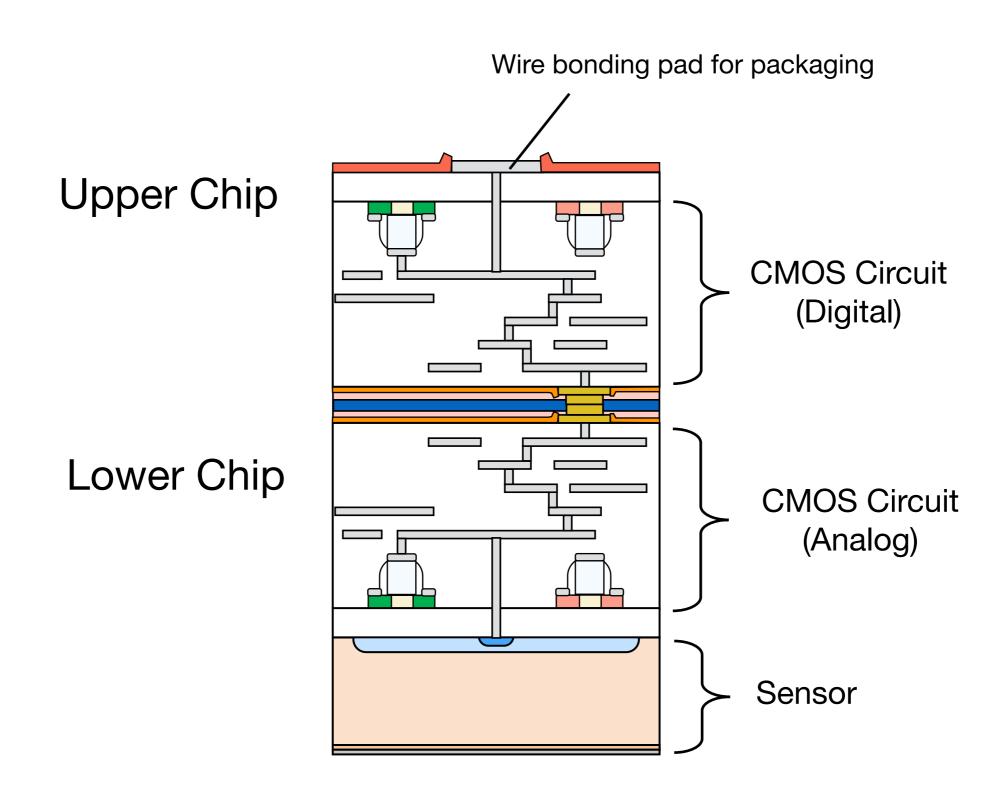

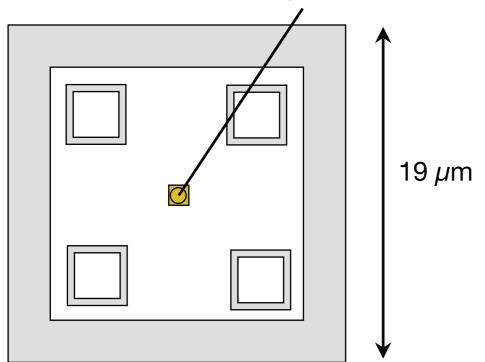

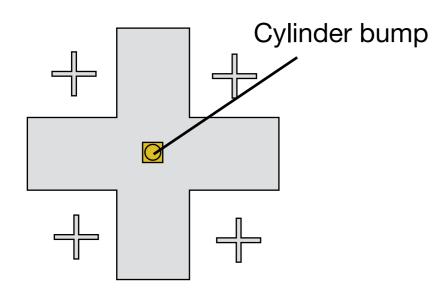

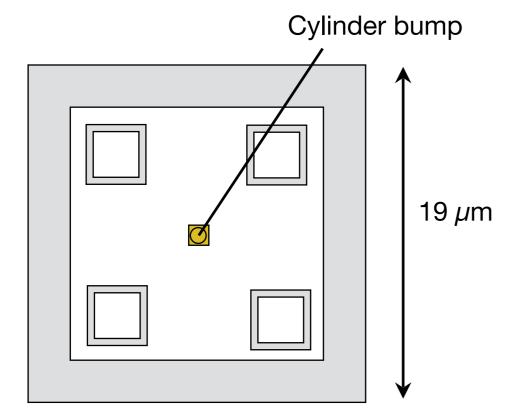

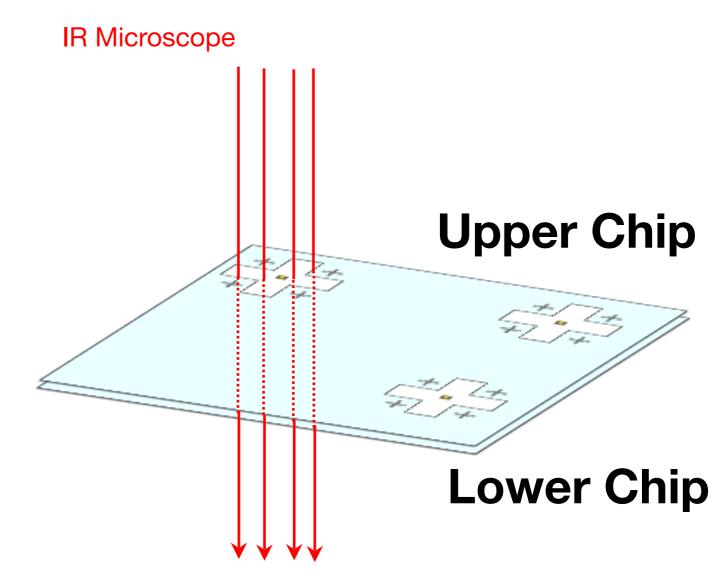

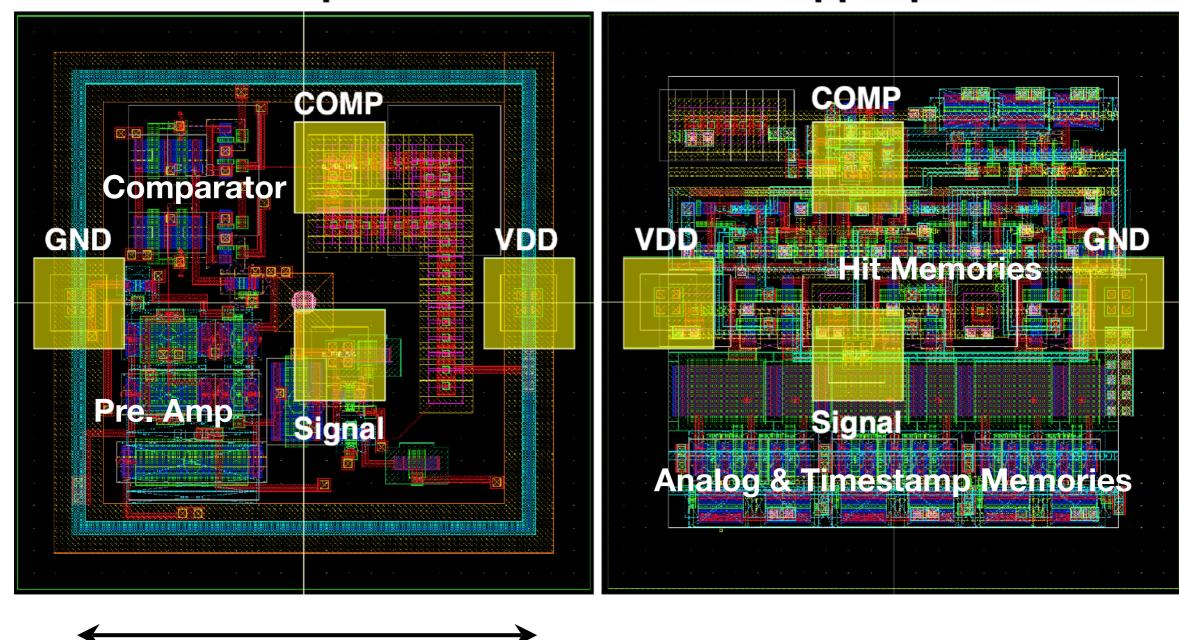

### SOFIST4 Pixel

SOFIST4 pixel has all necessary functions in a pixel.

Pre. amplifier and comparator are implemented in lower pixel.

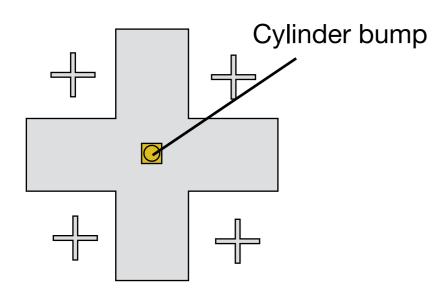

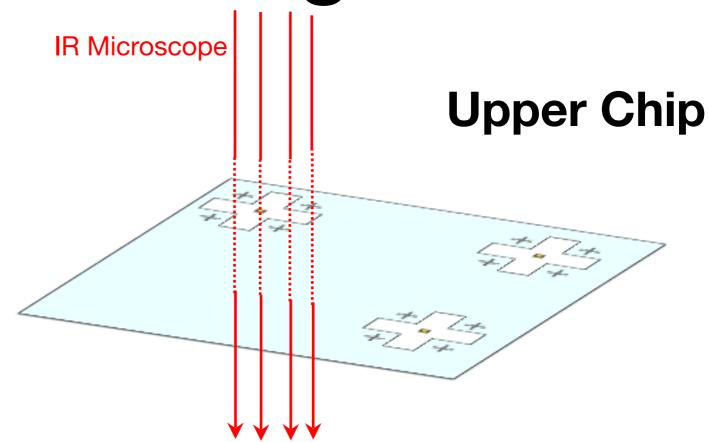

Memories (hit, analog signal and timestamp for three hits) are implemented upper pixel. Lower and upper pixels are connected by Au cylinder micro bump (Tohoku-MicroTec Co., Ltd.)

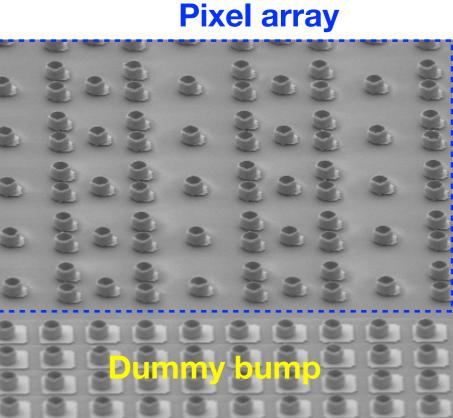

# Bumps for Pixel

Au cylinder bump Diameter: 3μmφ

5.0kV x1.00k

30.0um

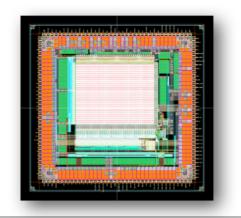

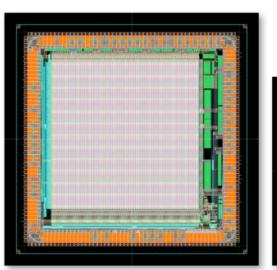

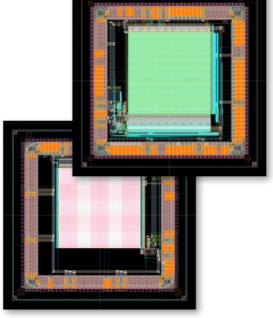

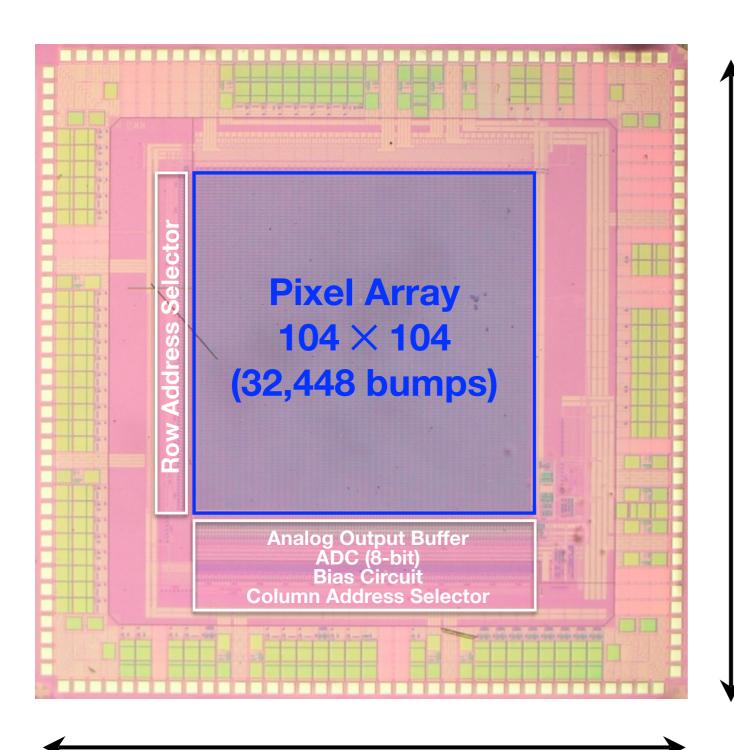

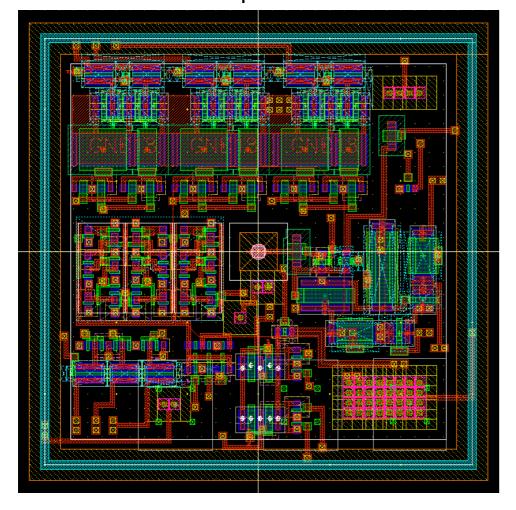

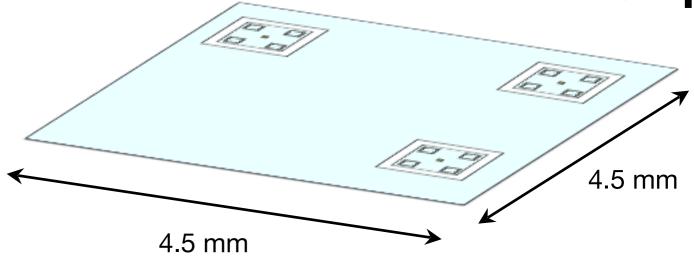

# SOFIST4 Chip

**Design:**

Chip size:  $4.45 \times 4.45 \text{ mm}^2$

Pixel size:  $20 \times 20 \ \mu m^2$

Active area:  $2.08 \times 2.08 \text{ mm}^2$

Sensor type: Double SOI, FZ *p*-type

Sensor thickness: 300 µm

Sensor resistivity:  $3 - 10 \text{ k}\Omega$  · cm

**Memory:** Analog 3 hits

**Timestamp 3 hits**

Hit 3 hits

**On-Chip: 8-bit Column ADC**

Total bumps: 32,448 for pixel array

3,520 for I/O cell

$4.45 \times 4.45 \text{ mm}^2$

# B-ray tracks

\*The sensors we have evaluated were single-SOI FZ-n type sensor due to the process issue of the 3D integration by T-Micro.

→Comparator, Shift-register and Timestamp functions does not work at this time.

90**S**r

# B-ray tracks

\* Movie

T. Tsuboyama, KEK

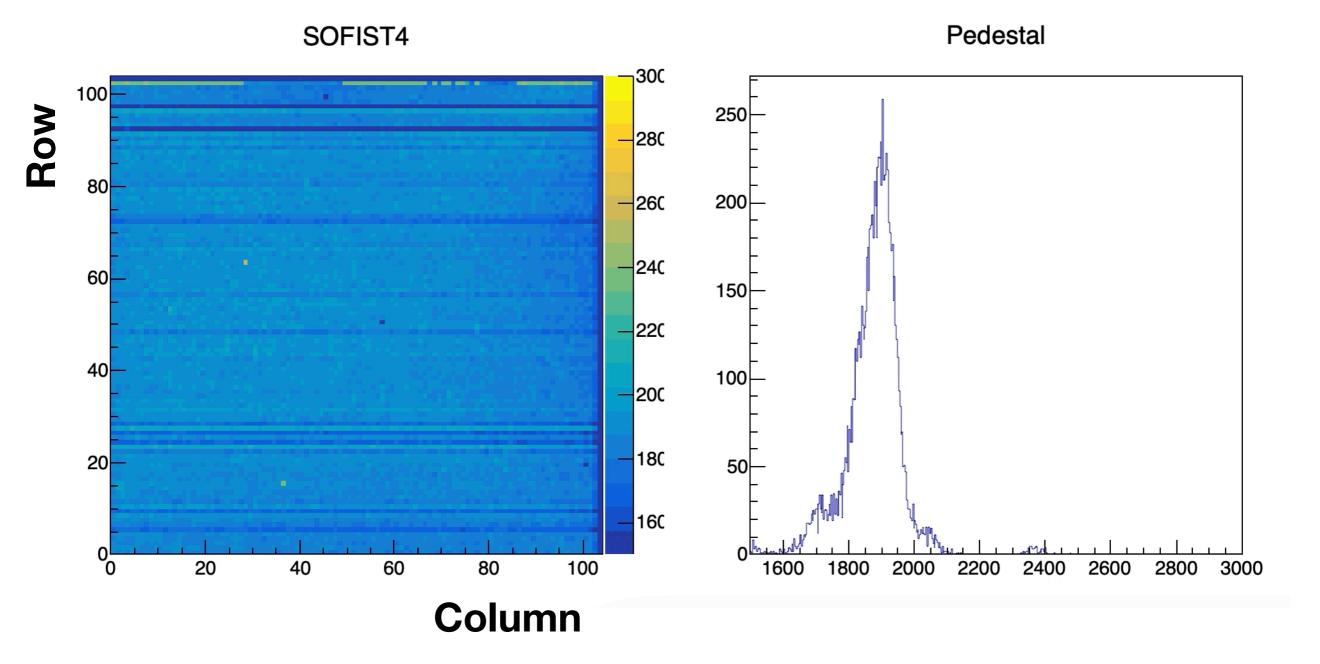

# Bump Connection Yield

\* Movie

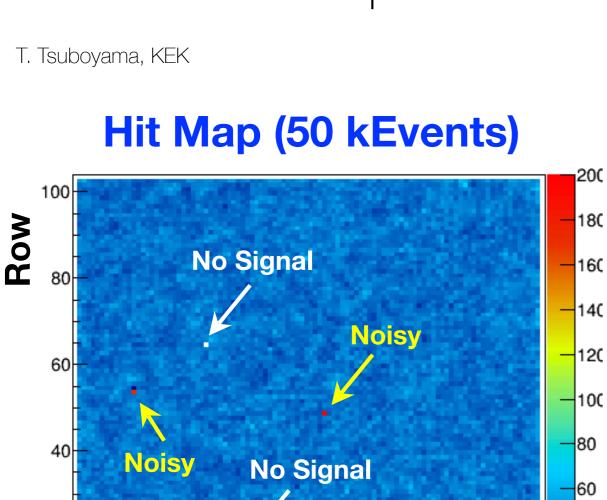

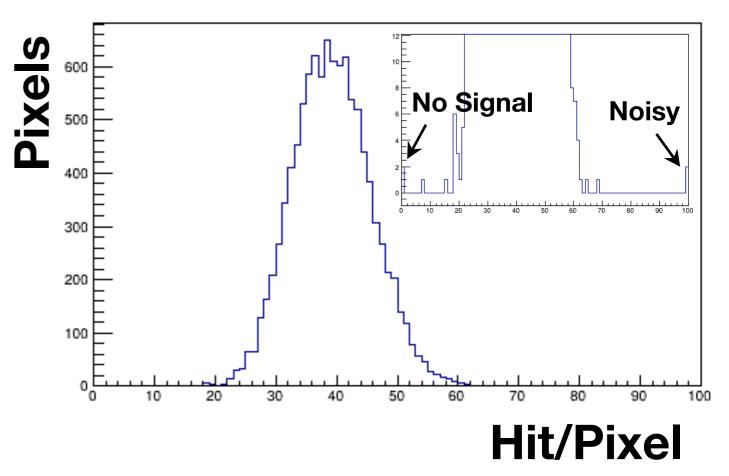

### **Hit Map**

T. Tsuboyama, KEK

# Bump Connection Yield

20

40

60

80

Connection Yield: (102 × 102 - 2) / 102 × 102 ~ 99.98 %

Reject the outermost pixels for the calculation.

40

20

100

Column

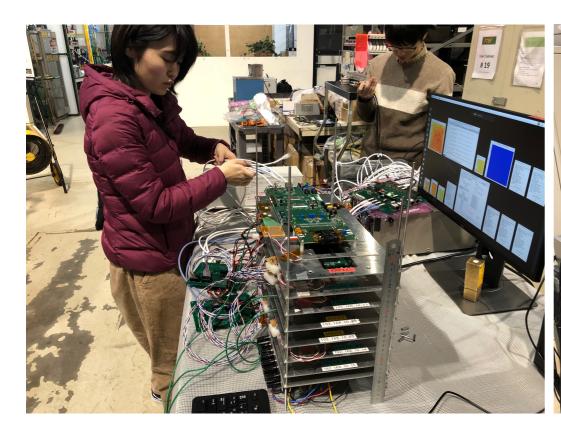

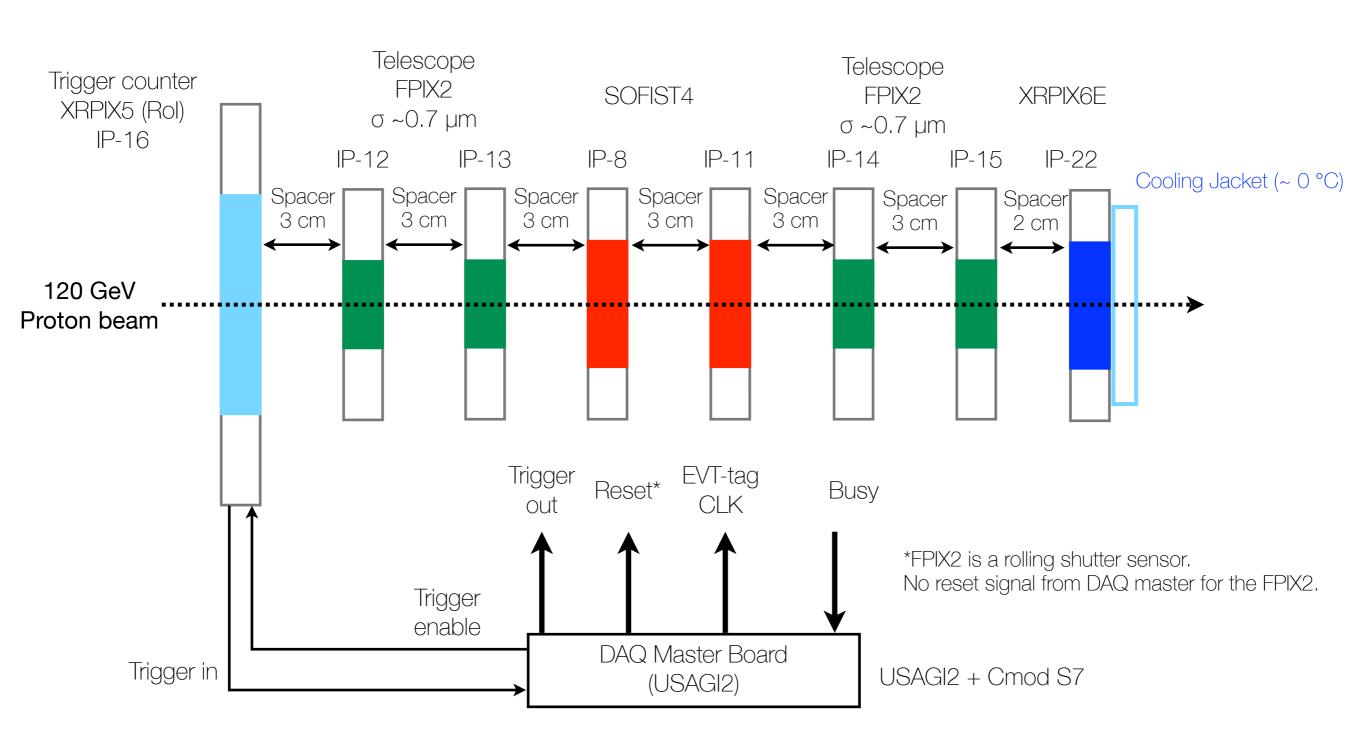

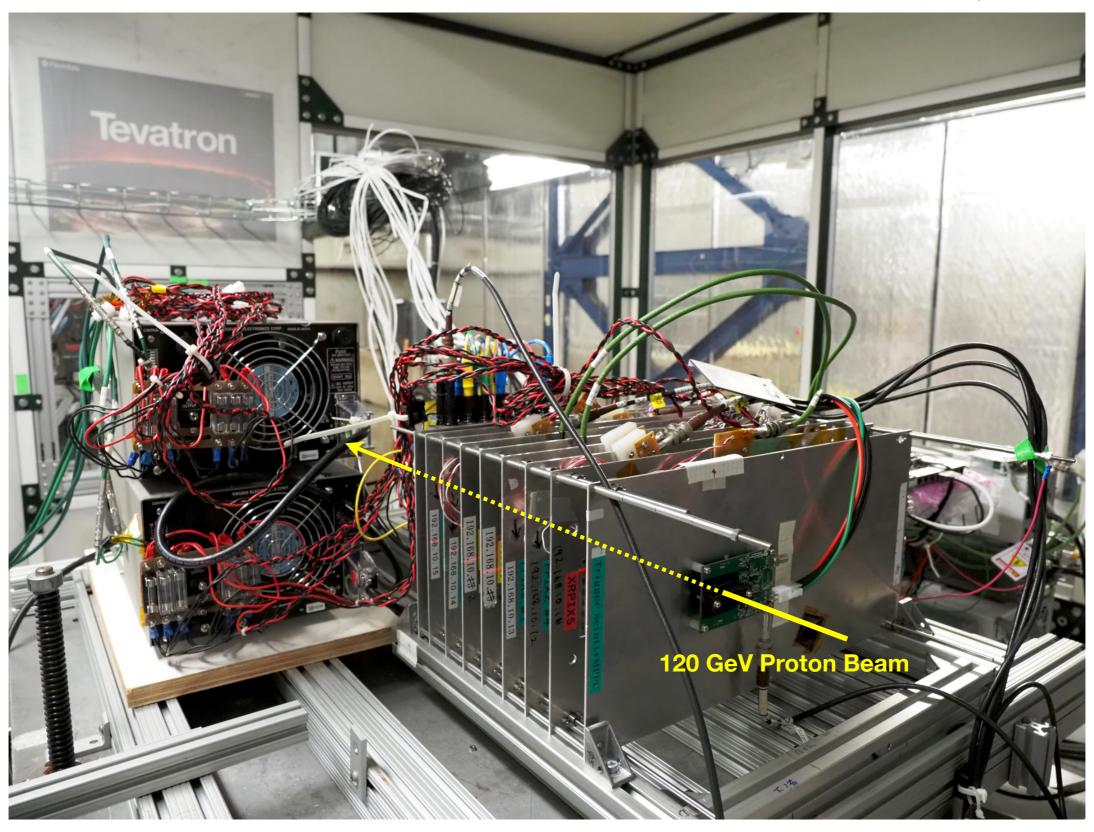

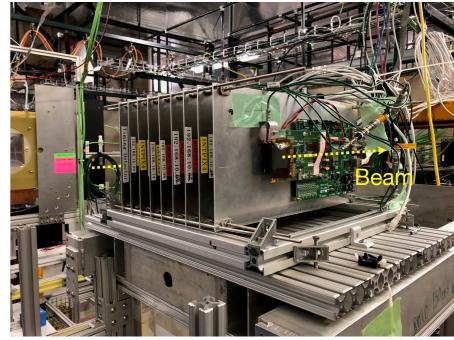

### Beam Test 2020 @ FTBF

Fermilab Beam Test Facility

Beam time: Feb. 26th - Mar. 8th, 2020

120 GeV proton beam

### Members

TMCIT, KEK, Univ. Tsukuba and Miyazaki Univ. (Japan)

Sensors (All SOIPIX)

SOFIST4 and XRPIX6E (DUT)

FPIX2 (Telescope)

XRPIX5 (Trigger)

# Setup

Telescope + Trigger counter + DUT

# DAQ Master (USAGI2)

# Setup

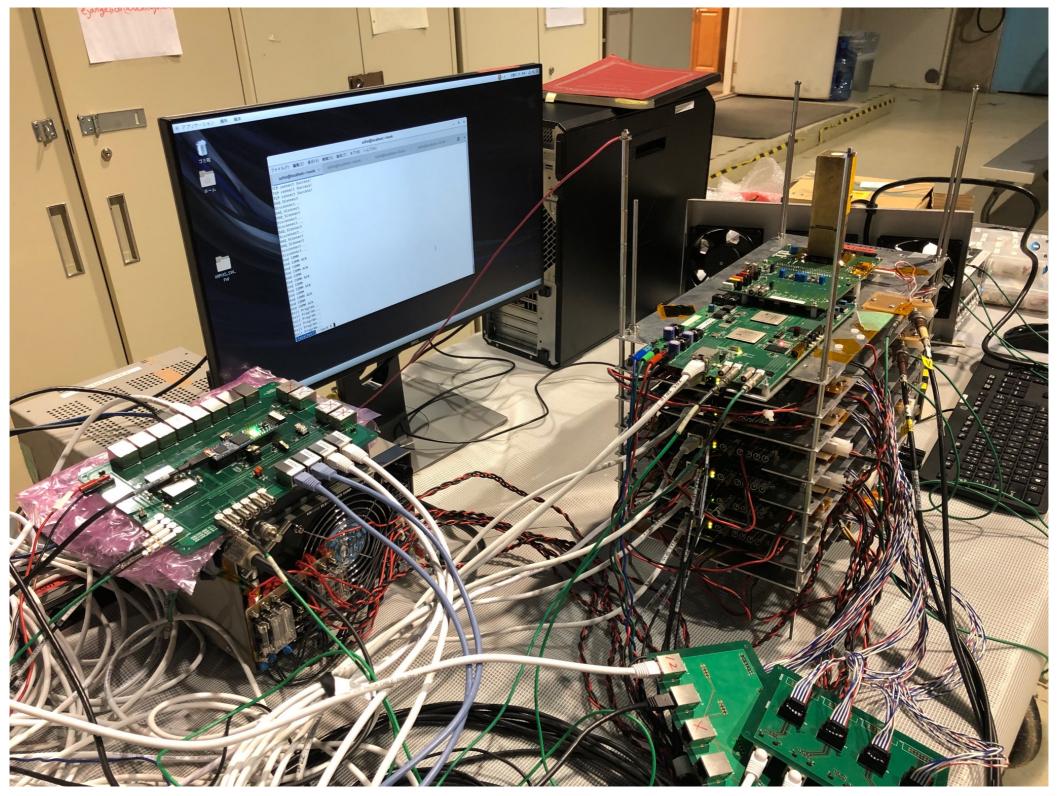

Checking the DAQ system by beta source

21

# Setup

Setup at the beam line

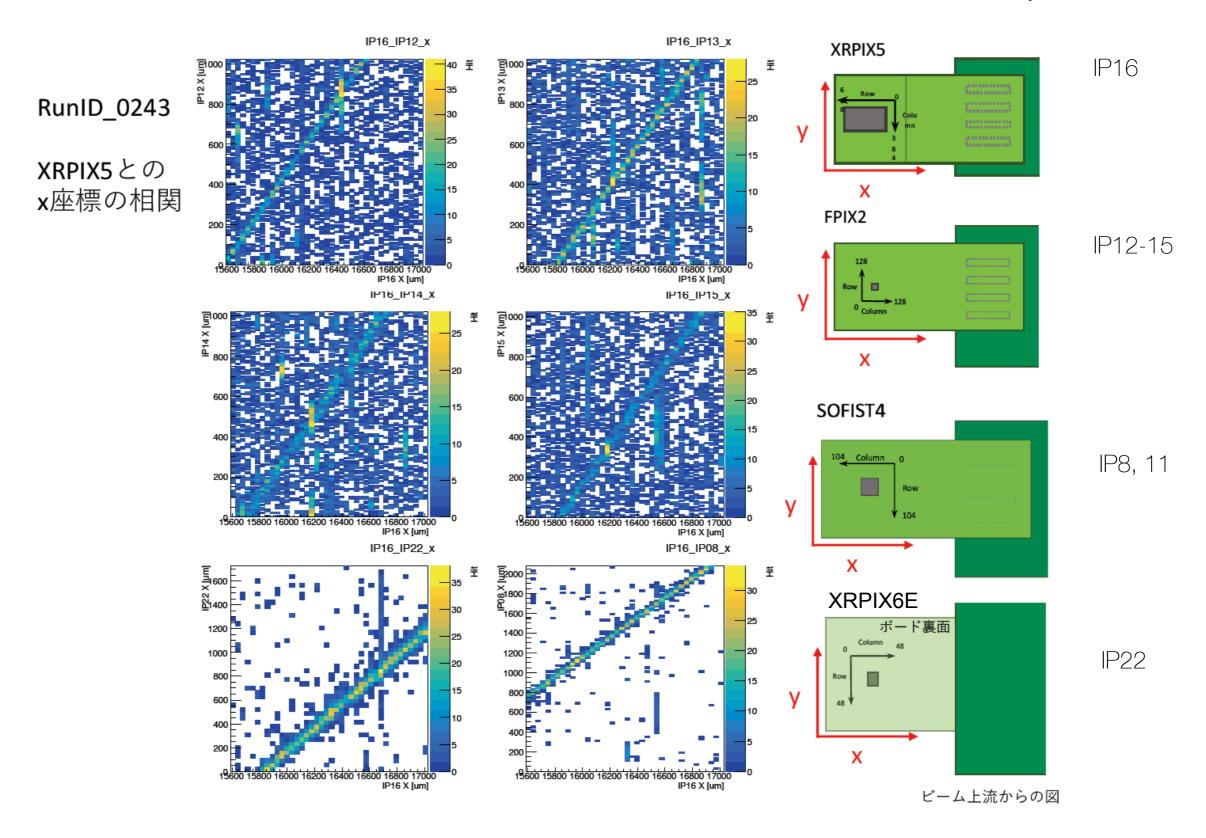

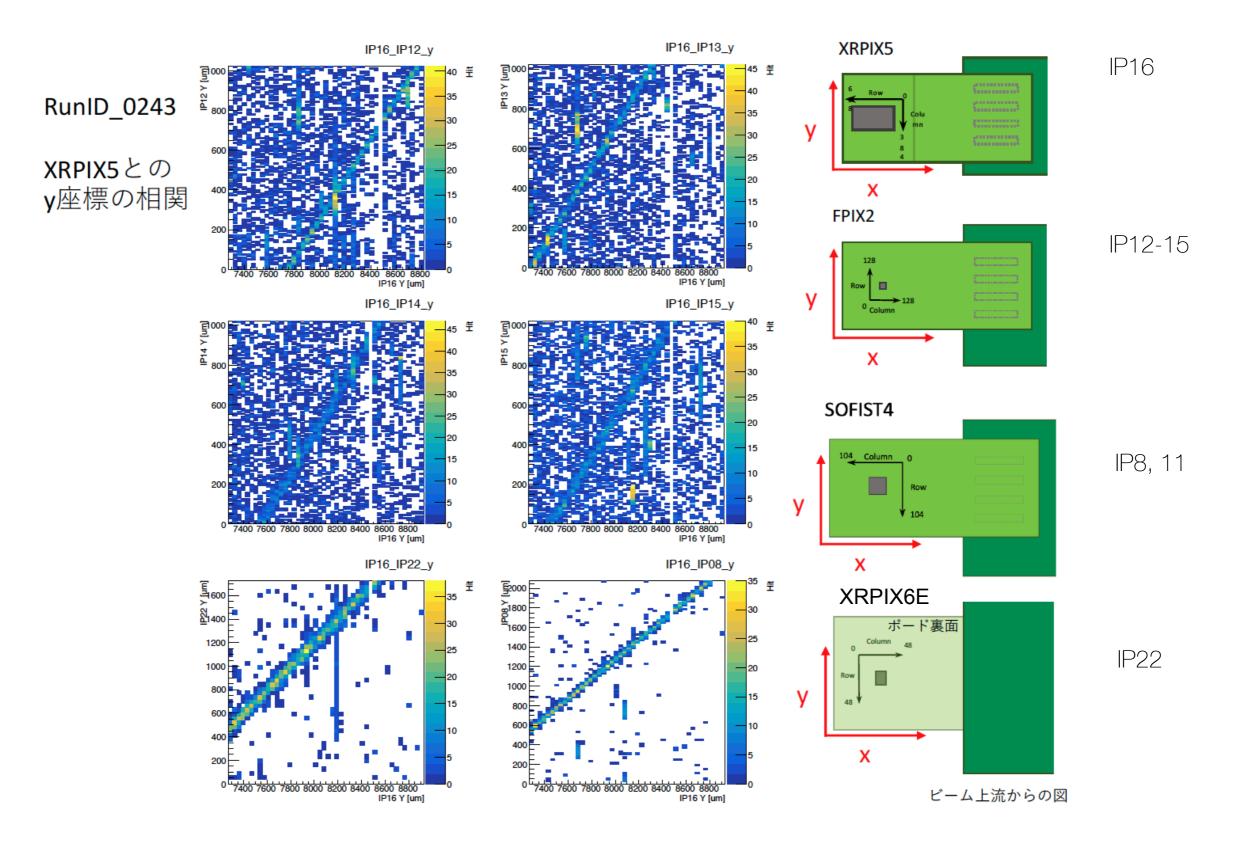

# Hit Correlation

H. Murayama, Univ. Tsukuba

# Hit Correlation

H. Murayama, Univ. Tsukuba

# Summary

Monolithic type pixel detector has been developed with SOI technology for the ILC vertex detector.

We have already demonstrated 1.4  $\mu$ m of spatial resolution and 1.55  $\mu$ s of time resolution by the prototype, SOFIST1 and 2.

SOFIST4 is 3D integrated SOI pixel detector

$\rightarrow$  Three kinds of multiple memories, Hit, Position, and Timestamp are implemented in 20  $\times$  20  $\mu$ m<sup>2</sup>.

Demonstrated the images of the  $\beta$ -ray tracks of  ${}^{90}Sr$  with a bump connection yield of 99.9%.

Data analysis of the beam test in 2020 is still working in progress.

We are planning to reprocess SOFIST4 to evaluate the full function. Additionally, we'd like to try to integrate thinned SOFIST4 sensor (~65 µm thickness).

# Backup

chip size

pixel size

# of pixels

active region

parallel readout

readout scheme

$2.9~\mathrm{mm} \times 2.9~\mathrm{mm}$

$8 \, \mu \text{m} \times 8 \, \mu \text{m}$

$128 \times 128$

$1024 \ \mu m \times 1024 \ \mu m$

$8 (128 \times 16 \text{ pixels / readout})$

rolling shutter

Sensor: Single SOI, FZ-p, ~25 k $\Omega$  · cm, 500  $\mu$ m thick

### Position resolution $\sim 0.7 \, \mu \text{m}$

tested at FTBF in 2017

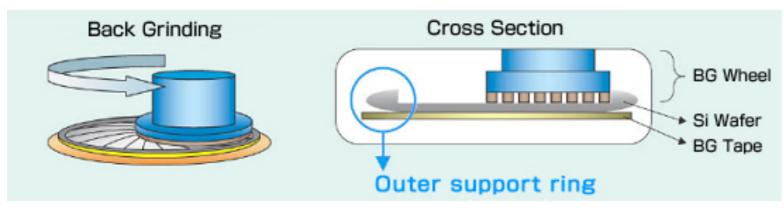

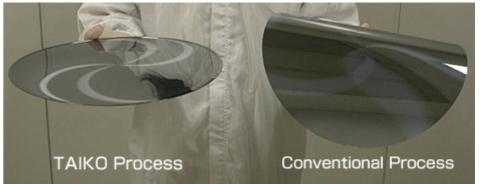

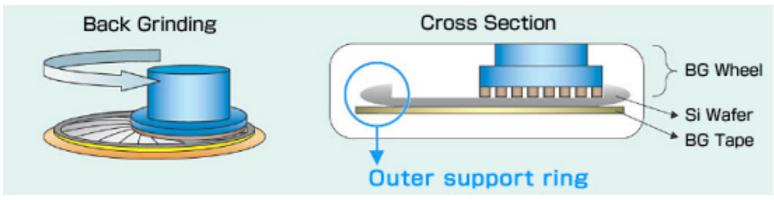

# Wafer Thinning

### **TAIKO Process by DISCO Corporation (Japan)**

#### Stress relief with wet etching by Mimasu Semiconductor Industry Co., Ltd. (Japan) HF+HNO<sub>3</sub> Exhaust gas **BG** Tape No Dry Etching Si Wafer Dry Etching Wet Etching **Back Grinding Tape Back Grinding Tape TAIKO Grinding** Laminating Stress Relief Peeling ~75 µm ~100 µm Discrete devices 3D Devices Via Hole Drilling Ion Implantation Electrode Filling Annealing **Back Side Metalizing** Interconnecting Bumping Wafer Testing · · · etc

Wafer Mounting

BG Tape Si Wafer

Ring Grinding

#### **TAIKO Process**

with outer support ring

- Lower wafer warpage

- Improve of wafer strength

- Easy wafer handling

- Easy backside processing (ion implantation, annealing, Metalizing etc) after thinning

### Back side process after thinning

- Boron implantation (ULVAC, Japan)

- Laser Annealing (SHI, Japan)

Dicing Tape Si

**Full-cut Dicing**

Tape Laminating

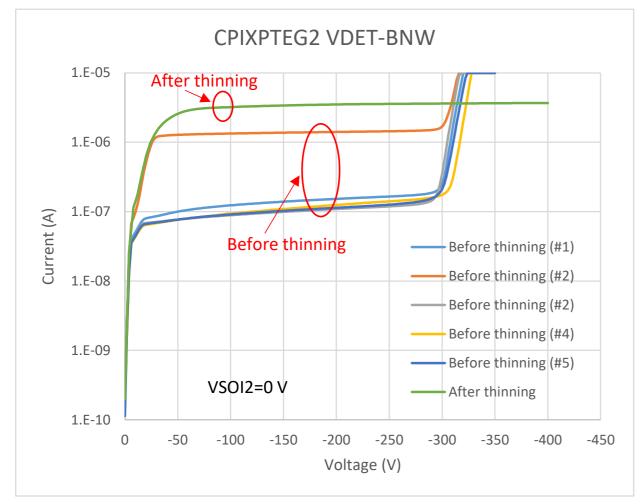

# Wafer Thinning

### **TAIKO Process by DISCO Corporation (Japan)**

### **Sensor I-V after thinning** (other SOIPIX)

Leak current increased by ~1.5 orders of magnitude. No break down by 400 V after thinning.

Still investigating these behavior.

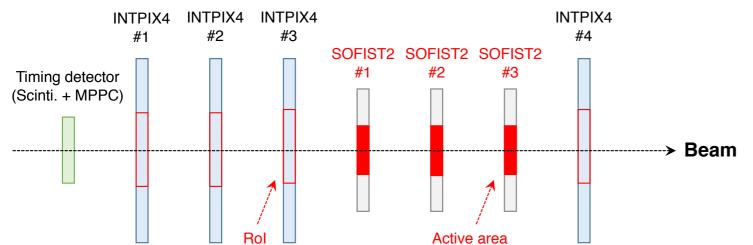

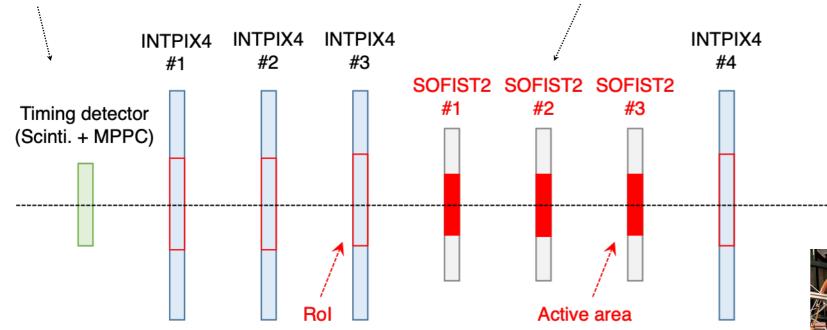

### Beam Test

Beam: 120 GeV proton (Fermilab Beam Test Facility, Jan. 2018)

DAQ rate: ~120 events/s

#### **Event Trigger and Timing detector**

Record hit timing for checking consistency to SOFIST.

Scinti. size:  $3 \times 3 \text{ mm}^2$ MPPC size:  $3 \times 3 \text{ mm}^2$

Readout: Comp. + AND + NIM converter

(Signal is sent to Master DAQ, SEABAS2)

#### **SOFIST ver.2**

Pixel size:  $25 \times 25 \mu m^2$

Pixel array:  $80 \times 64$  (2.0 × 1.6 mm<sup>2</sup>)

Readout: External 12-bit ADC (SEÁBAS2)

Sensor thickness: 75 µm

### **INTPIX4 (SOIPIX)**

Telescope for SOFIST Pixel size:  $17 \times 17 \mu m^2$

Pixel array: 832 × 512 (14.1 × 8.7 mm²) Function: Region of Interest readout Readout: External 12-bit ADC (SEABAS2)

### Beam Test Result

#### 位置分解能

テレスコープで再構成したトラックと **SOFIST** 上の ヒット位置の差

#### タイムスタンプの分解能

二枚の **SOFIST2** 間でのタイムスタンプの差 (互いのヒット位置が **2** ピクセル以内のもの)

### Readout and Sensor depletion layer

12-bit external ADC, 500 µm (Full depletion)

8-bit on-chip ADC, 500 µm (Full depletion) 12-bit external ADC, 200 µm (Partial depletion)

#### 位置分解能

### **SOFIST ver.1**

### タイムスタンプの分解能

SOFIST ver.2 #1 and #2

Intrinsic resolution: ~ 1.2 μm

(Position resolution of the telescope ~0.7 μm)

Intrinsic resolution: 2.19/√2 ~ 1.55 µs

### Time Stamp and Analog Pixel

### SOFIST ver.3

### **Pixel**

- Pre. amplifier (Charge sensitive amplifier)

- Comparator (Chopper inverter)

- Shift register

- Analog signal memories (three memories)

- Time stamp memories (three memories)

### On chip

8 bit column ADC

Pixel size:  $30 \times 30 \mu m^2$

ピクセル内に必要な全ての機能を実装した. ただしピクセルサイズは **30 µm** 角なので信号処理回路の評価が主な目的.

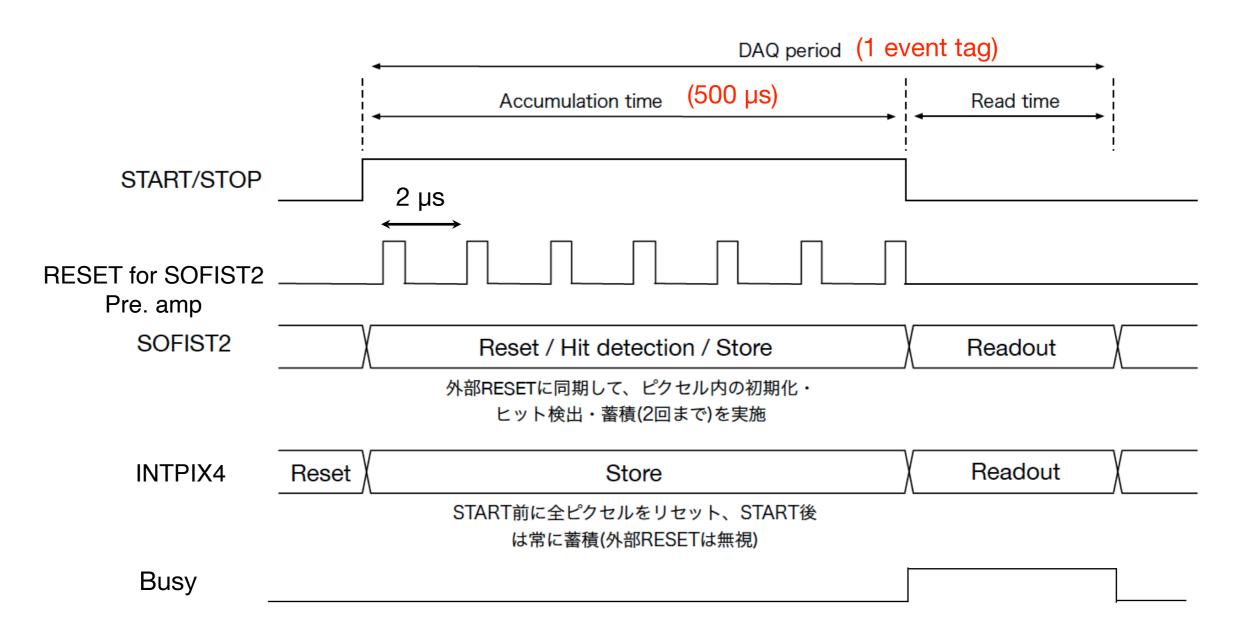

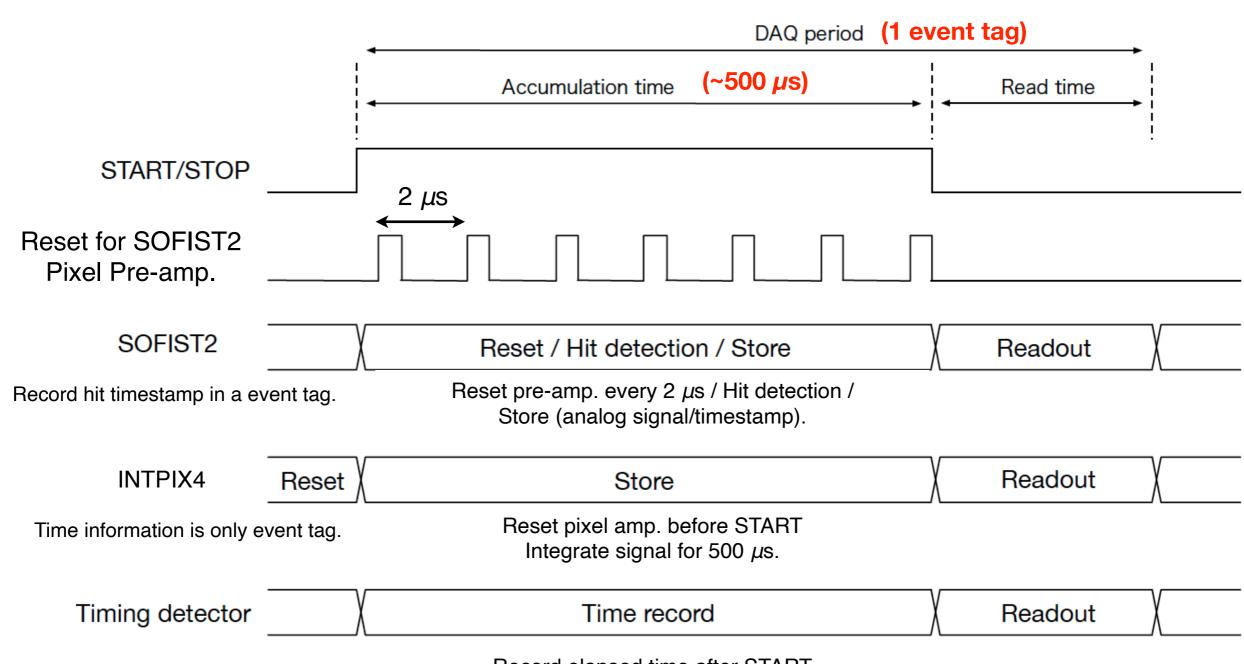

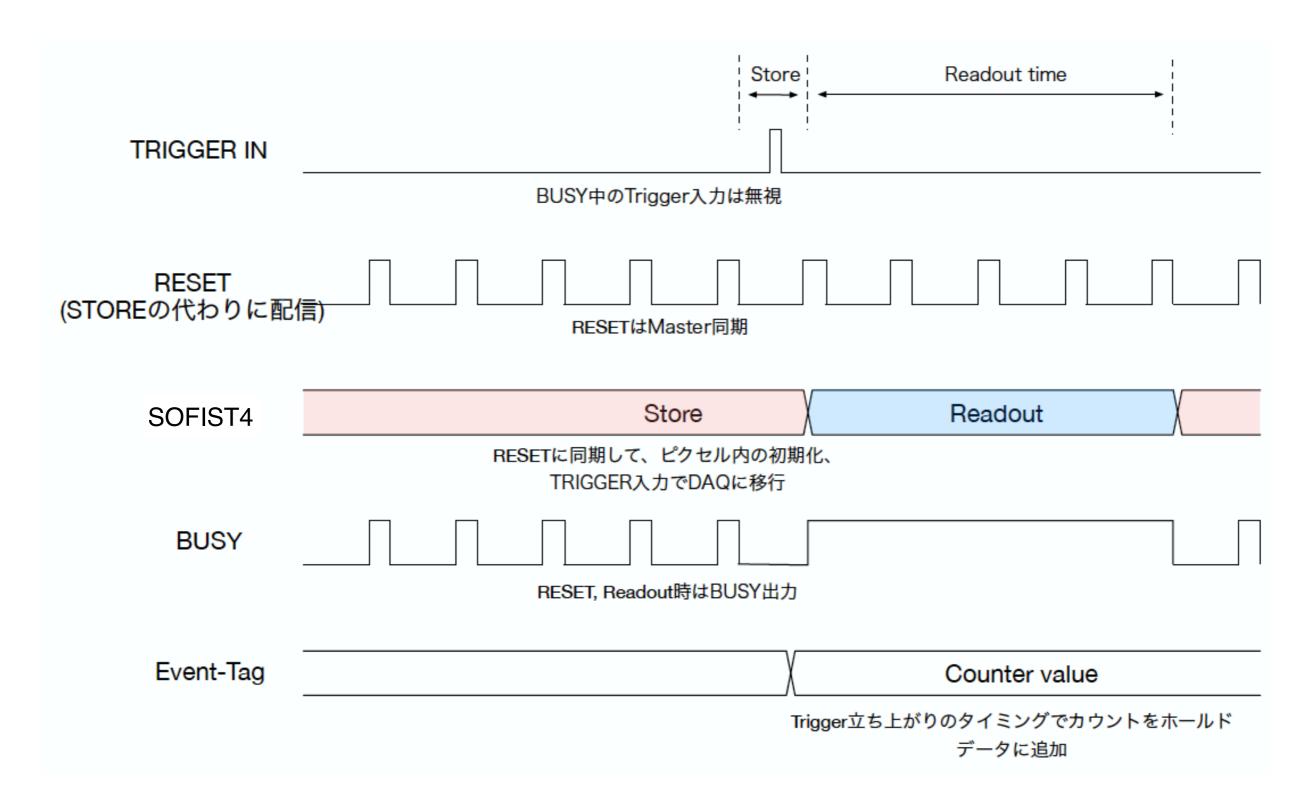

### 1 event tag あたりの各検出器の動作

Event tag trigger からシグナルを受け取ったら DAQ period (1 event tag) を開始する.

SOFIST2 は周期的にプリアンプのリセットを行い 500  $\mu$ s のあいだのヒットのタイムスタンプをピクセル内に記録する. INTPIX4 は 500  $\mu$ s のあいだ積分し続ける. 時間情報は event tag のみ.

リードアウト中は SOFIST2/INPIX4 から DAQ master へ busy を送る(event tag trigger を受け付けない).

### STORE Mode

### Operation of each detector in 1 event tag (DAQ period)

Record elapsed time after START for every hit detection for 500  $\mu$ s.

# Trigger Mode

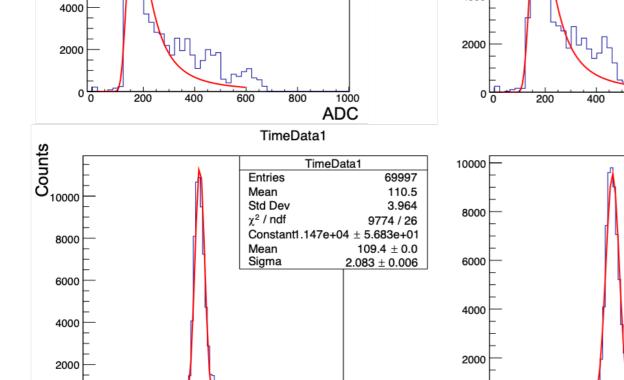

#### SOFIST3

#### Time difference of cluster size 2 event

In principle, timestamp of two pixels (cluster size 2) are the same.

Entries

Mean

Std Dev

$\chi^2$  / ndf

MPV

Sigma

**Analog signal**

Time stamp

**Analog signal**

Time stamp

**Analog signal**

Time stamp

AnalogData1

1.287e+04 / 26

69997

141.5

$173 \pm 0.4$

$25.34 \pm 0.22$

278

10000

8000

6000

4000

AnalogData1

Constan#.618e+04 ± 4.214e+02

120

140

160

μs

**Entries**

Mean

Std Dev

$\chi^2$  / ndf

MPV

Sigma

Counts

10000

8000

6000

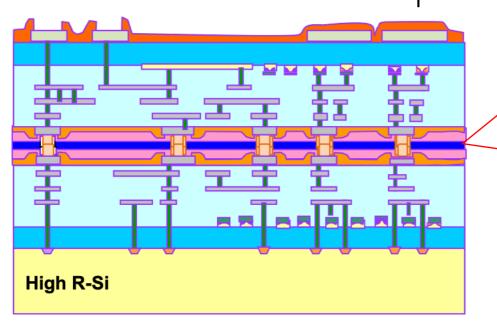

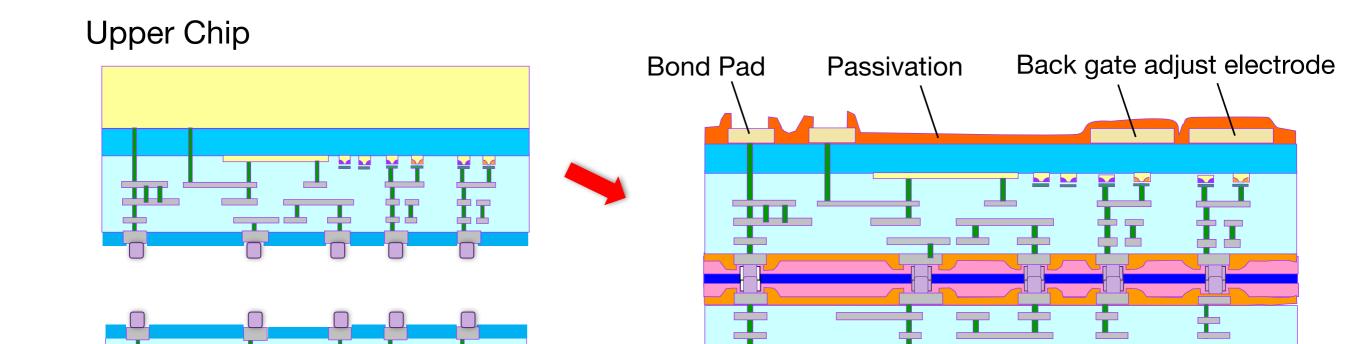

#### SOFIST4 Pixel

High R-Si

High R-Si

Lower Chip

#### Normal SOIPIX

SOIPIX for 3D Au Cylinder Bump (3  $\mu$ m $\Phi$ ) **Lower Chip** via 5 Au Under Bump Metal (5  $\times$  5  $\mu$ m<sup>2</sup>) Metal 5 Metal 4 Metal 3 **CMOS** Metal 2 Circuit Metal 1 Gate Poly Si **PMOS NMOS BOX** BNW *n*+ Sensor p-Handle Wafer D+ Al

# Au Micro Cylinder Bump

**Upper Chip**

**Lower Chip**

**Upper Chip**

Remove Sensor

by Wet Etching

2020/06/12 SOIPIX for the EIC at BNL 46

**Upper Chip**

Lower Chip

Metal 5 Alignment Mark

Cylinder bump

#### **Lower Chip**

#### Metal 5 Alignment Mark

#### SOFSIT4 Pixel

#### **Lower pixel**

#### **Upper pixel**

$20 \times 20 \,\mu\text{m}^2$

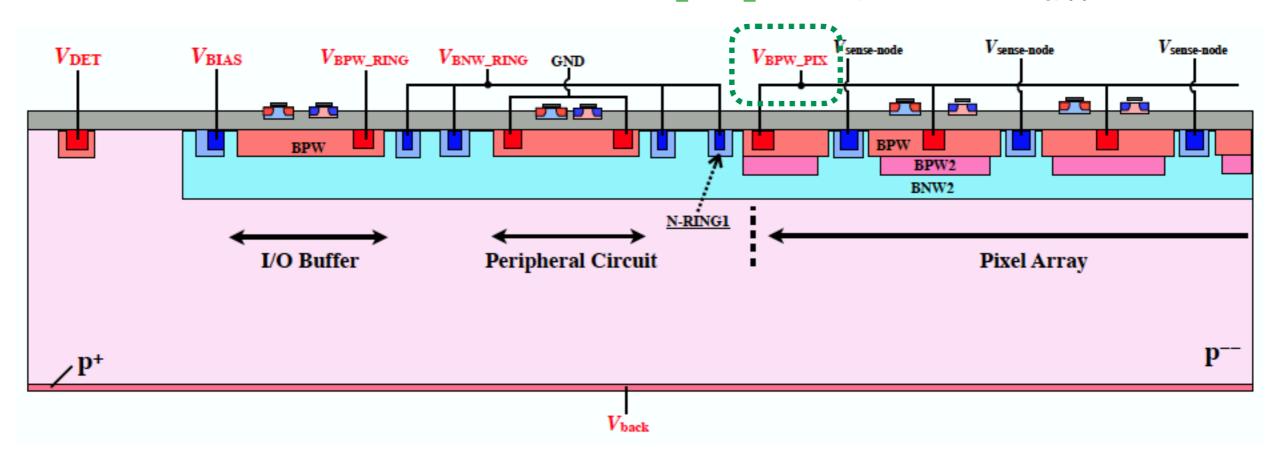

### PDD 構造

センスノード付近のポテンシャルは V\_BPW\_PIX で制御している.

#### **V\_BPW\_PIX** のチャージシェアへの影響は?

Run 247 - 252 V\_BPW\_PIX Scan: -1.1, -1.4, -1.6, -1.7, -1.8, -2.0 V

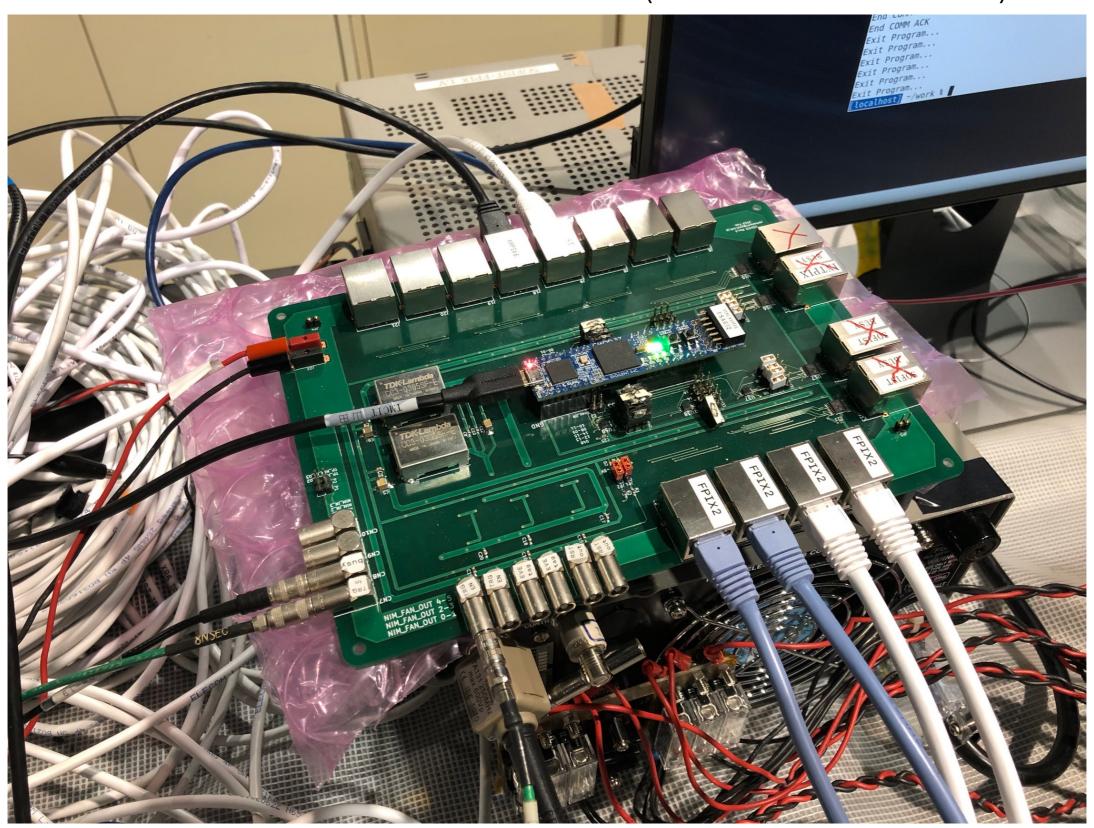

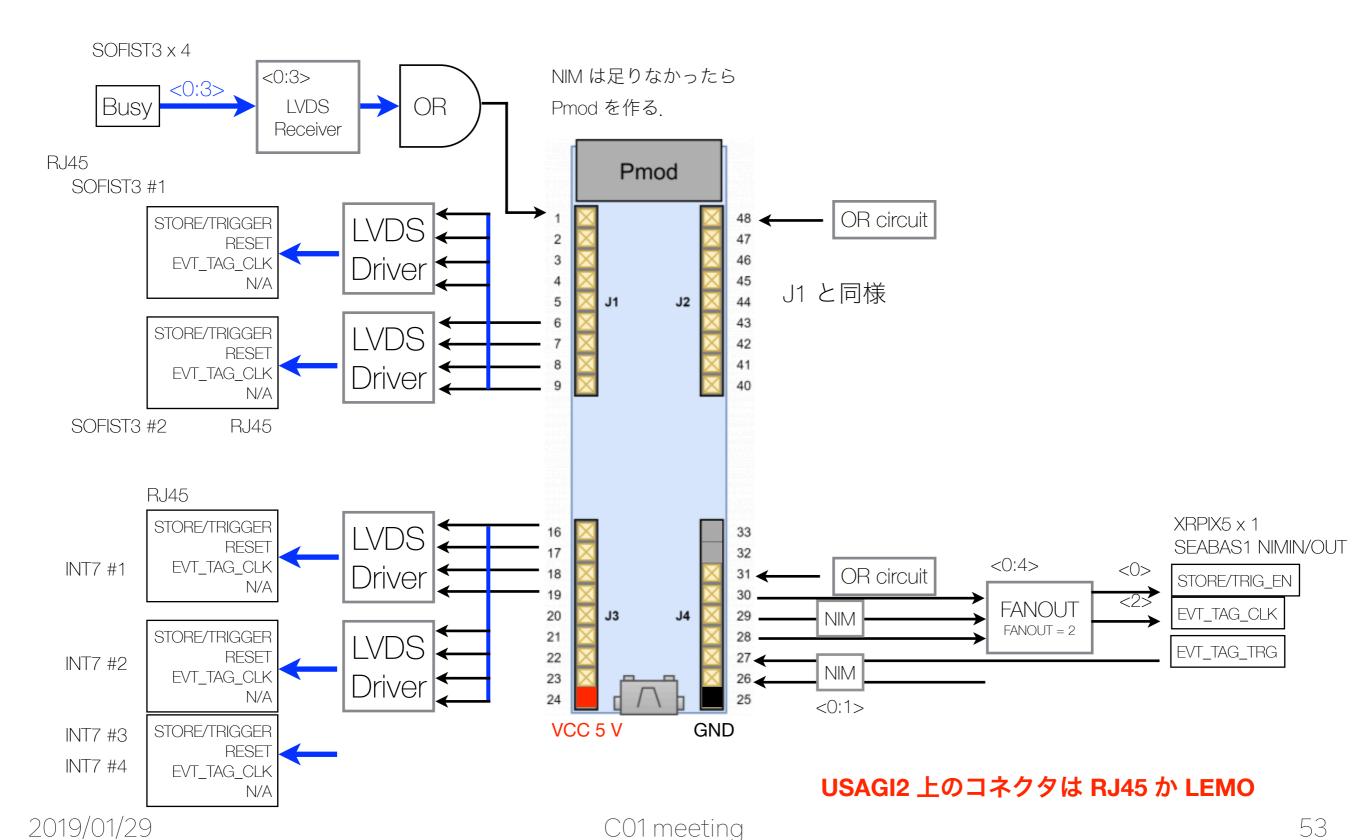

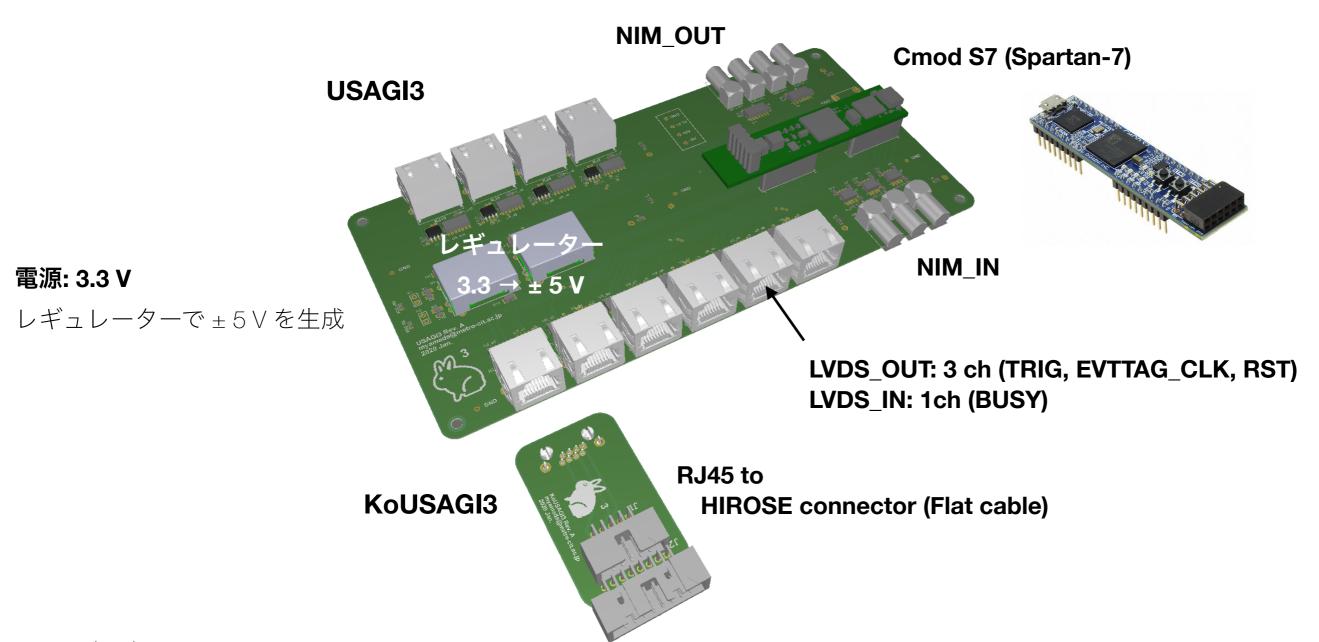

#### LVDS version 4 USAGI2 Conceptua

#### USAGI3 and KoUSAIG3

#### DAQ Master Board

Cmod S7 から DAQ に必要な信号を配布/受信するための I/O ボード 昨年の反省を踏まえて USAGI3 を作ったが、現地で殆どの LVDS ドライバーに不具合が起き(破損?ESD?) 結局 USAGI2 を使った(slave の BUSY の OR は NIM モジュールでとる).

JUITIA IUI LIIT EIU AL DINL