# **Chapt.8 Data Acquisition Systems**

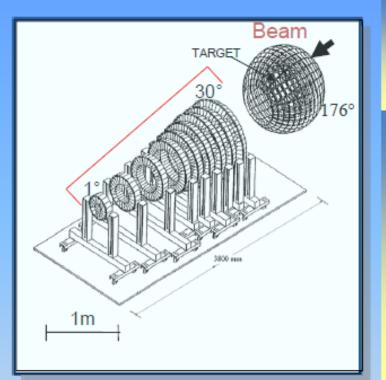

#### The CHIMERA Detector

#### 1192 Si-CsI(TI) Telescopes

18 rings in the range  $1^{\circ} \le \theta \le 30^{\circ}$

17 rings in the range  $30^{\circ} \le \theta \le 176^{\circ}$  (sphere)

High granularity and efficiency up to 94%  $4\pi$

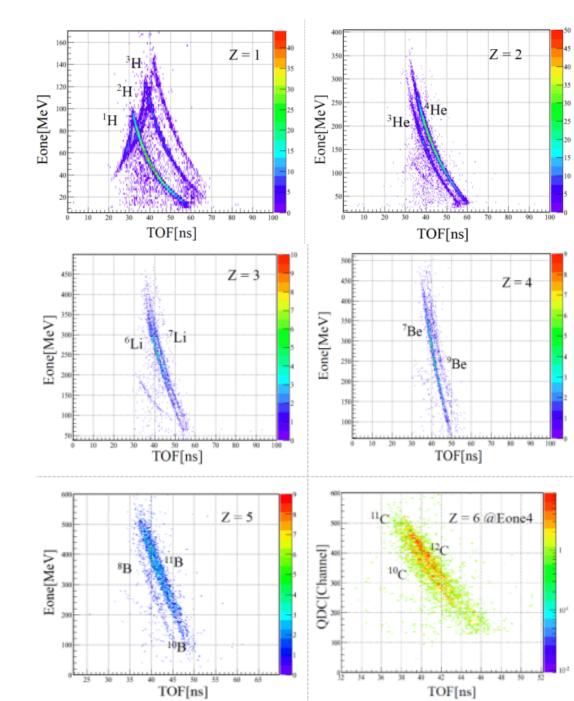

Z identification up to beam charge ( $\Delta E$ -E)

Z and A identification by  $\Delta E$ -E up to Z  $\leq$  9

Z and A identification in CsI up to  $Z \le 4$

Mass identification with low energy threshold (<0.3 A.MeV) by Time-of-flight

Zeta identification for particles stopping in Si (pulse

shape)

#### **Experimental Methods:**

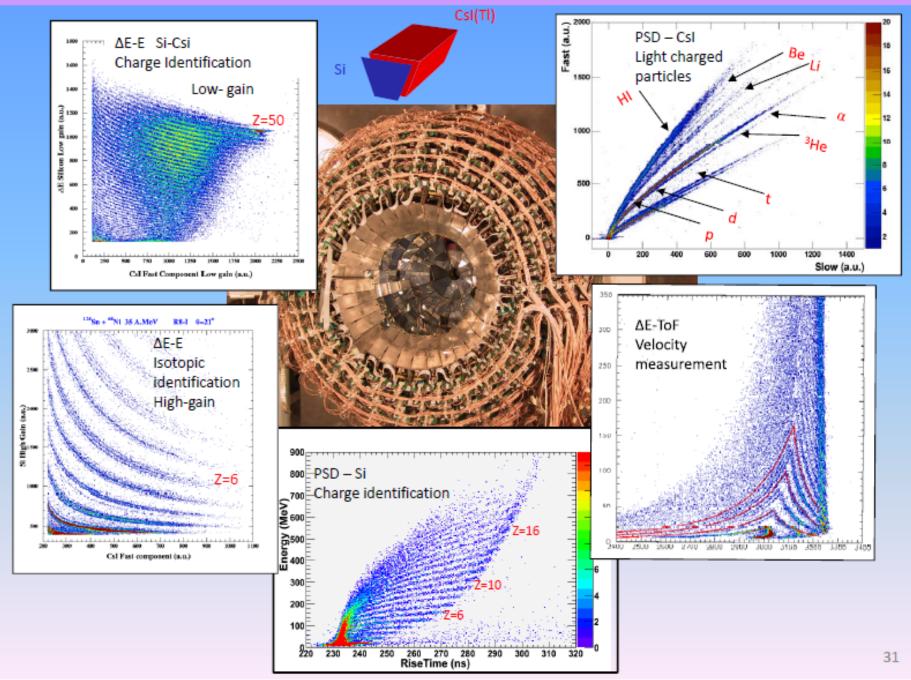

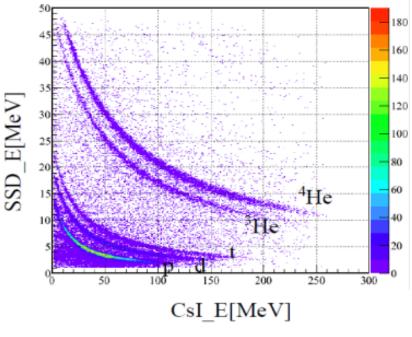

∆E(Si)-E(CsI(tl)): CHARGE, ISOTOPES

E(Si) – TOF(Si) VELOCITY - MASS

PULSE SHAPE in CsI(TI) p,d,t,<sup>3</sup>He,<sup>4</sup>He,.<sup>6,7,..</sup>Li,... Z<sub>light</sub><5 Pulse shape for particle stopping in Si (CHARGE)

#### **Chimera signals**

### Why do we need a Data Acquisition System ?

- •Primary objective is to have the most comprehensive information about the physical process under study.

- •For complex processes, many outgoing channels would require a large number of sensors and the simultaneous collection of data from all the channels.

Typical present generation experiments would have:

- >200 parameters per event

- 10,000 events per second

- $> 10^{12}$  bytes of data / experiment.

Needs high throughput and massive storage requirement.

•Detectors are large and distributed -containing many thousands of individual channels.

•The complete set of signals which describe a single nuclear interaction is called an Event. there can be thousands to millions of events occurring per second.

•Events occur at random.

```

Event1

Si1E, Si1T, CsI1E, CsI1Slow, CsI1Fast, CsI1T -Det1

Si2E, Si2T, CsI2E, CsI2Slow, CsI2Fast, CsI2T -Det2

....

SinE, SinT, CsInE, CsInSlow, CsInFast, CsInT -Detn

Timestamp

Event2

Event3

...

EventN

•Only a few events are interesting.

```

• The data acquisition system digitizes, formats and stores these information in a way which can be retrieved for later analysis.

### Trigger/Gate & Busy

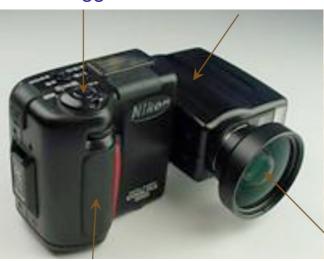

- Digital Camera is a "simple" physics DAQ system.

- 3-6 million channels

- Dead-time(BUSY) is important! -How long before I can take another picture??

Trigger

CCD detector Readout, processed

Light

Data stored on flash card

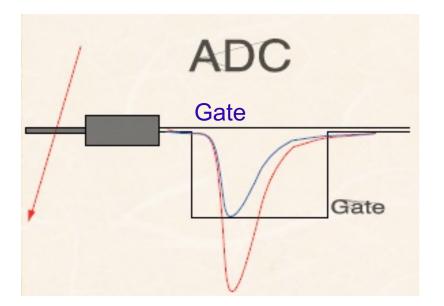

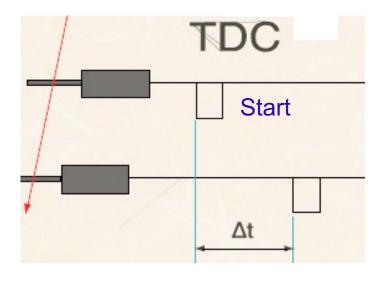

#### ADC/TDC Modules need a Trigger to start conversion

## Trigger

•The data acquisition system needs to know when an interaction "Event" has occurred in the detector.

•Some detectors are faster than others.

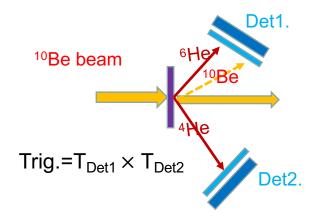

•Signals from fast detectors are combined to make a decision on when an interesting event has occurred. This is called a *trigger*.

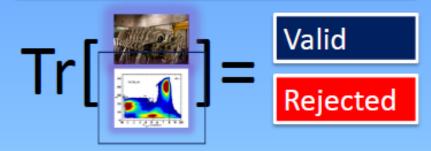

the trigger make a selection starting from the signals coming from the front-end electronics (hardware trigger) thus deciding if the event have to be readout or rejected.

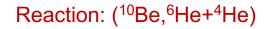

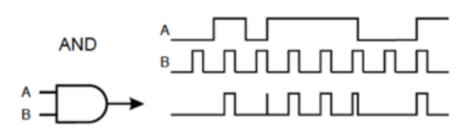

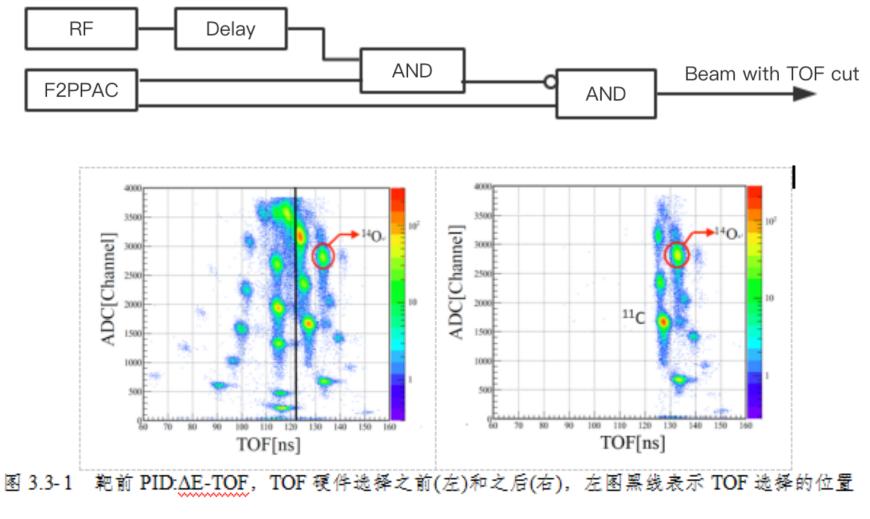

### **Basic trigger logic**

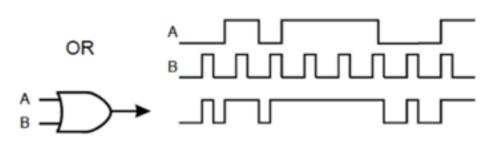

$\rightarrow$  AND: Output high, when both inputs are high.

$\rightarrow$  OR: Output high, when any input is high.

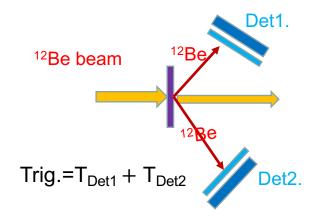

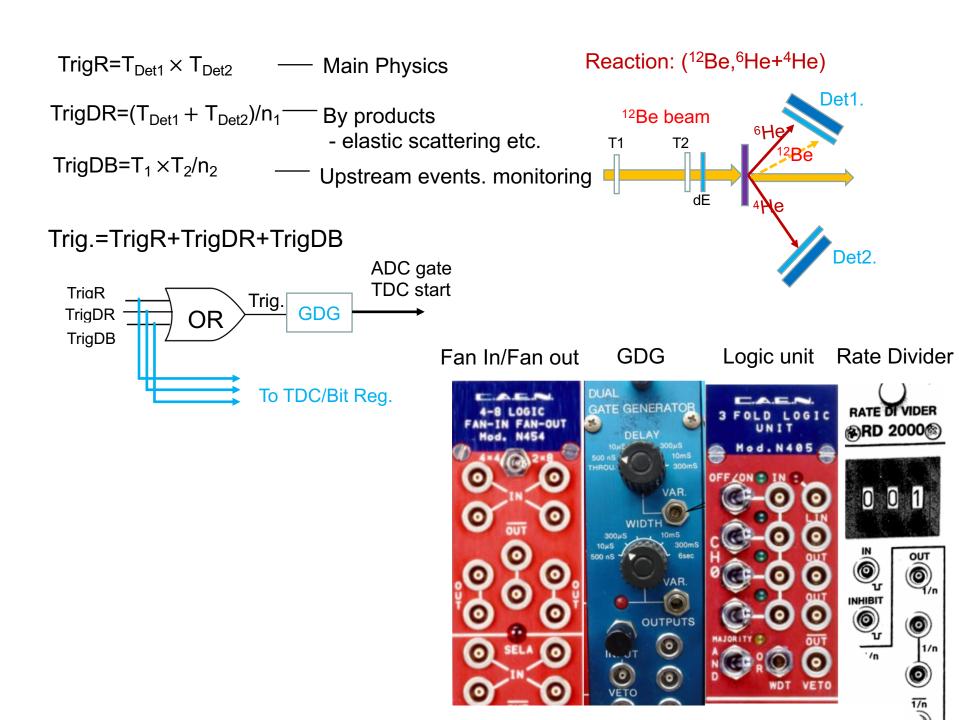

Reaction: (<sup>12</sup>Be, <sup>12</sup>Be')

$\mathsf{Trig.=T}_{\mathsf{Det2}} \times \mathsf{T}_{\mathsf{Neut}} \times \overline{\mathsf{T}}_{\mathsf{pla}}$

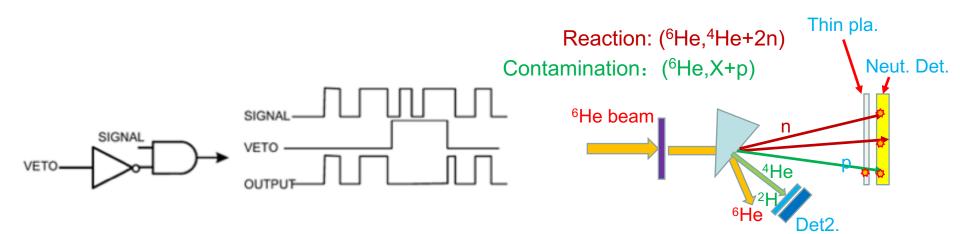

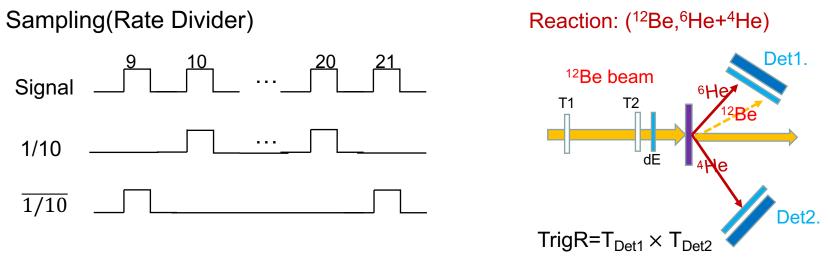

TrigDB= $(T_{det1} + T_{det2})/n$

sampling rate:1/n

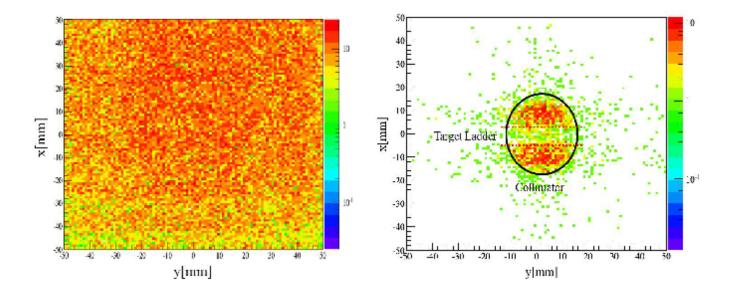

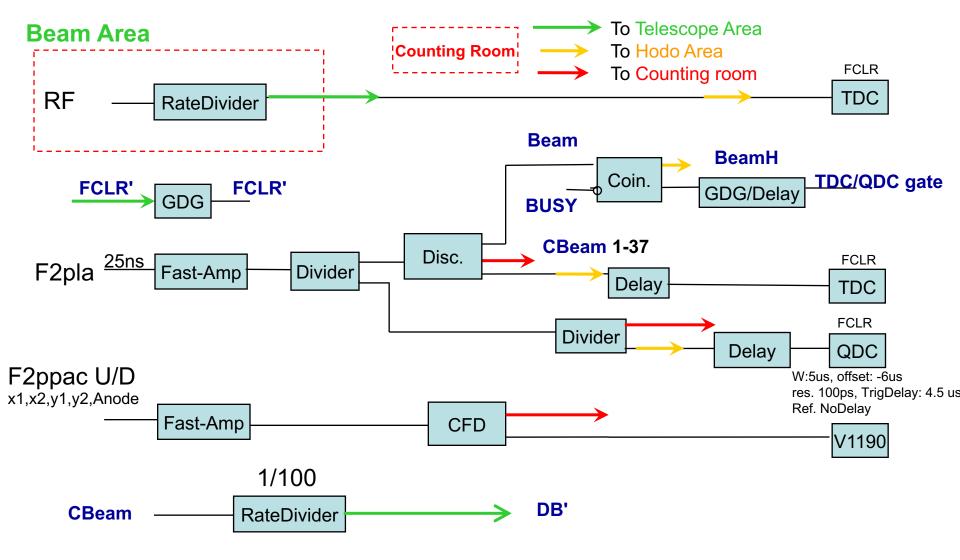

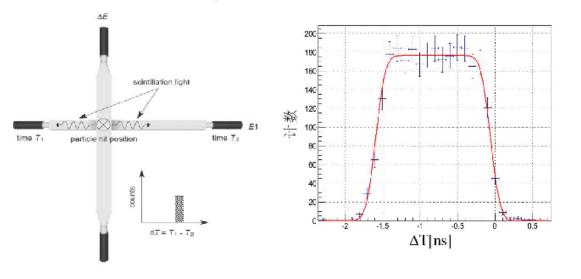

图 3.3-9 靶上束流的位置分布, 左图束流子触发的结果, 右图选择束流和 HODOSCOPE 符合的结果

### **Trigger** and DAQ

<u>TRIGGER</u>: the trigger make a selection starting from the signals coming from the front-end electronics (<u>hardware trigger</u>) thus deciding if the event have to be readout or rejected.

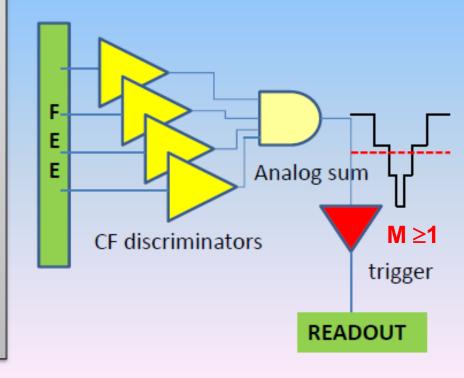

First level trigger L1: is based generally on hardware (discriminators, charged particle multiplicity, etc). It is generally fast (100ns-1µs).

Second level trigger L2: for example particle identification, energy calibration, etc. (CPUs, FPGA, etc). (milliseconds)

Third level trigger L3-Ln: in high energy physics, event reconstruction, physics processes (computer's farms). (10<sup>-2</sup>- 10<sup>0</sup> sec).

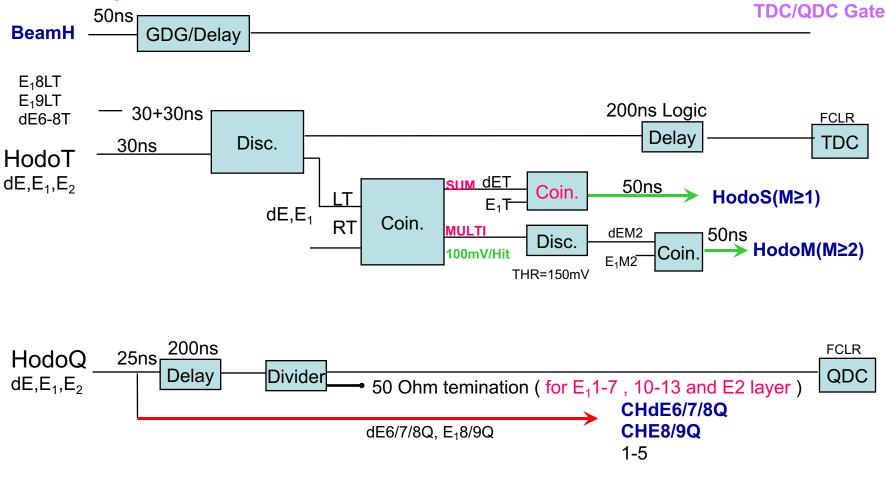

#### Simplified L1 trigger in CHIMERA based on particles Multiplicity

#### Trigger choice depends on detector and physics

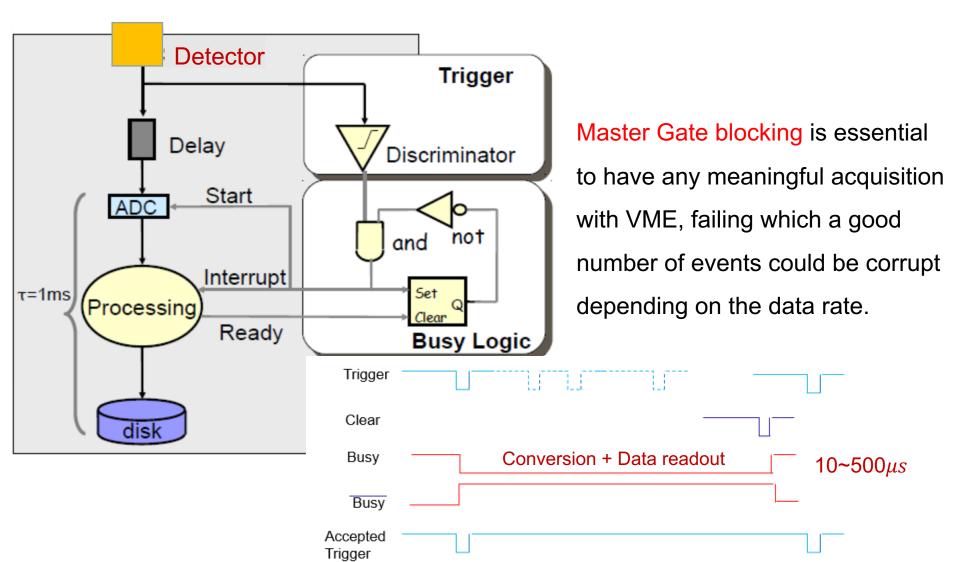

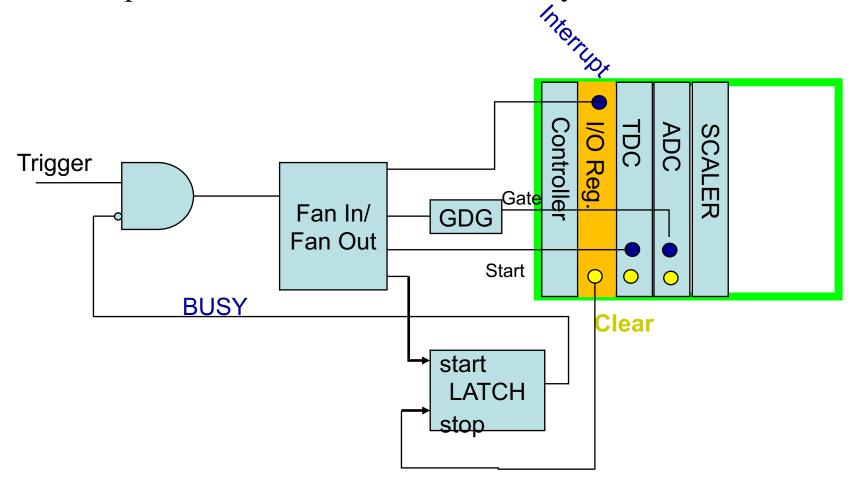

# real trigger & busy logic

• No master gate should reach the modules until the current event has been completely digitized and read out. (especially for VME)

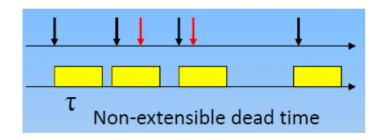

## **Deadtime and Efficiency**

Deadtime (%): ratio between the time the DAQ is busy and the total time .

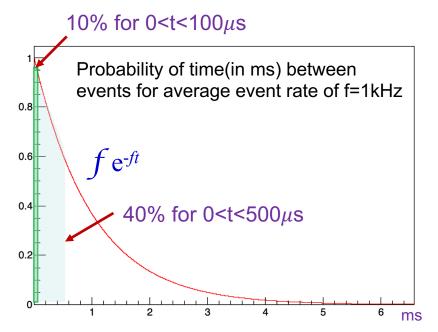

f=true interaction rate v=recorded count rate  $\tau$ =system dead time

$$v = n/(1+n\tau)$$

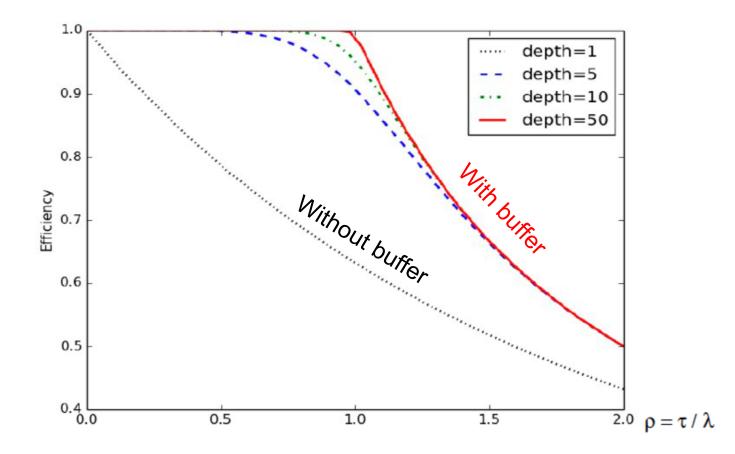

Efficiency: Nrecord/Ntot=  $1/(1 + f \cdot \tau)$

Due to the fluctuations introduced by the stochastic process the efficiency will always be less 100%

```

To have higher efficiency \rightarrow f \tau <<1

```

e.g. *f* =1kHz, ε >90%

$$\rightarrow \tau = 1/f (1/\varepsilon - 1) = 100 \mu s$$

$\rightarrow 1/\tau > 10 kHz$

In order to cope with the input signal fluctuations, we would need to overdesign our DAQ system by a factor 10.

Single cycle data readout: event by event readout

System BUSY = Conversion + Data readout

$\sim 10 \mu s$   $\sim a few 100 \mu s$

- Software cycle time to process an instruction

- Data transfer (only a event)

- Store to hard disk

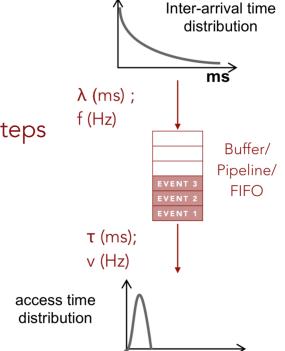

Buffers(FIFO) are introduced which hold temporarily the data. The FIFO absorbs and smooths the input fluctuation, providing a steady (De-randomized) output rate.

ex. Multi-Event Buffer: for CAEN v785 (VME ADC )

Busy is now defined by if the buffer is full or not.

Processor pulls data from the buffer at fixed rate, separating the event receiving and data processing steps

#### Data readout

- Software cycle

- Block Data transfer (multi-events)

- Store to hard disk

•Efficiency as a function of the ratio of the event processing time ( $\tau$ ) to average event arrival time ( $\lambda$ )

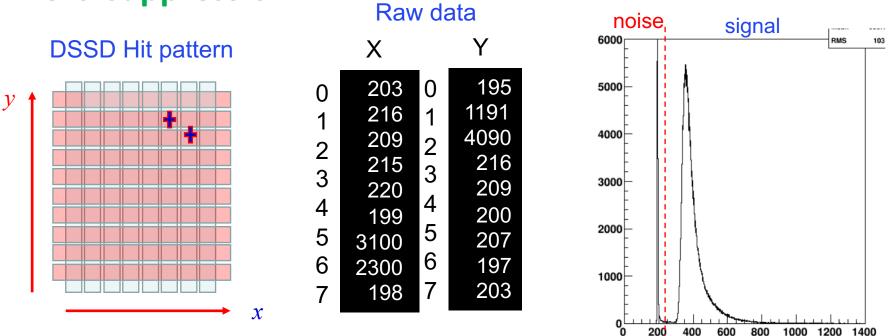

### **Zero-suppression**

Before event data is passed to the DAQ system it must be properly zero-suppressed to limit the loading of the data links and the DAQ system. Data must also be properly organized in self-describing data structures.

Zero-suppression(ADC) <-> Overflow-suppression(TDC)

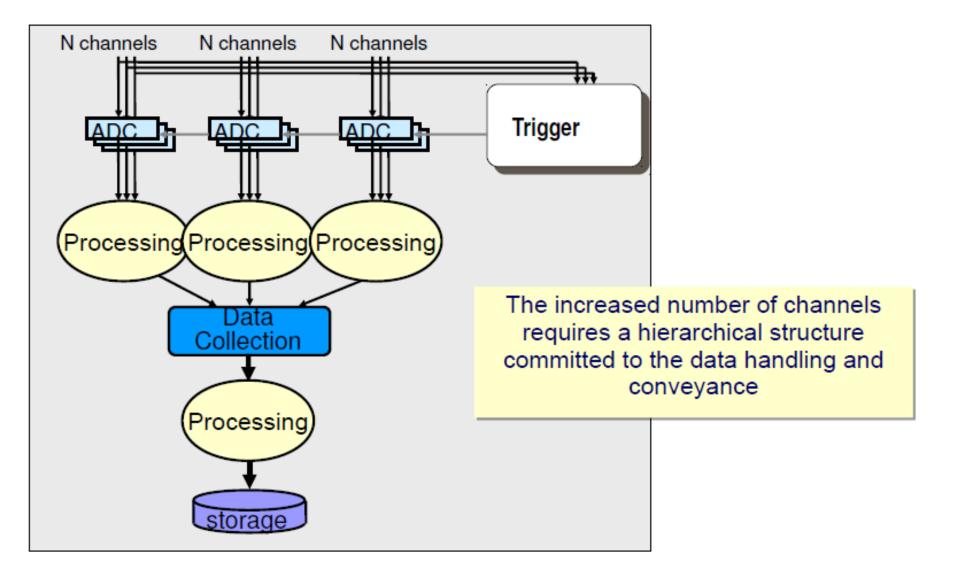

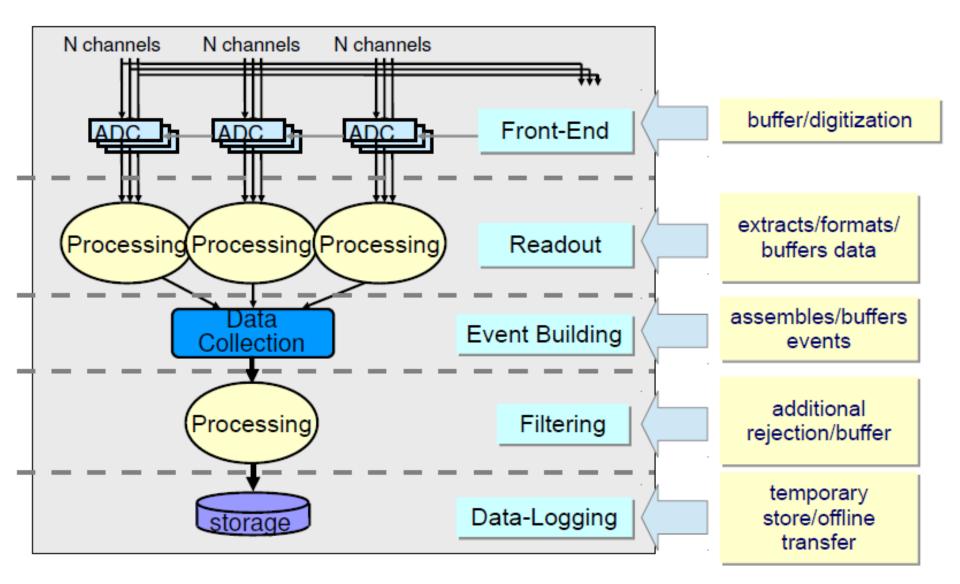

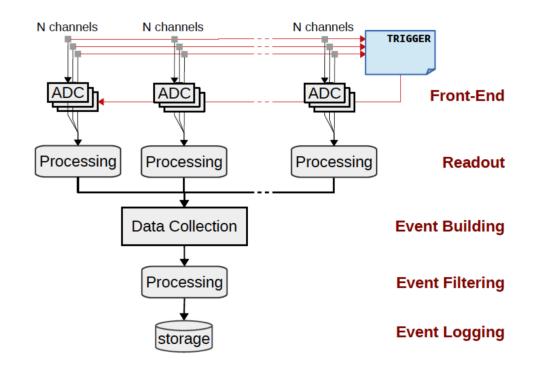

## Basic DAQ: more channels

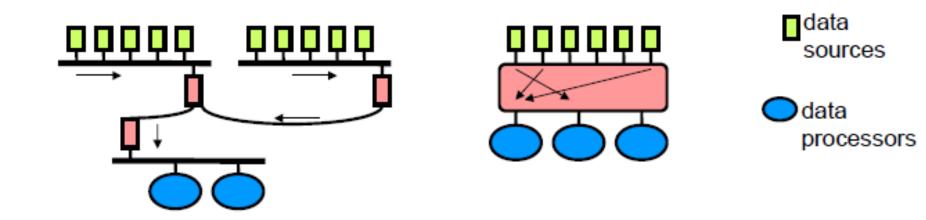

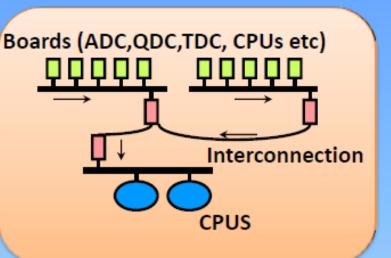

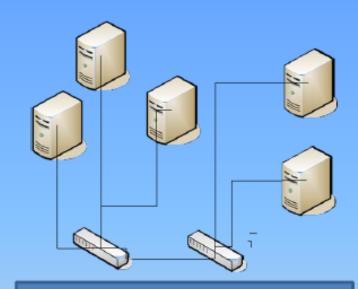

## Large DAQ: Constituents

If there are many channels, DAQ can be divided in blocks (for example all boards of a crate, all crates, a farm of computers to process data). All theses blocks have to be **interconnected**. Synchronization: to form full events from partial ones. **INTERCONNECTION Bus, Networks**

Two main classes: bus or network

## Buses

- → Esemples: VME, VXI, CAMAC, PCI, PCIe ...

- → Devices are connected by a "shared" bus

- → Devices can be "master" or "slave"

- → Devices can be addressed in a unique way in the bus.

- → Because the bus is shared among different board a bus "arbitrer" is generally necessary (VME)

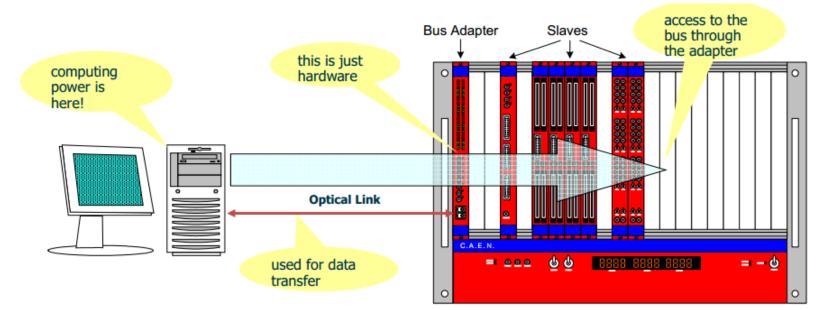

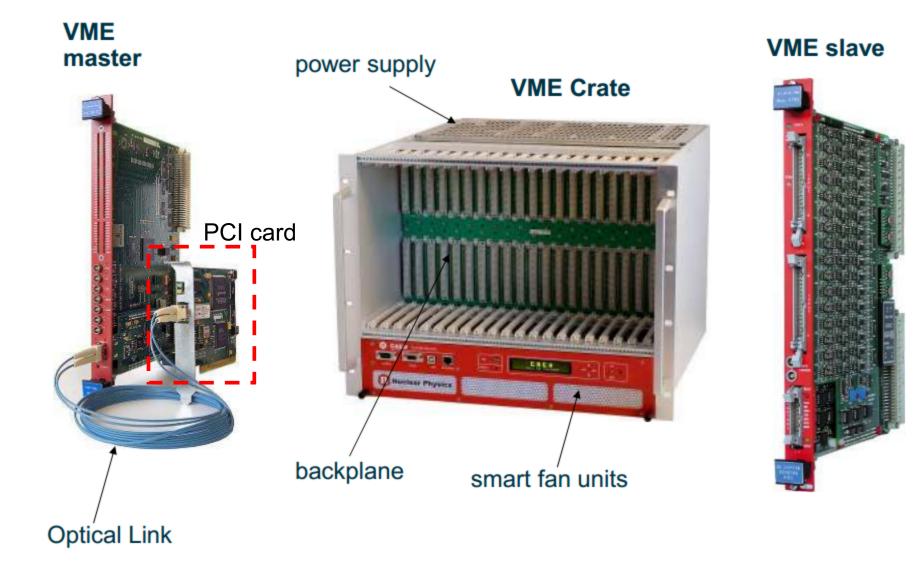

### Bus adapter/ controller:

- It makes possible to control the bus remotely from a standard PC through a high speed link

- The acquisition program (DAQ) runs on the remote PC

- Computing power (processors, memories, disks) is on the PC

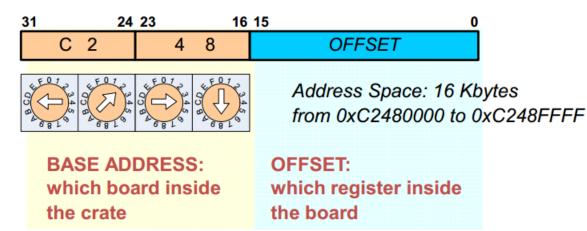

## Addressing:

All modules have a unique address in the bus.

Registers/buffers in a modules have a unique address.

Access and control modules through their addresses.

### Interrupt:

All modules included into the measurement are operated in the "master trigger" mode, i.e. a simultaneous data collection of all parameters is triggered by the interrupt given by one in particular defined module. The interrupt of the other modules are usually disabled.

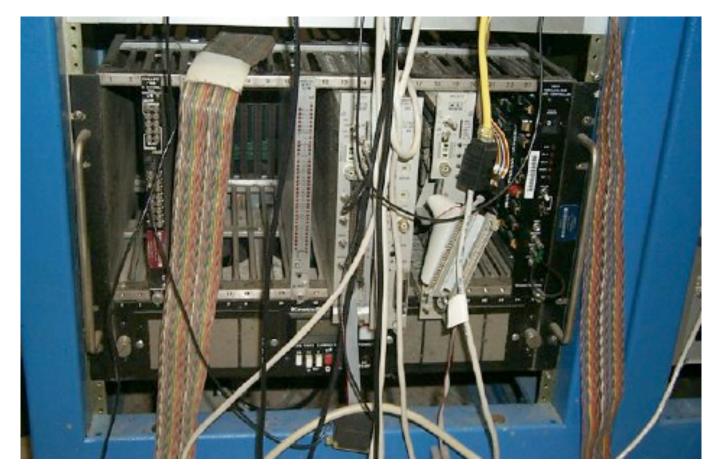

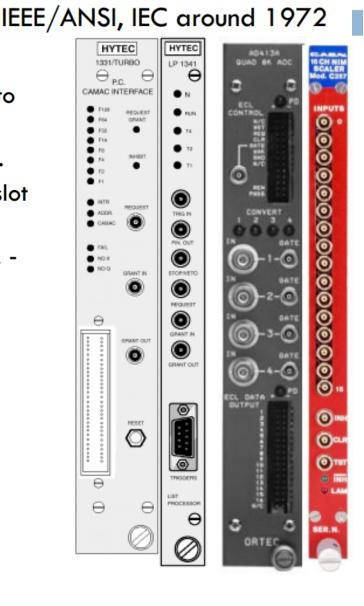

### CAMAC(Computer Automated Monitoring And Control)

Old IEEE Standard 24 bit bus.

Relatively slow(3 MB/sec).

Small boards.

A lot still around.

# CAMAC

## Specification

- 19" Crate, modular hardware form factor, 25 slots to attach modules.

- Crate contains power supply, backplane & FAN unit.

- Slot 25 is for CAMAC Crate controller module. The slot 1-24 may be occupied by CAMAC modules.

- The CAMAC backplane provides +6V, -6V, +24V & -24V, 0V (return) DC power; optionally +12V, -12V,

- CAMAC: Computer Automated Measurement And Control

- Standardized by ESONE,

## CAMAC backplane signals

#### CAMAC Data & Address lines:

24bit READ & 24bit WRITE bus.

- N Slot number: each slot is directly addressed by controller with this signal

- A sub-address : Each CAMAC module can host 16 sub-unit

- F Function: Each sub-unit can perform 32 functions

#### Control signals

- S1, S2: Timing signal for dataway operations

- 🗖 Z: Initialize

- Module responds with signals:

- 🗖 B: Busy

C: Clear

🗆 l: Inhibit

- L: Look At Me (LAM) signal. L line individually connects each slot to the controller, works as a interrupt to controller.

- Q: asserts the operation status

- X: asserts the command has been accepted

## **CAMAC** dataway operations

#### DATA WORD FORMAT

| 16 |            | 13 | 12 |              | 1 |

|----|------------|----|----|--------------|---|

|    | Channel ID |    |    | Channel Data |   |

CONTROL REGISTER FORMAT

| 16 9                         | 84 | 3         | 2         | 1          |

|------------------------------|----|-----------|-----------|------------|

| Conversion Delay (Read Only) | 0  | UT Enable | LT Enable | PED Enable |

#### CAMAC DATAWAY OPERATIONS

- F(0) •A(X) : Read event data memory for Channel (X+1). Data word as described above.

- F(1) •A(X) : Read the parameter memory pointed to by the most recent F17 operation for channel (X+1).

- F(4) •A(0)

Read Sparse Data. Only those channels with data that falls between the upper and lower thresholds are read, starting with the highest numbered channel. Reading an empty buffer returns Q false. Data word as described above.

- F(6) •A(0) : Read the Control Register. Format described above.

- F(6) •A(1) : Read the Hit Register. Shows which channels' pedestal corrected data falls within their upper and lower thresholds.

- : Test LAM. A Q=1 response is generated if LAM is present and enabled. The address lines have no effect on this command.

- : Clear the Module. Resets front end, clears and disables LAM, disables pedestals and thresholds. The address lines have no effect on this command.

- F(10) : Clear LAM. Occurs on S2 strobe. The address lines have no effect on this command.

- F(11) •A(0) : Reset the Control Register. Occurs on S2 strobe.

- F(11) •A(1) : Reset the Hit Register and LAM. No effect on data memory. Occurs on S2 strobe.

- F(11) •A(2) : Reset the Test Register. Occurs on S2 strobe.

- F(11) •A(3) : Reset the Hit Register, LAM and data memory. Occurs on S2 strobe.

- $F(16) \cdot A(X)$  : Write to data memory for channel (X+1).

## CAMAC based DAQ

All modules Triggered by the LAM (CAMAC Look-At-Me) given by one in particular defined module. This module is characterized by an enabled LAM line in contrast to the other modules where the LAM lines are automatically disabled

After getting the LAM the following data collection cycle is started

| Step | Operation                                             |

|------|-------------------------------------------------------|

| 1    | check LAM source                                      |

| 2    | inhibit all inputs (CAMAC inhibit I)                  |

| 3    | Read-out: read Module 1                               |

|      | read Module 2                                         |

|      |                                                       |

|      | read Module n                                         |

| 4    | clear all modules (CAMAC clear C), if enabled         |

| 5    | clear LAM                                             |

| 6    | data check and move into the data buffer              |

| 7    | monitor data check                                    |

| 8    | move into the monitor buffer and spectra accumulation |

| 9    | set back inhibit line                                 |

| 10   | optional CAMAC NAF ( if defined )                     |

#### A CAMAC Data Acquisition system with CC7700 and PC-Linux http://rarfaxp.riken.go.jp/~iwasa/cc7700.html

static int camacNAF(int N, int A, int F, long \*data, int \*stat) /\* long word data NAF operation \*/

static int dc int(unsigned short buffer[]) static long j; j=in1(BASE ADDRESS+4); pos=3; for(j=0;j<16;j++) { camacNAF(ADC1, j, 0, &i, &k); buffer[pos++]=i; for (j=17; j<32; j++) { camacNAF(TDC1, j, 0, &i, &k); buffer[pos++]=i;

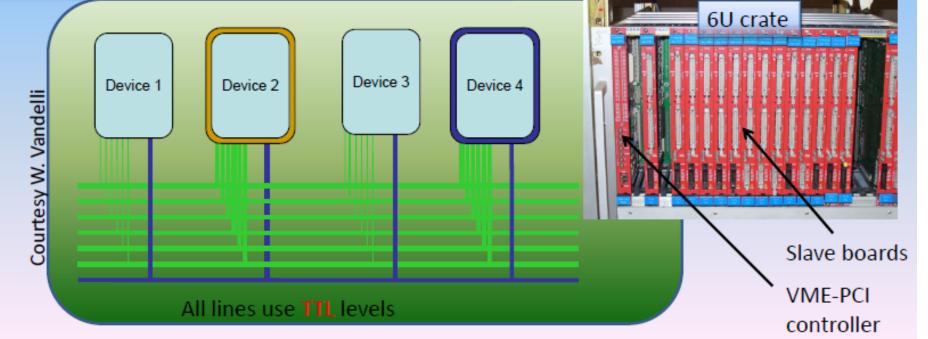

## VME (Versa Module Europa)

International standard for interconnecting modules.

32/64 bit bus (80MB/s)

Large number of commercial products (used heavily in the military).

VME64X provide bandwidth options (160-320 MB/s).

Currently transitioning from FASTBUS

- 19" crate with power supply unit & FAN unit

- Crate's height and depth depend on form-factor. 3U, 6U and 9U crates (1U=1.75") are available

- 6U VME64x crate has 21 slots and common backplane for all the signal and power lines

- p1 & p2 160pin and p0 is 95pin connector for each module

- +5V, +12V, -12V, +3.3V DC power are available in VME64X crate

- Hot-swappable, User IO

## VME modules

### CAEN VME785, 792 & 775

- 32 channel 12bit resolution

- 5.7us ADC conversion time for all 32channels

- 32event FIFO memory

- External ECL bus for control and synchronization

- BLT32, CBLT and MBLT capable

- MDI2, MADC32 from mesytec

Zero suppression Overflow suppression - to speedup data transfer, i.e. reduce dead time of DAQ

#### VME Base Address (Hardware Setting)

#### A32 mode

Table 4.2: Address Map for the Model V785

| Register content   | DR | SR           | HR           | Address       | Туре            | Access mode |

|--------------------|----|--------------|--------------|---------------|-----------------|-------------|

| Output Buffer      | ✓  | ✓            | ✓            | 0x0000÷0x07FF | Read only       | D32/D64     |

| Firmware Revision  |    |              |              | 0x1000        | Read only       | D16         |

| Geo Address        |    |              |              | 0x1002        | Read/Write (**) | D16         |

| MCST/CBLT Address  |    |              | ~            | 0x1004        | Read/Write      | D16         |

| Bit Set 1          |    | <b>√</b> (*) | <b>√</b> (*) | 0x1006        | Read/Write      | D16         |

| Bit Clear 1        |    | <b>√</b> (*) | <b>√</b> (*) | 0x1008        | Read/Write      | D16         |

| Interrupt Level    |    | ✓            | <b>~</b>     | 0x100A        | Read/Write      | D16         |

| Interrupt Vector   |    | ✓            | <b>~</b>     | 0x100C        | Read/Write      | D16         |

| Status Register 1  |    | ✓            | <b>~</b>     | 0x100E        | Read only       | D16         |

| Control Register 1 |    | <b>√</b> (*) | <b>√</b> (*) | 0x1010        | Read/Write      | D16         |

cmdvme -wr addr cmdvme -wr 0xC2480000 : word read

: read a word from the first channel of the module

#### Data Output Buffer

| [ | 31 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22  | 21   | 20   | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12   | 11         | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|-------|----|----|----|----|----|----|----|-----|------|------|----|----|----|----|----|----|----|------|------------|----|---|---|---|---|---|---|---|---|---|---|

|   | G     |    | 0  | 1  | 0  |    |    | CF | RAT | 'E[7 | 7:0] |    |    | 0  | 0  |    | С  | NT | [5:0 | <b>)</b> ] |    |   |   |   |   |   |   |   |   |   |   |

#### Fig. 4.5: Output buffer: the Header

V785:

| 31 | 30 | 29  | 28  | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18           | 17  | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5    | 4  | 3 | 2 | 1 | 0 |

|----|----|-----|-----|----|----|----|----|----|----|----|----|----|--------------|-----|----|----|----|----|----|----|----|---|---|---|-----|------|----|---|---|---|---|

|    | GE | 0[4 | :0] |    | 0  | 0  | 0  |    |    |    |    | -  | ANN<br>(4:0) | IEL |    |    |    | UN | ov |    |    |   |   | A | DC[ | 11:0 | )] |   |   |   |   |

| 31 30 29 28 27 | 26 | 25 | 24 | 23 | 22 2 | 12 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11  | 10  | 9    | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------|----|----|----|----|------|----|----|----|----|----|----|----|----|----|----|-----|-----|------|------|---|---|---|---|---|---|---|---|

| GEO[4:0]       | 1  | 0  | 0  |    |      |    |    |    |    |    |    | EV | EN | тс | ou | JNT | FER | R[23 | 3:0] |   |   |   |   |   |   |   |   |

Fig. 4.7: Output buffer: the End Of Block

|                  | 31 | 30 | 29  | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 0 19 | 91  | 8   | 17  | 16 | 15 | 14  | 13   | 1  | 21    | 1 1 | 0    | 9    | 8   | 7 | 6  | 5   | 4   | 3  | 2 | 1 | 0 |

|------------------|----|----|-----|----|----|----|----|----|----|----|----|----|------|-----|-----|-----|----|----|-----|------|----|-------|-----|------|------|-----|---|----|-----|-----|----|---|---|---|

| Write            |    | (  | GEC | )  |    | 0  | 1  | 0  |    | C  | RA | TE | NU   | MB  | ER  |     |    | 0  | 0   | ME   | M  | 1. CH | IAN | NE   | LS   | (2) |   |    |     |     |    |   |   |   |

| Pointer          |    | (  | GEC | )  |    | 0  | 0  | 0  |    |    | 0  | CH | IAN  | INE | EL  | (2) |    |    |     | UN   | lo | v     |     |      |      | /   |   | СС | XOU | IN  | s  |   |   |   |

| N                |    | (  | GEC | )  |    | 0  | 0  | 0  |    |    | 0  | CH | IAN  | INE | EL  | (5) |    |    |     | UN   | lo | v     |     |      |      | /   |   | СС | XOU | IN  | s  |   |   |   |

| GATE 5           |    | (  | GEC | )  |    | 1  | 0  | 0  |    |    |    |    |      |     |     |     |    |    | EVE | INT  | C  | OUN   | ITE | R(   | m)   |     |   |    |     |     |    |   |   |   |

|                  |    | (  | GEC | )  |    | 0  | 1  | 0  |    | С  | RA | TE | NU   | MB  | ER  |     |    | 0  | 0   | ME   | M  | I. CH | IAN | NE   | LS   | (3) |   |    |     |     |    |   |   |   |

| Write<br>Pointer |    | (  | GEC | )  |    | 0  | 0  | 0  |    |    | 0  | CH | IAN  | INE | EL  | (0) |    |    |     | UN   | lo | v     |     |      |      | 1   |   | СС | XOU | IN  | ſS |   |   |   |

| N+1              |    | (  | GEC | )  |    | 0  | 0  | 0  |    |    | С  | ж  | ANI  | NE  | L ( | 17) |    |    |     | UN   | lo | v     |     |      |      | /   |   | СС | XOU | IN  | s  |   |   |   |

| GATE 8           |    | (  | GEC | )  |    | 0  | 0  | 0  |    |    | 0  | CH | IAN  | INE | EL  | (3) |    |    |     | UN   | c  | v     |     |      |      | /   |   | СС | XOU | JNT | S  |   |   |   |

|                  |    | (  | GEC | )  |    | 1  | 0  | 0  |    |    |    |    |      |     |     |     |    | E  | VE  | NT C | 00 | NUC   | TER | t (m | 1+3) |     |   |    |     |     |    |   |   |   |

#### Fig. 4.9: Multi-Event Buffer: data structure example

### VME Data Readout

Data readout is possible in following modes -

- Single cycle

- Reads a word from the slave FIFO

- BLT/MBLT (Block Transfer/Multiplexed Block Transfer)

- Reads a number of events limited to 256 words from any slave module

- In MBLT two 32 bit words are multiplexed to read as a single 64-bit word in VME64 standard

- CBLT (Chained Block Transfer)

- Most pertinent mode for nuclear physics applications allowing for eventby-event data acquisition.

- Reads the data belonging to the same physical event from several contiguous boards in a crate limited to 256 words per CBLT cycle

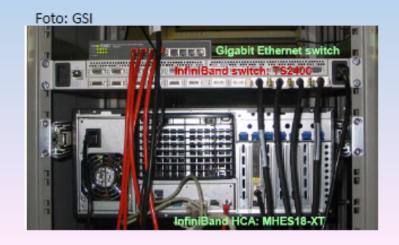

## **READOUT NETWORKS IN A DAQ**

INTERCONNECTION IS OBTAINED BY SWITCHES (it switchs frames to destination using MAC) It is possible to connect and exchange data between different "crates" or devices in a network making in parallel the readout of different parts of a multidetector

A network can link also different devices (for example permitting the coupling of different data acquisitions (in a network the connected devices are called "nodes" or "peers" (no master or slaves). In a network devices communicates directly (or through a switch) exchanging data and messages.

#### ETHERNET is the most used protocol

Others high bandwidth (datatransfer/second) , low latency protocols , low distances: INFINIBAND MYRINET

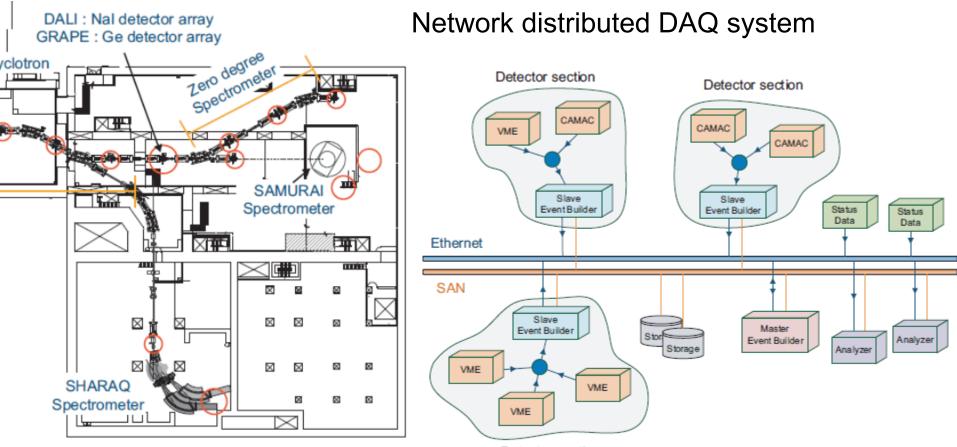

Detector section

### **Event Building**

- The detectors are spread over a physical volume of space.

- Bits and pieces of events arrive at different times from different places.

- All the parts of the event need to be collected together and packaged with other information needed by the analysis.

The Event builder is a very fast collating machine.

### **Run Control**

- Need to start and stop the DAQ

- Place to input parameters which change from run to run.

- Place to read parameters from.

- Automatic monitor of the health of the DAQ system.

- Something nice for the operator to look at.

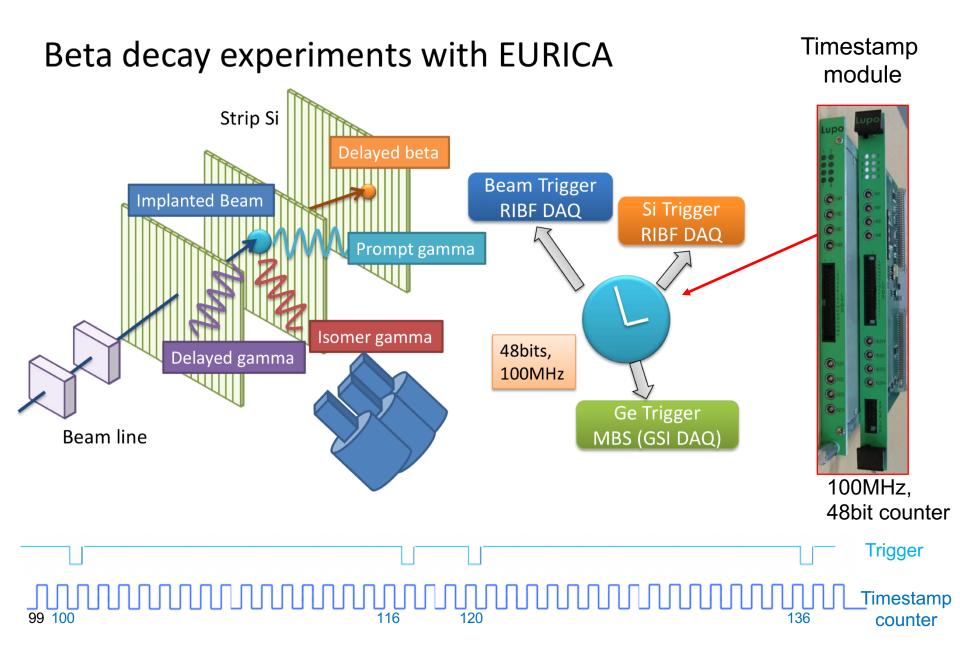

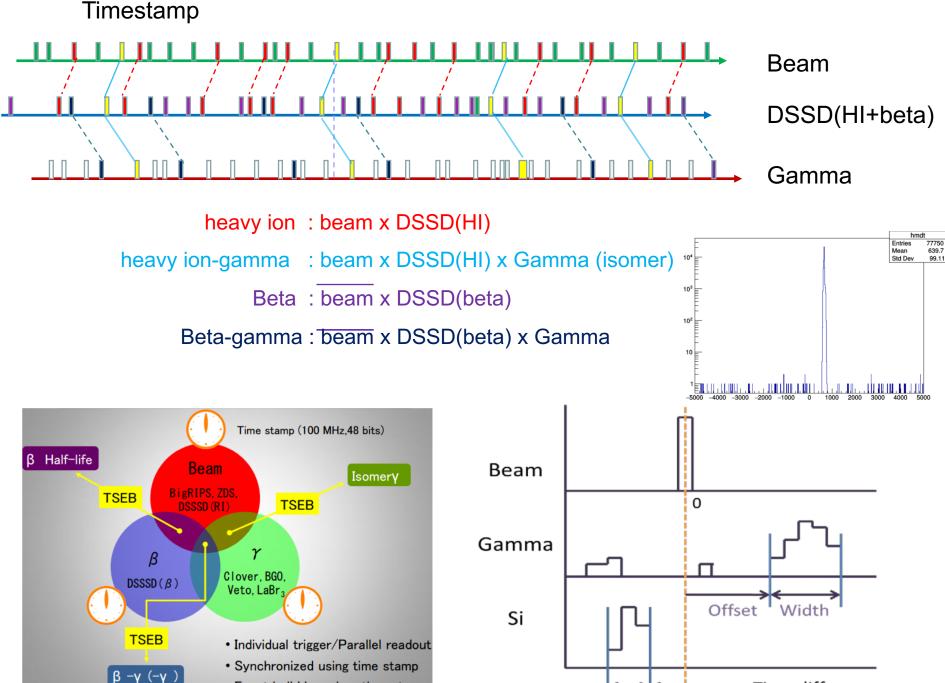

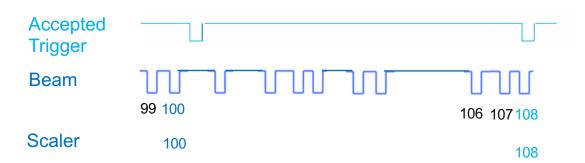

# **Timestamp-based DAQ**

- Independent DAQ for each sub-system

own trigger and timestamp

- Synchronize sub-systems with timestamp

- fixed time difference and offset

• Event build based on time stamp

Time difference

#### Application:

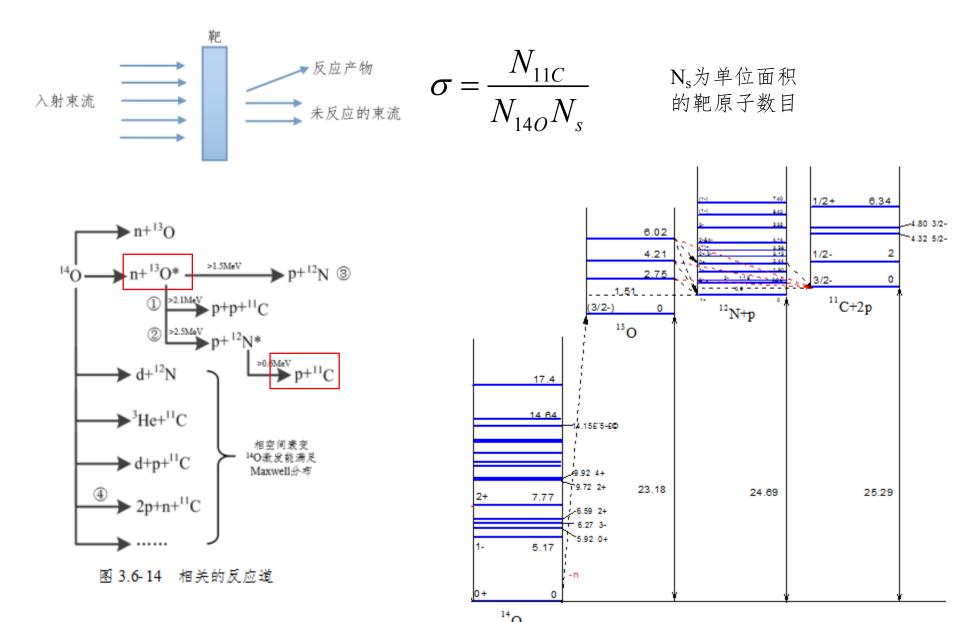

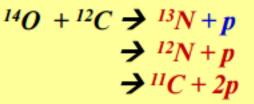

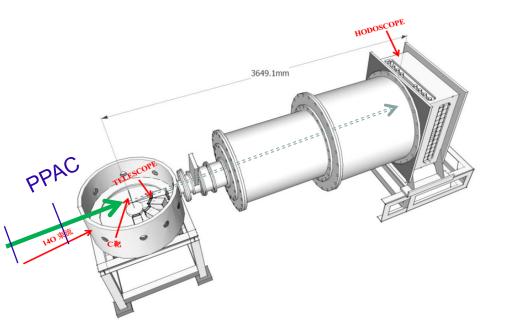

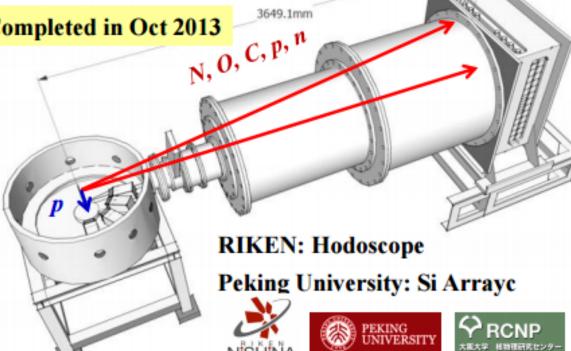

# Study of Knockout Reaction Mechanism from $^{14}\mathrm{O}$ at $60\mathrm{MeV/u}$

Phys. Rev. C 93, 044607 (2016)

#### Physics goal: the breakup reaction cross section of $^{14}O$ to $^{11}C$

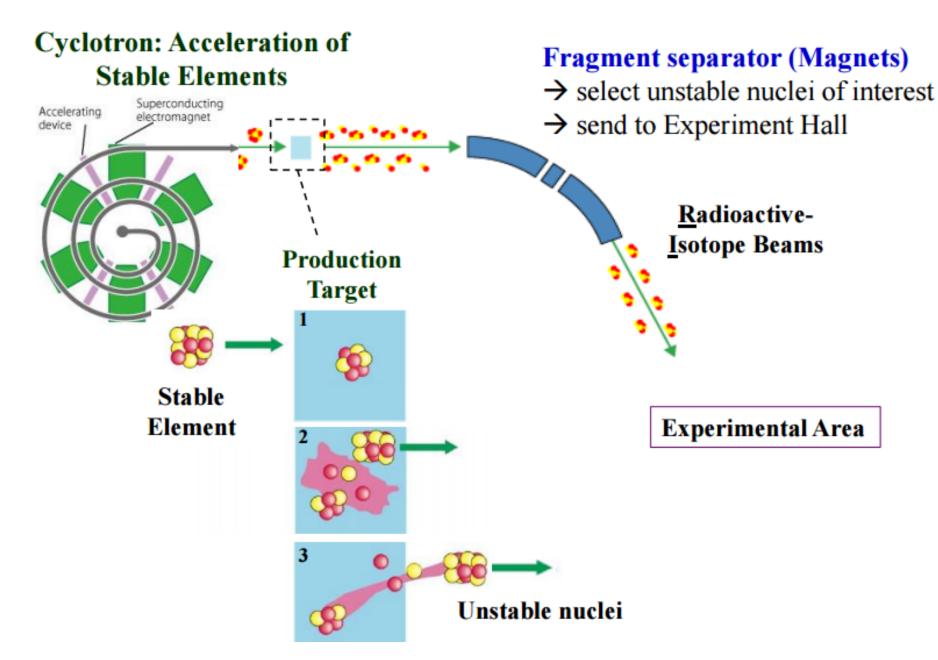

# **Radioactive Isotope Beam Production**

Hiroshim

okushima

Nagasak

Hokkaido

Aomori

Sendal Fukushima

Tokyo

Sapporo Niseko

# **Study of Reaction Mechanism**

Fully Exclusive Measurements of reaction products

大阪大学・核物理研究中心 Osaka University Research Center for Nuclear Physics

#### **EN-Course Beam line**

## **Beam production**

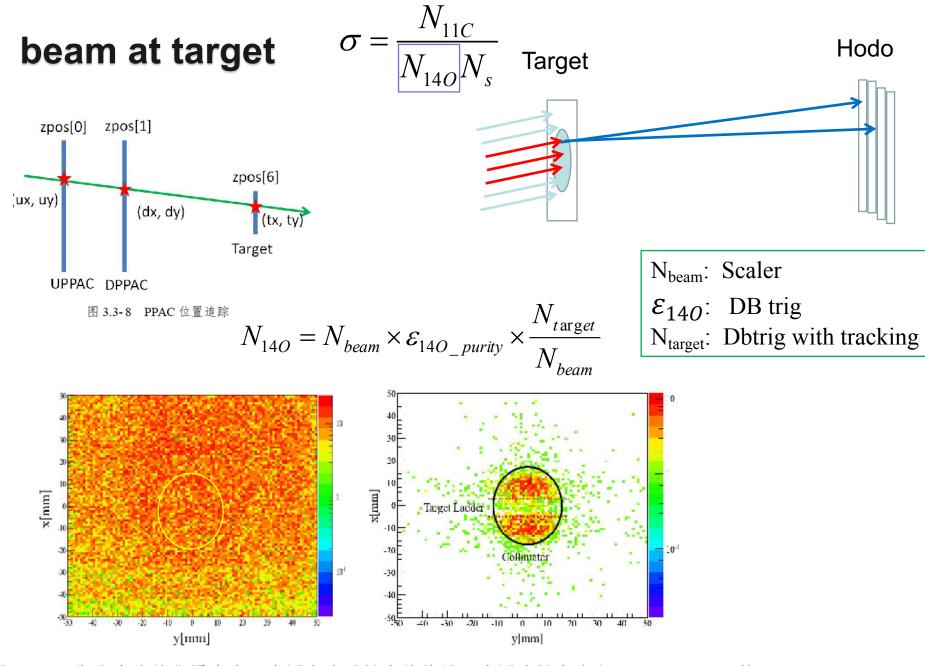

$$\sigma = \frac{N_{11C}}{N_{14O}N_s}$$

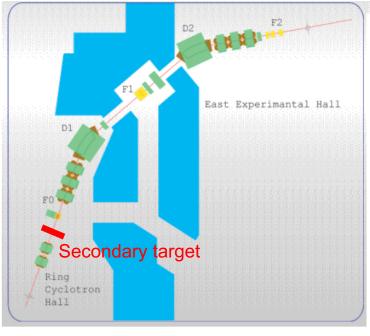

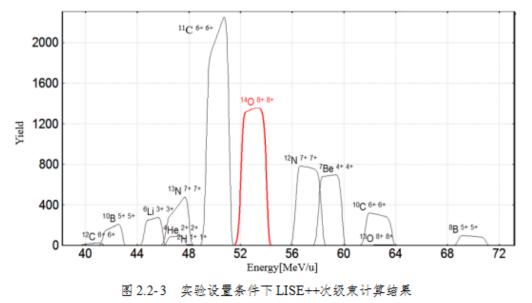

<sup>14</sup>O 次级東流通过78.2MeV/u 的 <sup>16</sup>O 在 2.1mm 的 <sup>9</sup>Be 靶上产生。

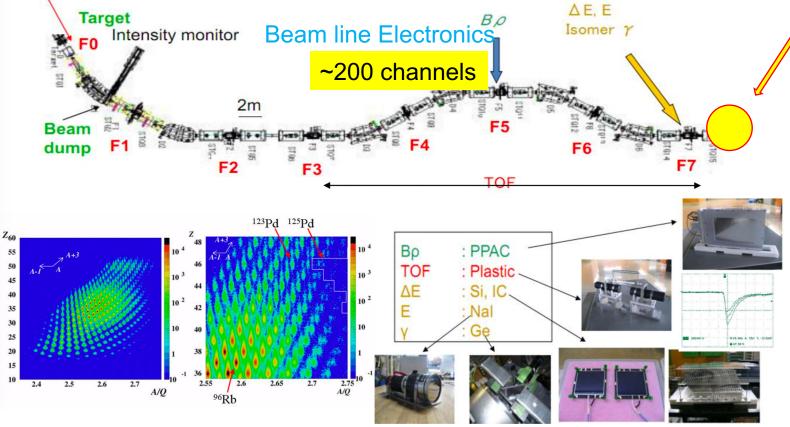

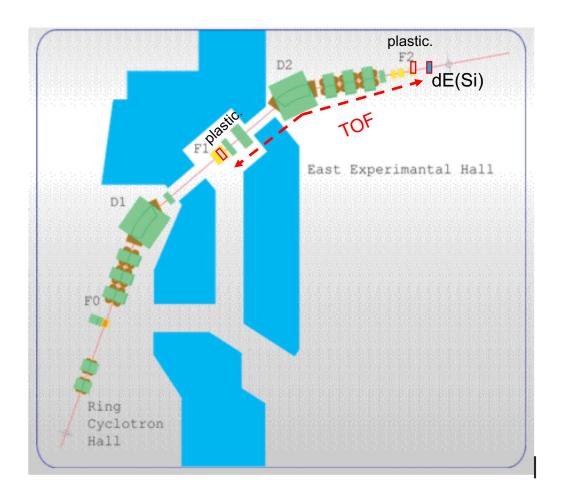

#### Secondary Beam line @RCNP

图 2.2-2 RCNP EN Course 東流线设置

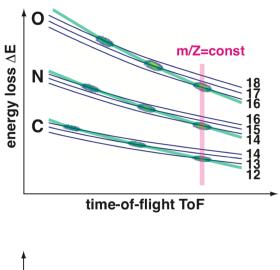

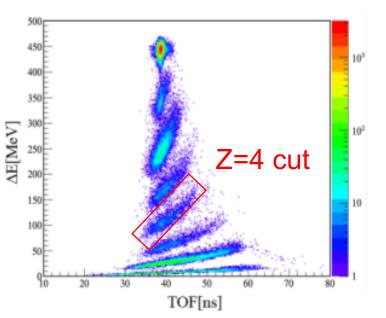

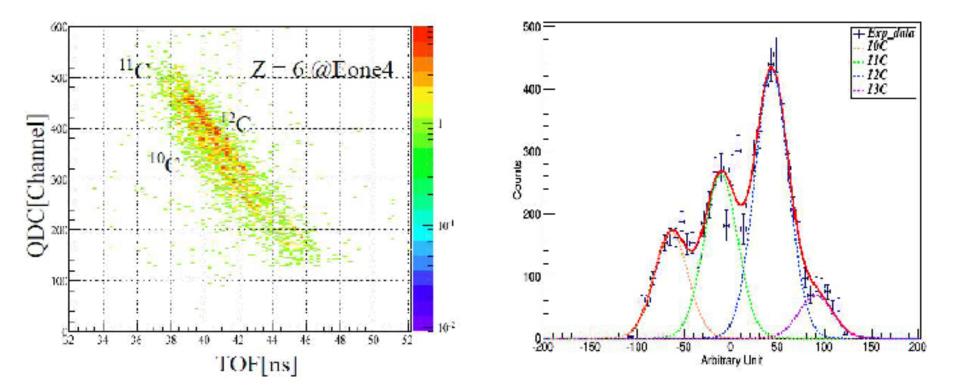

#### **Particle identification**

$$dE/dx \propto z^2/v^2 \quad (1) \qquad dE \propto z^2 TOF^2 \quad (1) - (2)$$

$$TOF \propto 1/v \quad (2) \qquad TOF \propto \frac{1}{c} \frac{m}{z} \quad (2) - (3)$$

图 2.2-2 RCNP EN Course 束流线设置

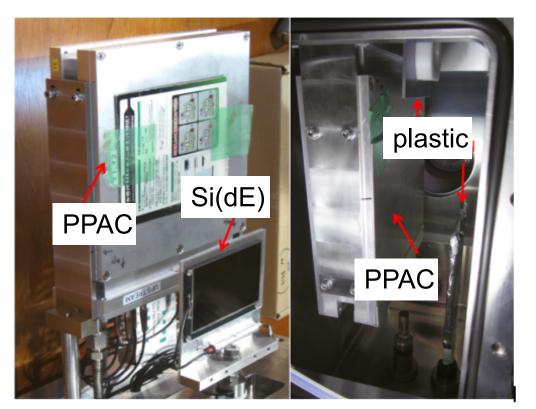

PPAC - xy, tracking Si- dE RF- TOF start plastic- TOF stop

#### 图 2.2-4 F2 PPAC 方硅和塑闪实物照片

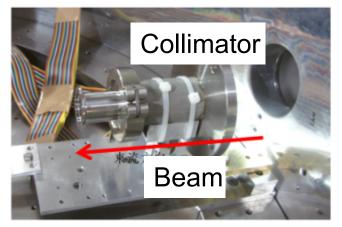

图 2.2-5 靶前准直器以及靶架

Target

| 初级束             | 能量          | 初级靶             | 厚度        |

|-----------------|-------------|-----------------|-----------|

| <sup>16</sup> O | 78.22MeV/u  | <sup>9</sup> Be | 388mg/cm2 |

| D1 磁钢度          | F1 狭缝       | 降能器             | 厚度        |

| 2.066Tm         | $\pm 8 mm$  | Al              | 600um     |

| D2 磁钢度          | F2 狭缝       | 动量接收度           |           |

| 1.9947Tm        | $\pm 20 mm$ | 0.92%           |           |

| 次级束             | 能量          | 强度              | 纯度        |

| 14O             | 59MeV/u     | 7.5kpps         | 5%        |

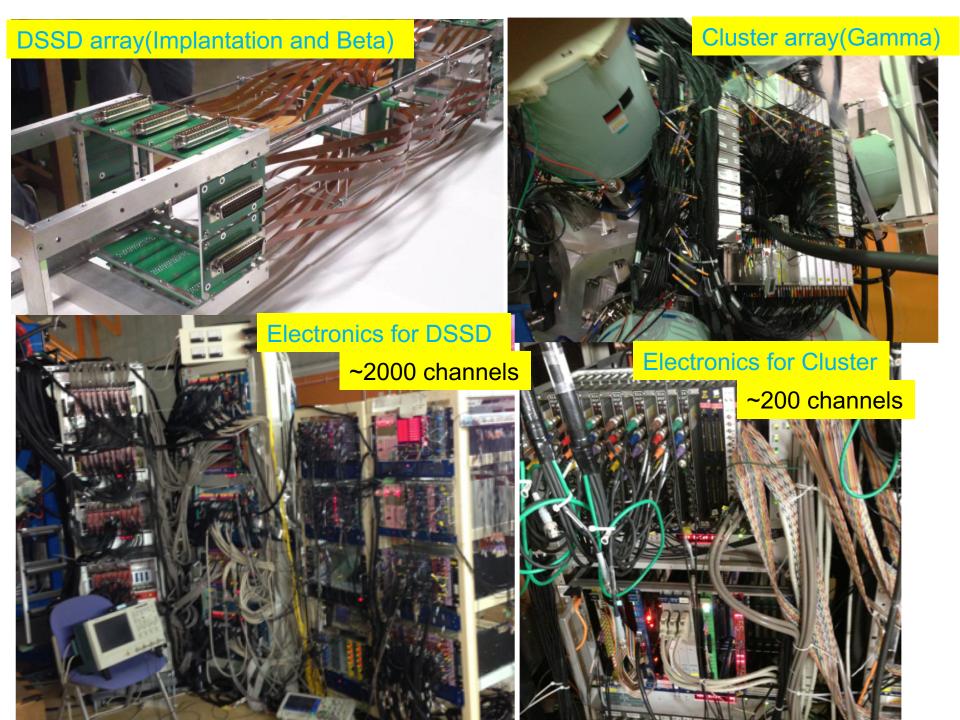

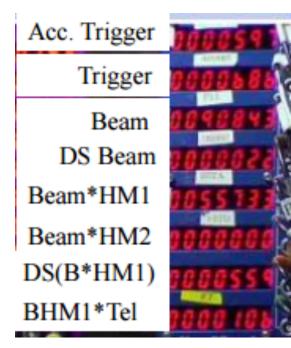

#### DAQ: ~ 600 channels dead time 20% @ 2kHz !

trigger rate ~ beam rate 150kcps need to suppress beam contaminants

Beam intensity: 150kcps ->30kcps

Need more strict trigger from downstream detectors(Physics)

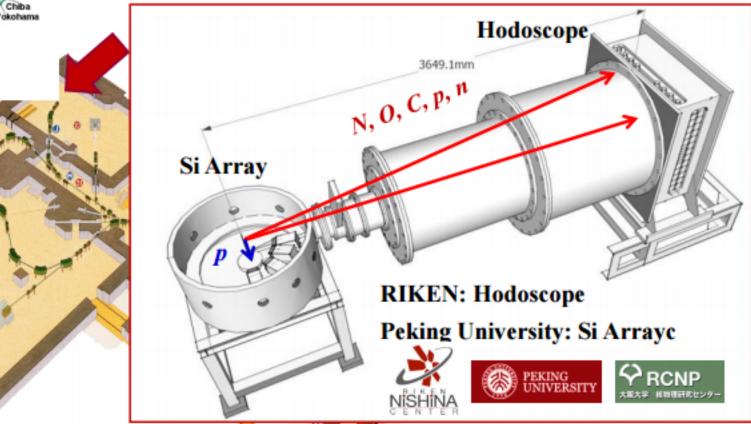

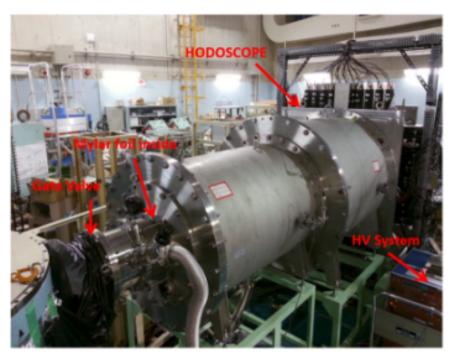

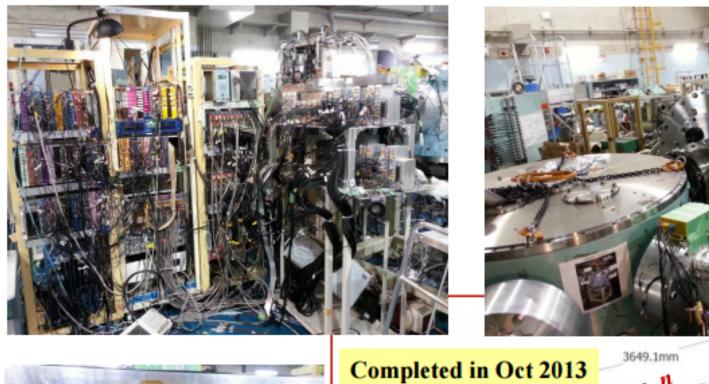

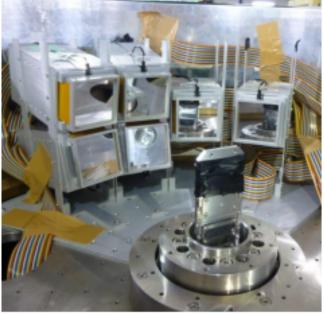

## **Detector array**

$$\sigma = \frac{N_{11C}}{N_{14O}N_s}$$

图 2.2-7 HODOSCOPE 塑料闪烁体阵列的组成[104]

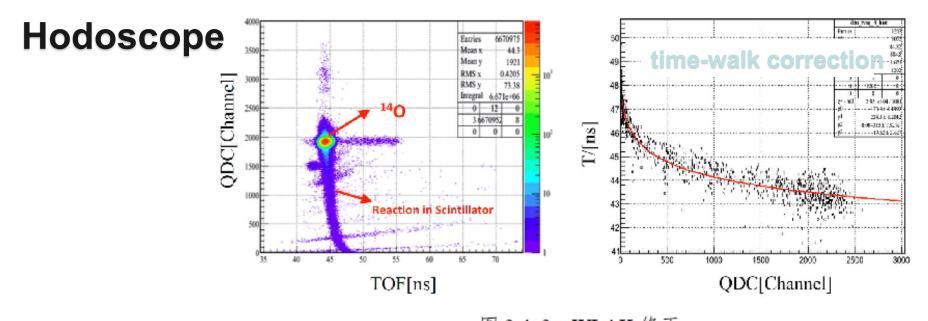

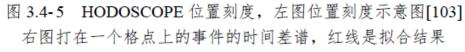

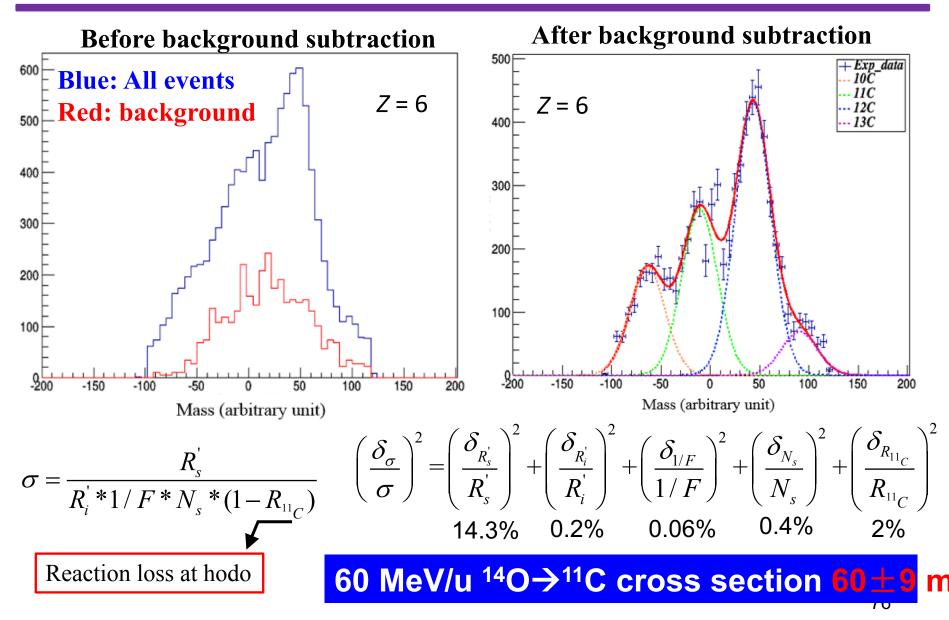

如图所示,HODOSCOPE由42条BC408塑料闪烁体构成,每条闪烁体耦合光电倍增管 (Photomultiplier,PMT)双端读出。整个阵列共三层,第一层(ΔE)厚度5mm,沿水平方 向(X)分成13条;第二层(E1)厚度60mm,沿垂直方向(Y)分成16条;第三层(E2)厚度 也是60mm,沿垂直方向分成13条。

#### $N_{11C}$ particle identification using hodoscope $N_{140}N_{s}$ 5 mm 60 mm Tu <sub>1 m</sub> $dE \propto z^2 / v^2$ $E \propto Av^2$ TOF $\propto 1/v$ TOF Target Ejectiles 1 m $dE \propto z^2 \cdot TOF^2$ $E \propto A / TOF^2$ Plastic detectors: Td<sub>HODO-ΔE</sub> ✓ Poor energy resolution HODO-E ✓ Good timing

✓ Large acceptance

Figure 3.9: A schematic layout of the plastic scintillator hodoscope for detection of the ejectiles.

#### Hodoscope Area

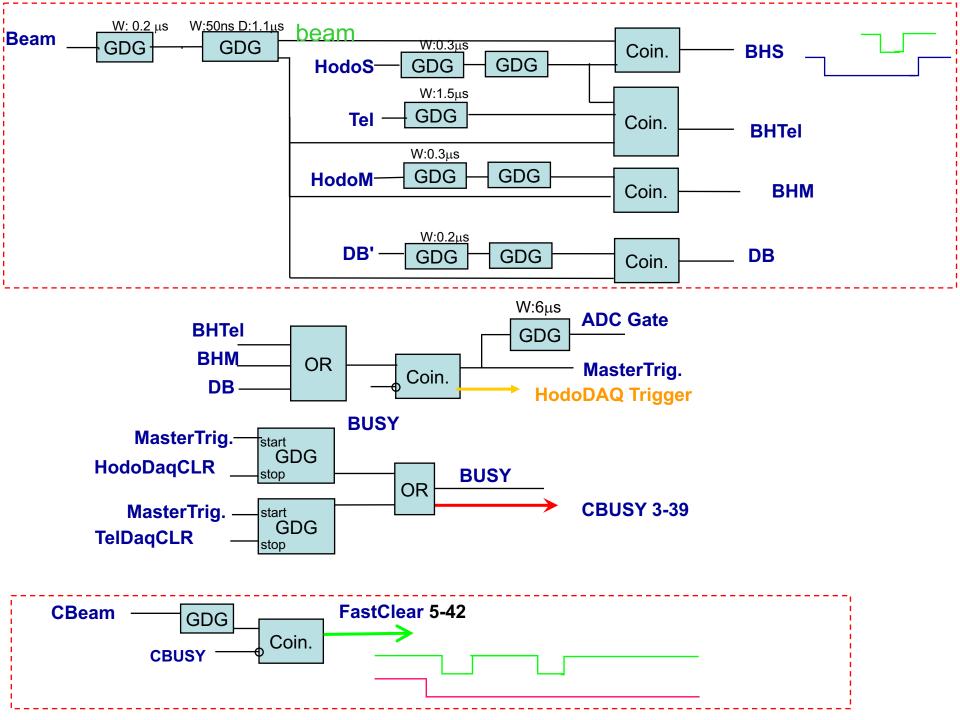

Trigger from Hodo Osilloscope: HodoM: 11C+p : dE & E multiplicity ≥2 counting rate: 30kcps-> 1.5kcps

Main trigger: Beam x HodoM

# **Hodoscope Veto Trigger**

Condition: (DE6 + DE7 + DE8) AND (E1-8 + E1-9)

Beam with intensity >  $10^4 \rightarrow$  Huge Dead Time !  $\rightarrow$  Exclude central area in data-taking

# $dE \propto z^2 \cdot TOF^2$ $E \propto A / TOF^2$

Trigger from Beam line detector: DB: Beam/100~ 300cps - sampling Monitor beam condition during beam time. Telescope array at upstream(back angle)

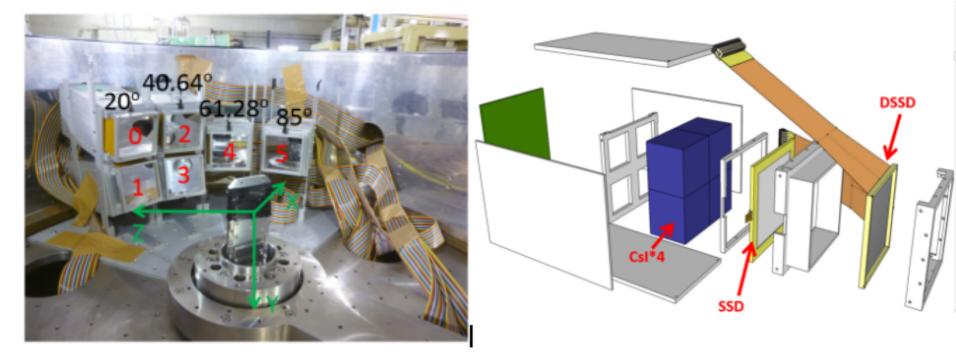

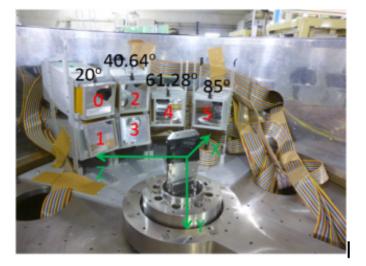

图 2.2-9 靶室内望远镜阵列设置 图中数字为望远镜编号(红色)以及中心和 Z 束流线的夹角(黑色) 图中的绿线标示了坐标系的定义

Trigger from telescope: HodoS x Tele

Visual Scaler-1

- 1. Trigger

- 2. Accepted Trigger

- 3. Beam

- 4. DB

- 5. B x HSingle

- 6. B x HMulti

- 7.140

- 8. B x Hodo x Tel

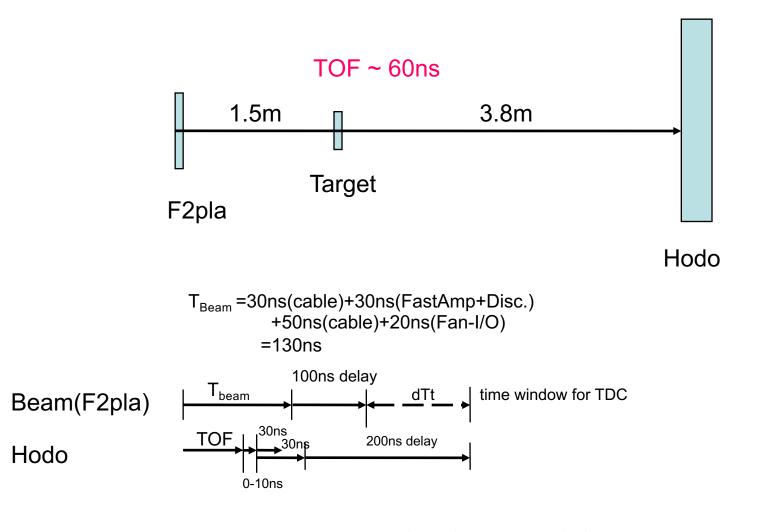

#### V1190(TDC)

- 33. Beam

- 34. DB

- 35. B x HSingle

- 36. B x HMulti

- 37. B x Tel

- 38. Beam x !Busy for deadtime of FCLR

- 64. Reference

To label trigger pattern

$T_{HodoT}: 60+(0-10)+30+200+(30)=300-340ns$   $T_{HodoE}: 60+(0-10)+30+200=300-310ns$   $dTt=T_{HodoT}-(T_{Beam}+100ns)=70-110 ns$  $dTe=T_{Hodoe}-(T_{Beam}+100ns)=70-80 ns, Width: 230ns$

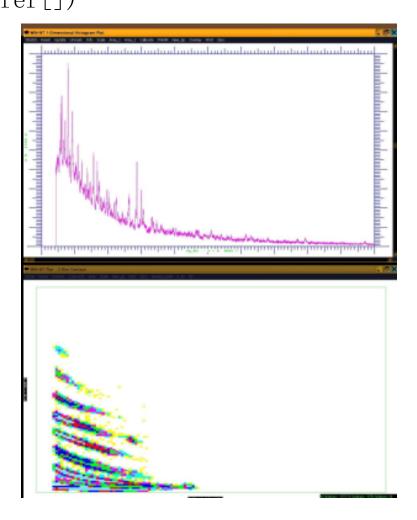

## **Data Analysis - calibration**

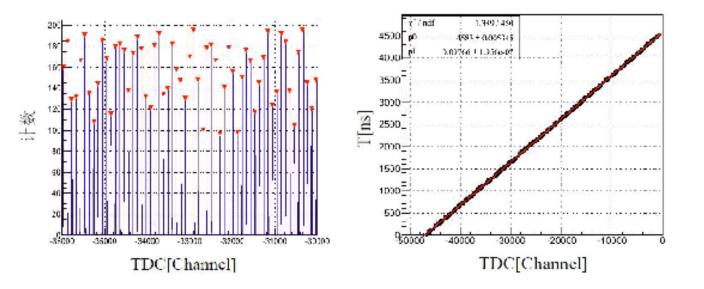

图 3.1-2 V1190 时间刻度

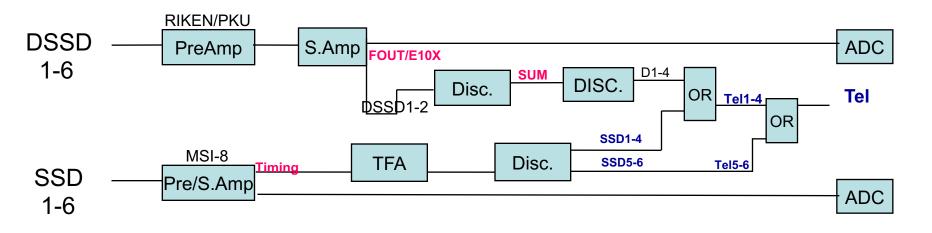

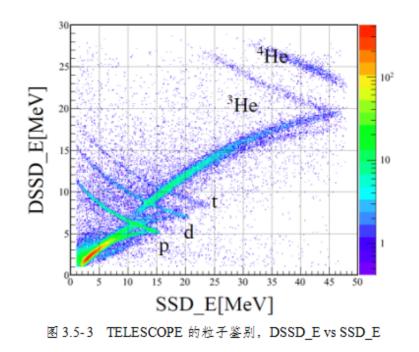

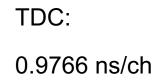

图 3.2-1 DSSD 能量刻度

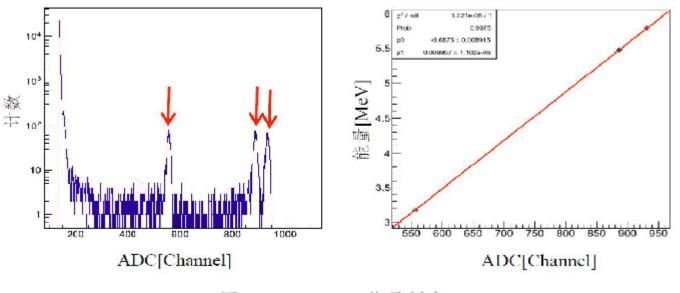

图 3.2-2 DSSD 能量刻度前后, 左图: 道值对硅条编号; 右图: 能量对硅条编号

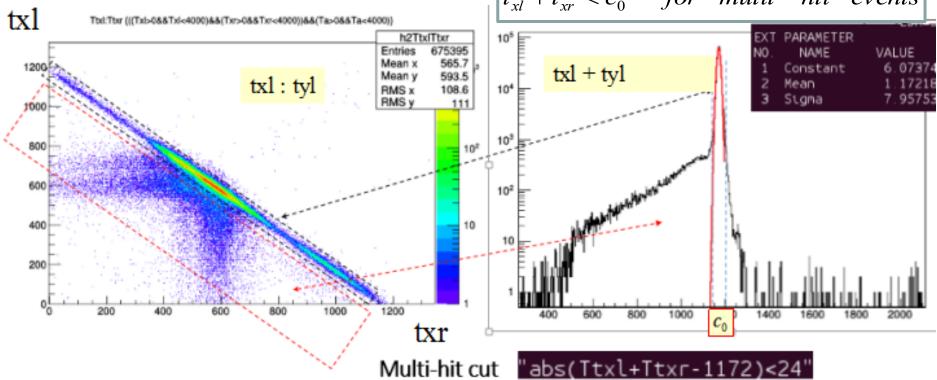

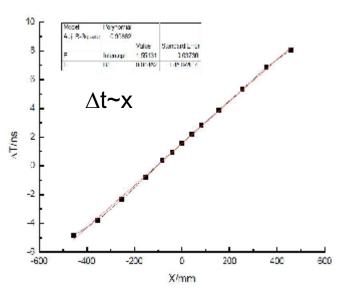

## PPAC beam x,y

$$x = c_x (t_{xl} - t_{xr})$$

$$t_{xl} + t_{xr} = c_0$$

$$t_{xl} = t_{al}; \quad t_{xr} = t_{br}$$

$$t_{xl} = t_{xr} < c_0 \quad for \quad multi - hit \quad events$$

$$t_{xl} + t_{xr} < c_0 \quad for \quad multi - hit \quad events$$

$$t_{xl} + t_{yr} < c_0 \quad for \quad multi - hit \quad events$$

$$t_{xl} + t_{yr} < c_0 \quad for \quad multi - hit \quad events$$

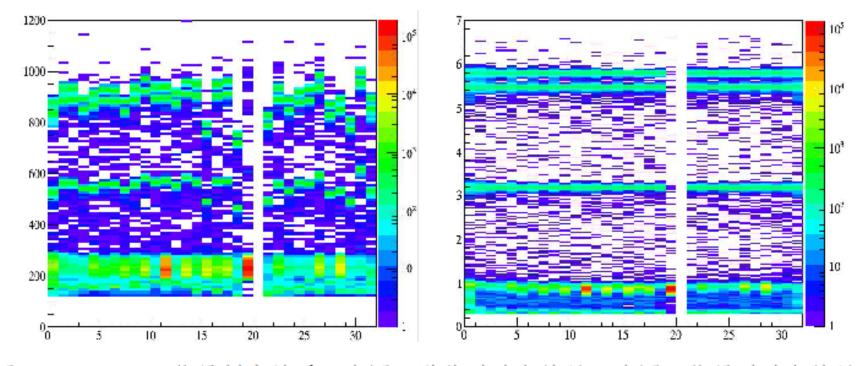

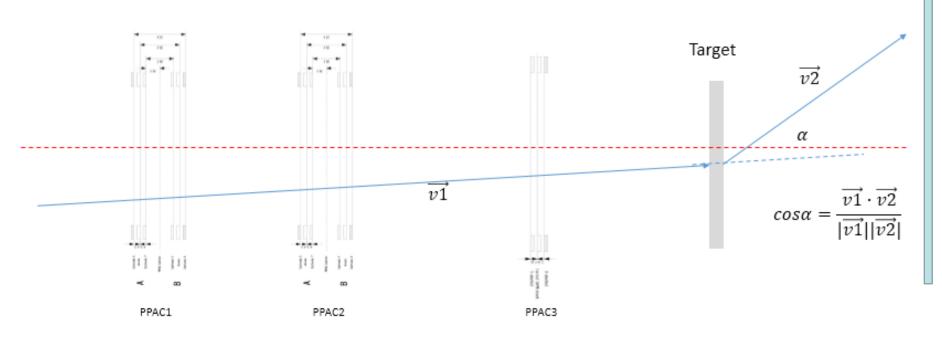

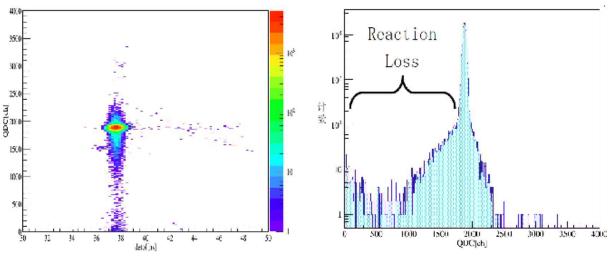

图 3.3-9 靶上束流的位置分布, 左图束流子触发的结果, 右图选择束流和 HODOSCOPE 符合的结果

position calibration

#### Online

\* Beam tuning (position, direction)

#### \* beam profile at target position

#### Offline

reaction dynamics (Scattering angle)

# Particle Tracking

## **Hodoscope-Acceptance**

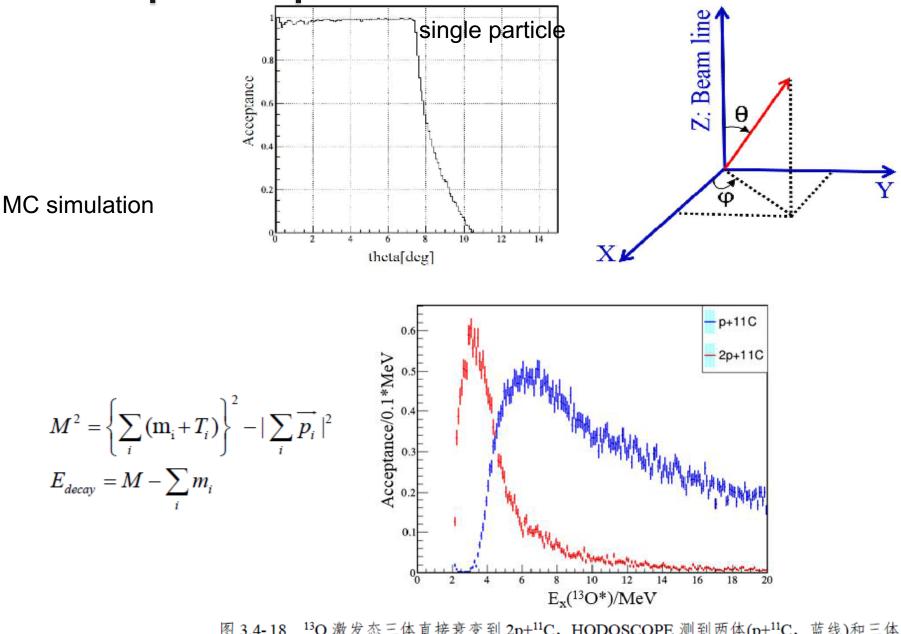

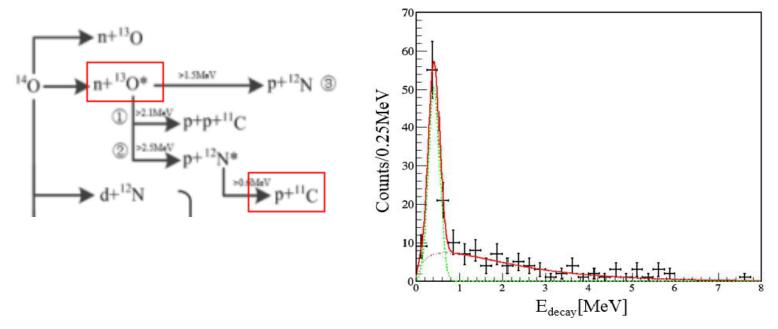

图 3.4-18 <sup>13</sup>O 激发态三体直接衰变到 2p+<sup>11</sup>C, HODOSCOPE 测到两体(p+<sup>11</sup>C, 蓝线)和三体 (2p+<sup>11</sup>C, 红线)的接收度

## **Telescope-Acceptance**

图 2.2-9 靶室内望远镜阵列设置 图中数字为望远镜编号(红色)以及中心和 Z 束流线的夹角(黑色) 图中的绿线标示了坐标系的定义

MC simulation

图 3.5-6 TELESCOPE 每 2 度的接收度

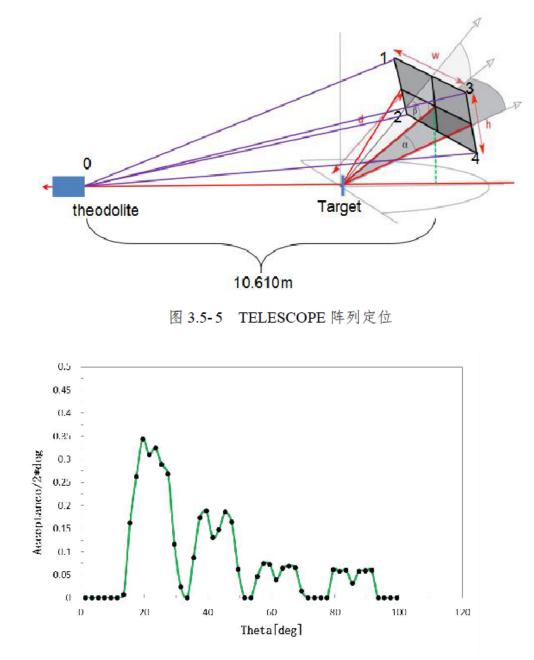

# Reaction in Detector

图 3.6-6 空靶时 <sup>14</sup>O 在 HODOSCOPE 上的反应损失

对 QDC 和 TOF 取其中心值±3sigma,范围之外的认为是在 HODOSCOPE 上的反应损失带来 的。计算得到的反应损失为 10.5%±0.1%。

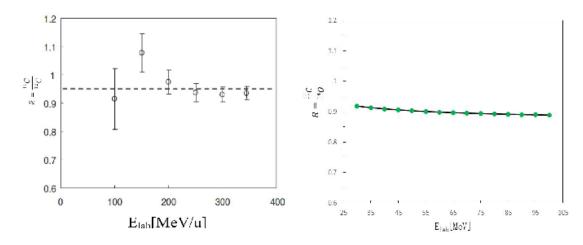

图 3.6-7 反应损失的比值, 左图为 <sup>11</sup>C 和 <sup>12</sup>C 在塑闪中的反应截面的比值, 取自文献[109]; 右图为 Kox 公式计算得到的 <sup>11</sup>C 和 <sup>14</sup>O 在塑闪中反应截面的比值

# **Background estimation with empty target**

$$\sigma = \frac{N_{11C}}{N_{14O}N_s}$$

图 3.6-10 选择<sup>11</sup>C 和质子重建的<sup>12</sup>N 的衰变能谱

<sup>13</sup>O\*主要通过中间态的<sup>12</sup>N\*衰变到<sup>11</sup>C,参考式(3-65)该过程的截面<sup>1</sup>

$$\sigma = \frac{R_{s}'}{R_{i}'*1/F*N_{s}*\varepsilon*(1-R_{11_{C}})*(1-R_{H})}$$

R<sup>'</sup><sub>5</sub>为质子和<sup>11</sup>C 重建得到的<sup>12</sup>N\*(2+)的计数约为 230±25, R<sup>'</sup><sub>i</sub>为入射的<sup>14</sup>O 数目; δ为 HODOSCOPE 仅测到两体的接收度,因为实验中仅观测到少量的三体符合事件,因此可假设<sup>13</sup>O 处在较高的激发态,这样 δ值约为 0.73(参考 3.6.2 节),<sup>11</sup>C 和质子在 HODOSCOPE 上的反应损失 分别取 10%和 7%。由于实验测到的 p+<sup>12</sup>N 的符合事件仅有 p+<sup>11</sup>C 符合事件的十分之一,因此我们 忽略 <sup>13</sup>O 激发态衰变到 <sup>12</sup>N 基态的截面,计算得 <sup>13</sup>O 激发态的上限约为 10±1mb。