### Frontend microelectronics for fast signal acquisition and feature extraction for particle detection and tracking

Nov 16, 2020 Isar Mostafanezhad, Ph.D. Founder and CEO at Nalu Scientific LLC

Work partially funded by US DOE SBIR Grants: DE-SC0015231, DE-SC0017833, DE-SC0020457

# **ABOUT NALU SCIENTIFIC**

#### Fast Growing Startup in Honolulu, Hawai'i

Located at the Manoa Innovation Center Over \$10M in committed funding, 15 staff members Access to advanced design tools Rapid prototyping and testing lab

#### **Scientific Expertise**

HEP/NP particle detection and tracking Radiation detection Readout electronics for Particle Physics

#### **Technical Expertise**

Analog + digital System-on-Chip (SoC) Field Programmable Gate Arrays (FPGA) Complex multi-layer Printed Circuit Board (PCBs)

### WAVEFORM DIGITIZER SoCs FOR PRECISE TIME OF FLIGHT ESTIMATION

#### 1. Front-end Chips:

- Event based digitizer+DSP

- 4-32 channel scope on chip

- 1-15 Gsa/s, 12 bit res.

- Low SWaP-C

- User friendly: FW/SW tools

### 2. Integration:

- SiPM

- PMT

- LAPPD

- Detector arrays

NALU SCIENTIFIC - Approved for public release. Copyright © 2020 Nalu Scientific LLC. All rights reserved. Streaming DAQ workshop, Nov 2020. LAPPD photo courtesy of Incom.

#### 3a. Main application:

- NP/HEP experiments

- Astro particle physics

#### **3b. Other applications:**

- Beam Diagnostics

- Plasma/fusion diagnostics

- Lidar

- PET imaging

## WHERE WE STARTED

A Search for New Physics – The Belle II Experiment

**Tsubuka City** Located 60 mi north of Tokyo High Energy Accelerator Research Facility (KEK) in Tsukuba

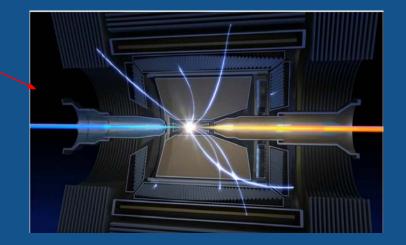

Interaction point inside the electron/positron collider

### **HISTORY - BELLE II**

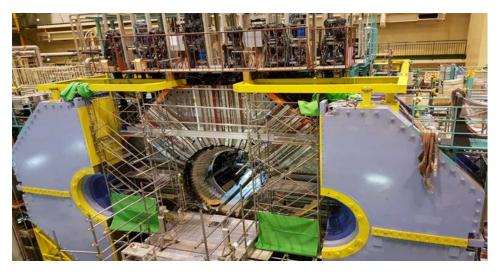

Belle II Upgrade is a 26+ Country, 900 Member Collaboration

### 2015

2018

Nalu Staff designed and implemented front-end electronics and FW for KLM (muon system) and iTOP (Cerenkov-based PID) sub-detectors.

Belle II: e+ e- experiment at 40x luminosity of Belle -> Detector needs to operate at severe beam background

# **HOW DOES NP/HEP EXPERIMENT WORK?**

### 2) Board-stack SiPM 3) Digitizer Cards 5) Data Acquisition 1) Measurement Space: PMTs 4) Digital Control Storage Back-end Front-end Nalu's expertise

LESSON ONE

#### **LESSON TWO**

Next gen Particle Physics electronics need to be:

- Radiation hard

- High performance

- Accommodate long trigger delay

- Low cost, low power

- User friendly

Solution: New System-on-Chip Integrated Circuit

Opportunity: Not many commercial options available

### Proposed Solution: Chip level integration of switched capacitor array (analog) with digital processing.

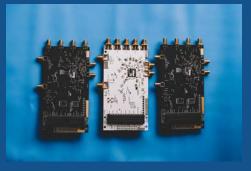

### **Current SoC-ASIC Projects**

| Project  | Sampling<br>Frequency<br>(GHz) | lnput<br>BW<br>(GHz) | Buffer<br>Length<br>(Samples) | Number of<br>Channels | Timing<br>Resolution<br>(ps) | Available<br>Date |

|----------|--------------------------------|----------------------|-------------------------------|-----------------------|------------------------------|-------------------|

| ASoC     | 3-5                            | 0.8                  | 16k                           | 4                     | 35                           | Rev 3 avail       |

| HDSoC    | 1-3                            | 0.6                  | 4k                            | 64                    | 80-120                       | Feb'21            |

| AARDVARC | 8-14                           | 2.5                  | 32k                           | 4                     | 4                            | Rev 3 avail       |

| AODS     | 1-2                            | 1                    | 8k                            | 1-4                   | 100-200                      | Rev 1 avail       |

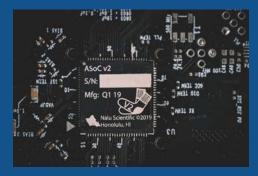

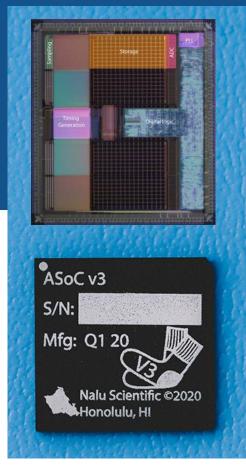

- **ASoC**: Analog to digital converter System-on-Chip ٠

- **HDSoC**: SiPM specialized readout chip with bias and control ٠

- AARDVARC: Variable rate readout chip for fast timing and low deadtime ٠

- **AODS:** Low density digitizer with High Dynamic Range (HDR) option ٠

AARDVARC VI

MFG: Q2 18

AODS v1 BV2

Mfa: O1 2

ASoC v3

S/N Mfa: O1

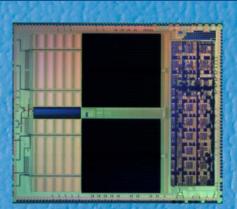

# ASoC V3 DESIGN DETAILS

### Compact, high performance waveform digitizer

- High performance digitizer: 3+ Gsa/s

- Highly integrated

- Commercially available, low cost, patented design

- 5mm x 5mm die size

| Parameter               | Spec                          |

|-------------------------|-------------------------------|

| Sample rate             | 2.4-3.6GSa/s                  |

| Number of Channels      | 4                             |

| Sampling Depth          | 16kSa/channel                 |

| Signal Range            | 0-2.5V                        |

| Number of ADC bits      | 12 bits                       |

| Supply Voltage          | 2.5V                          |

| RMS noise               | ~1.5 mV                       |

| Digital Clock frequency | 25MHz                         |

| Timing resolution       | <25ps (see below for details) |

| Power                   | 120mW/channel                 |

| Analog Bandwidth        | 850MHz                        |

| Serial interface        | Up to 500 Mb/s***             |

- Calibration memory access

- PLL on chip

- Isolated analog/digital voltage rings

- Serial interface

- Self triggering

- Completed DOE Phase II SBIR

- Eval cards avail

- Custom boards under dev

### IEEE NSS 2020

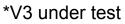

# **ASoC V2\* MEASUREMENTS**

SiPM waveform readout

10

NALU SCIENTIFIC - Approved for public release. Copyright © 2020 Nalu Scientific LLC. All rights reserved. Streaming DAQ workshop, Nov 2020.

~600ns separation

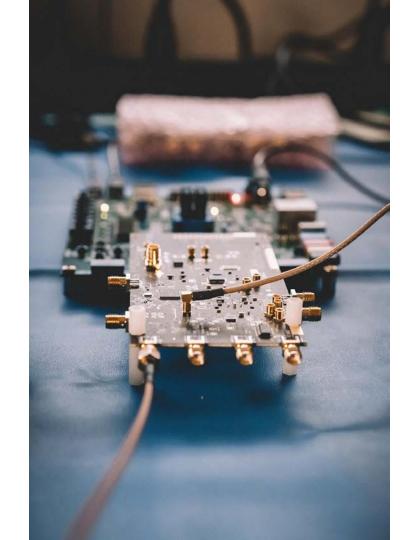

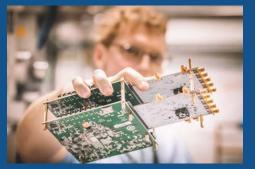

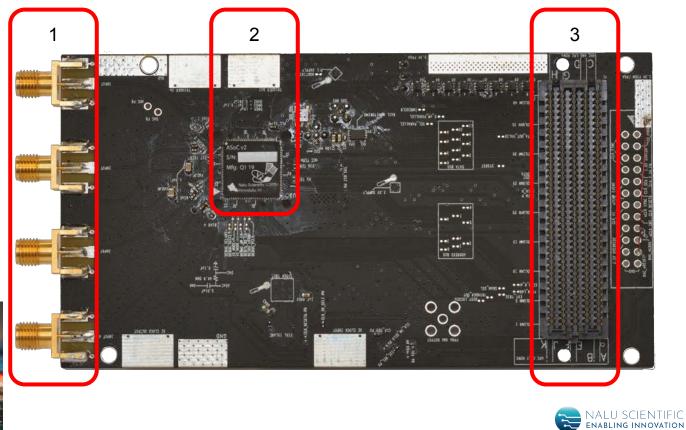

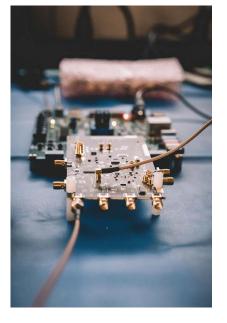

## **ASoC Eval Card**

- 1. SMA inputs

- 2. ASoC chip

- 3. FMC for FPGA card

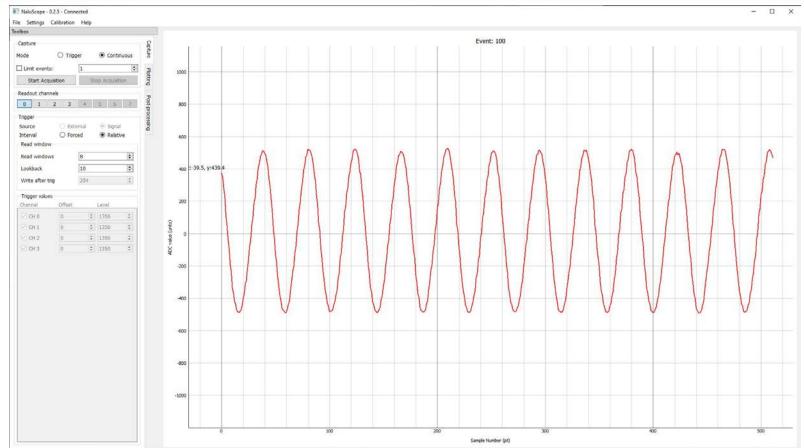

## NaluScope Common Software and GUI

## AARDVARC V3 DESIGN DETAILS

### Compact, high performance waveform digitizer

- High performance digitizer: 10+ Gsa/s

- Highly integrated

- Commercially available, low cost, patented design

- 5mm x 5mm die size

| Parameter       | Spec             |

|-----------------|------------------|

| Sampling Rate   | 10-14 GSa/s      |

| ABW             | > 1GHz           |

| Depth           | 32k Sa           |

| Trigger Buffer  | ~3 us*           |

| Deadtime        | O**              |

| Channels        | 4                |

| Supply/Range    | 1.2V/0.3-0.9V    |

| ADC bits        | 12               |

| Timing accuracy | <5ps (@13 GSa/s) |

| Technology      | 130 nm CMOS      |

| Power           | 80mW/ch          |

- On chip calibration

- On chip PLL

- On chip feature extraction

- Isolated analog/digital voltage rings

- Serial interface

- Funded DOE Phase IIA SBIR

### IEEE NSS 2020

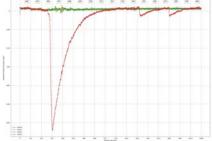

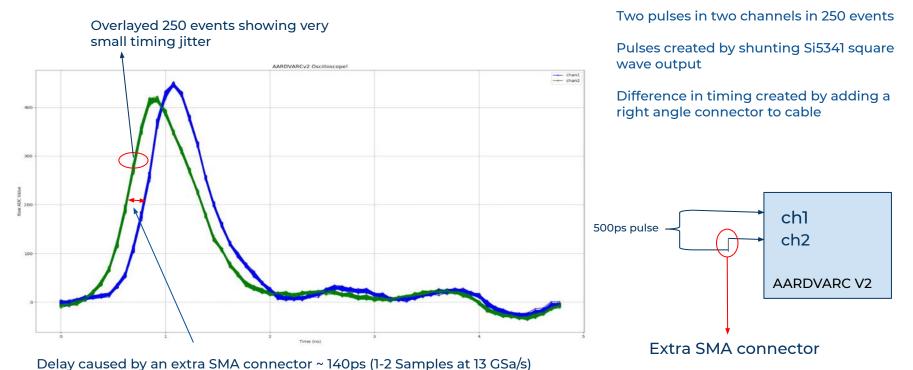

## AARDVARC V2\*

Note: the pulse gen is synced with ASIC sampling clock.

#### \*V3 is under test with expected similar performance

Jitter measured at ~1-2ps

# HDSoC VI DESIGN DETAILS

High density waveform digitizer with dead-timeless readout

- High Density: 64 channels

- Highly integrated, SiPM gain + bias

- Commercially available, low cost CMOS

| Parameter       | Spec        |

|-----------------|-------------|

| Sampling Rate   | 1-2 GSa/s   |

| ABW             | > 600MHz    |

| Depth           | 2k Sa       |

| Trigger Buffer  | ~3 us*      |

| Deadtime        | 0**         |

| Channels        | 64          |

| Supply/Range    | 2.5         |

| ADC bits        | 12          |

| Timing accuracy | 80-120ps    |

| Technology      | 250 nm CMOS |

| Power           | TBD         |

- On chip calibration

- Serial interface

- On chip Feature extraction

- Virtually dead-timeless

- Phase I SBIR Project

\*\*Up to 240 KHz / ch with single serial link using on-chip self trigger and feature extraction. Up to 400 kHz / ch with additional serial links.

## **Dead-timeless operation**

#### • Multi-bank switched capacitor array:

- Older versions of chips (ASoC, AARDVARC)

- Long internal analog memory (storage)

- Capable of self triggering

- Suitable for long trigger delays (3-5 us)

- Large die size

- ASoC V3 may be able to readout up to ~100 kHz of input rate without deadtime (estimated).

#### • Virtual analog memory:

- New lines of chips (HDSoC)

- Unlimited virtual depth (up to a certain rate)

- Small die size, lower power

- Dead-timeless up to a certain rate, designed with self-triggering in mind

- Suitable for streaming mode readout

- Feature extraction and on-chip data reduction

- Estimated 240-400 kHz rate handling

## How can Nalu's chips contribute?

| Project  | Sampling<br>Frequenc<br>y (GHz) | Buffer<br>Length<br>(Samples) | Number<br>of<br>Channels | Timing<br>Res. (ps) | Rate handling | TRL  | Suitable for                                                    | Potential EIC<br>Sub Detectors |

|----------|---------------------------------|-------------------------------|--------------------------|---------------------|---------------|------|-----------------------------------------------------------------|--------------------------------|

| ASoC     | 3-5                             | 16k                           | 4                        | 35                  | ~100kHz       | High | Low density, precision<br>timing, flexible board<br>integration |                                |

| HDSoC    | 1-3                             | 4k                            | 64                       | 80-120              | ~240, 400 kHz | rev1 | High density SiPM, MA-PMT                                       | mRICH, dRICH                   |

| AARDVARC | 8-14                            | 32k                           | 4                        | 4                   | ~125kHz       | Med  | Precision timing, low density                                   |                                |

| AODS     | 1-2                             | 8k                            | 1-4                      | 100-200             |               | Med  |                                                                 |                                |

- Significant investment from DOE SBIR program

- All chips designed with commercial grade design tools can be readily commercialized

- Nalu staff already involved with EIC-PID readout, white papers, etc

- Ongoing discussion with system integrators to connect chips to DAQs

- High levels of integration on chip clock, calibration, memory experiment in mind.

- Previous versions of similar technology have been used in experiments (Belle II)

# Summary

- Nalu Scientific portfolio of FE/digitizer electronics

- Specialized for NP/HEP experiment readout

- High integration (clock, memory, calibration)

- Packaged chips and eval cards available

- Additional testing under way including irradiation

- Nalu staff have been involved in:

- Previous NP/HEP electronics/FW development

- Advanced mixed signal ASIC design

- A variety of detector electronics design

- Funding:

- <u>SBIRs:</u> costly chip development

- <u>Trade studies:</u> initial assessment

- <u>Custom design contracts:</u> Implementing new packaging and PCB designs

- Next steps:

- Continue chip+PCB development

- Continue engagement with experiments in order to tailor the designs to evolving experiment needs

ASoC v3

Mfg: Q1 20

Nalu Scientific ©2020

Honolulu, HI

S/N:

• Eval boards available for testing

US Department of Energy Office of Science

### Hawaii Technology Development Corporation (HTDC)

### University of Hawai'i at Manoa Department of Physics